文章目录

- 一、RGMII接口介绍

- 二、MAC和PHY

- 1.关系

- 2.MAC和PHY的交互

- 3.MAC为什么要配置PHY

- 4.如何配置

- (1)原理

- (2)PHY地址的确定

- (3)寄存器地址及配置数据

- 三、88E1111中PHY的时序

- 1.接收端时序

- (1)非延时模式

- (2)延时模式

- 2.发送端时序

- (1)非延时模式

- (2)延时模式

- 四、Xinlinx中处理RGMII接口的数据

- 1.IDDR

- (1)作用及接口说明

- (2)三种工作模式

- (3)数据处理过程

- 2.ODDR

- (1)作用及接口说明

- (2)工作模式

- (3)数据处理过程

- 3.IDELAYE2

一、RGMII接口介绍

以太网的通信离不开物理层 PHY 芯片的支持,以太网 MAC 和 PHY 之间有一个接口,常用的接口有MII、 RMII、 GMII、 RGMII 等。

RGMII接口如下:

| 信号名称 | 位宽 | 方向 | 描述 |

|---|---|---|---|

| TXC | 1 | OUT | 发送时钟信号,10/100/1000Mbps 模式频率分别为 2.5M/25M/125MHz |

| TD | 4 | OUT | 发送数据信号 |

| TX_CTL | 1 | OUT | 发送数据控制信号,上升沿时为数据有效信号,下降沿时为数据有效信号/错误信号 |

| RXC | 1 | IN | 接收时钟信号,10/100/1000Mbps 模式频率分别为 2.5M/25M/125MHz |

| RD | 4 | IN | 接收数据信号 |

| RX_CTL | 1 | IN | 接收控制信号,上升沿时为数据有效信号,下降沿时为数据有效信号/错误信号 |

RGMII 是 GMII 的简化版,数据位宽为 4 位

- 在 1000Mbps 传输速率下,时钟频率为 125Mhz,在时钟的上下沿同时采样数据

- 在 100Mbps传输速率下,时钟频率为25MHz,为单个时钟沿采样

- 在 10Mbps传输速率下,时钟频率为2.5MHz,为单个时钟沿采样

二、MAC和PHY

1.关系

MAC(介质访问控制)和PHY(物理层)是网络通信中两个互补的组件,它们共同工作以实现数据在网络中的传输。它们在OSI模型中分别对应不同的层次:

- MAC层:

- MAC层位于OSI模型的数据链路层的上层,负责控制对共享介质(如以太网)的访问。

- 它处理帧的封装和拆封,包括添加MAC头部和尾部,以及处理错误检测和控制机制。

- MAC层还负责多路访问和冲突解决,例如在以太网中通过CSMA/CD(Carrier Sense Multiple Access with Collision Detection)协议。

- MAC地址,也称为物理地址或硬件地址,是网络设备在网络中的唯一标识,由MAC层管理。

- PHY层:

- PHY层位于OSI模型的数据链路层的下层,直接与传输媒介(如电缆、光纤、无线电波等)交互。

- 它负责通过物理媒介传输和接收比特流,包括信号编码、调制解调、信号放大和时钟恢复。

- PHY层定义了电气特性,如电压水平、阻抗匹配、数据速率、最大传输距离等。

- 它还可能包括介质相关接口(MDI)和物理编码子层(PCS),用于进一步处理数据以适应特定的传输媒介。

2.MAC和PHY的交互

- MAC层生成要传输的数据帧,并将它们发送到PHY层。

- PHY层接收来自MAC层的帧,将其转换为适合在物理媒介上传输的信号,并发送出去。

- 当PHY层接收到来自物理媒介的信号时,它将信号转换回帧,并将其发送到MAC层。

- PHY层还负责与链路伙伴(如交换机、路由器或另一台主机)的PHY层进行协商,以确定最佳的传输参数,如速率、双工模式等。

3.MAC为什么要配置PHY

MAC(Media Access Control,介质访问控制)是网络接口的一部分,负责管理和控制数据在物理媒介上的传输。PHY(Physical Layer,物理层)是网络接口的另一个重要组成部分,它负责通过物理媒介(如电缆、光纤等)传输和接收实际的比特流。MAC和PHY共同工作以实现网络通信。

MAC需要配置PHY的原因包括:

- 物理层参数:不同的物理媒介有不同的特性和要求,例如信号速率、双工模式(全双工或半双工)、流控制等。配置PHY可以确保数据传输符合所使用的物理媒介的特性。

- 接口标准化:配置PHY有助于确保网络设备遵循特定的标准(如以太网、Wi-Fi等),这些标准定义了物理层的操作方式。

- 自动协商:许多网络设备使用自动协商来确定最佳的传输速率和模式。通过配置PHY,可以实现速率和双工模式的自动协商。

- 信号完整性:PHY负责信号的生成和接收,配置PHY可以优化信号的完整性,减少噪声和干扰,提高数据传输的可靠性。

- 错误检测和纠正:某些PHY支持错误检测和纠正机制,配置PHY可以启用这些机制,从而提高数据传输的准确性。

- 电源管理:PHY可能包含电源管理功能,如节能模式,配置PHY可以优化设备的能耗。

- 远程监控:配置PHY还可以允许远程监控物理层的状态,包括链路状态、速率、错误统计等。

- 兼容性:不同的网络设备可能使用不同的PHY芯片或技术,配置PHY确保MAC层与PHY层兼容,从而实现无缝通信。

- 高级功能:一些高级网络功能,如优先级队列、虚拟局域网(VLAN)标记等,可能需要PHY支持特定的硬件功能。

- 故障诊断:配置PHY有助于故障诊断,因为它可以提供链路状态和错误信息,帮助网络管理员识别和解决问题。

总之,MAC配置PHY是为了确保网络接口能够在物理层上正确、高效、可靠地传输数据,并与网络中的其他设备兼容。

4.如何配置

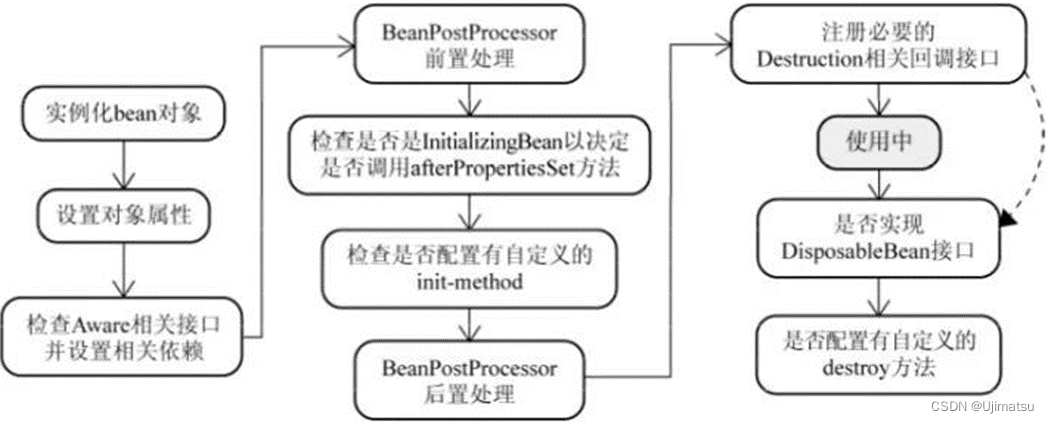

(1)原理

MDIO(Management Data Input/Output,管理数据输入输出) 是一种简单的双线串行接口。该总线由 IEEE 通过以太网标准 IEEE 802.3 的若干条款加以定义。可收集的信息包括链接状态、传输速度与选择、断电、低功率休眠状态、TX\RX 模式选择、自动协商控制、环回模式控制等。

其包含 2 个引脚:MDC 和 MDIO。MDC 管理数据的时钟输入,最高速率 8.3 MHz;MDIO 管理数据的输入输出,数据是与 MDC 时钟同步的。

通过FPGA向PHY操作的数据格式如下:

| Preamble | Start | Opcode | PHY address | Register address | Turn-around | Register data | Idle |

| 32bit 1 | 01 | Read:10 Write:01 | 5bit | 5bit | Read:z0 Write:10 | 16 bit | z |

- Preamble:32bits的前导码,全1。

- Start:2bit的开始位

- PHY adress:5bits的PHY地址,

- Register adress:5bits的寄存器地址

- Turn-around:2bits的TA,在读命令中,MDIO在此时由MAC驱动改为PHY驱动,并等待一个时钟周期准备发送数据。在写命令中,不需要MDIO方向发生变化,则只是等待两个时钟周期准备写入数据。

- Register data:16bits数据,在读命令中,PHY芯片将读到的对应PHYAD的REGAD寄存器的数据写到Data中,在写命令中,MAC将要写入对应PHYAD的REGAD寄存器的值写入Data中。

- Idle:空闲状态,此时MDIO无源驱动,处高阻状态。

下面给出读写两种情况下的MDIO和MDC的时序图:

①写操作

②读操作

时序图中与手册规定的不一样,并没有采用32bit的前导码。

对寄存器进行配置或读取时,需要按照上述的数据格式,通过MDIO一比特一比特的传输到PHY中。

(2)PHY地址的确定

要确定PHY芯片的地址,需要查看PHY芯片手册以及板卡原理图。

①PHY芯片手册决定了控制信号和PHY地址的对应关系

②板卡原理图决定了PHY地址的控制信号所连接的对象

接下来以手上的一个325t的办卡进行举例:

先看一下PHY芯片手册:

可以看到各个控制信号对应的管脚信息,并且说明了CONFIG[0]决定了PHY地址的低3位,CONFIG[1]决定了PHY地址的高两位。

查看板卡原理图:

我们可以发现,CONFIG[0]连接着PHYA_LED_RX,CONFIG[1]连接着PHYA_LED_LINK1000。我们查看88E1111的手册,如下:

可知LED_RX对应010,LED_LINK1000对应100,因此CONFIG[0]对应的PHY地址低3位为010,CONFIG[1]对应的PHY地址高2位为00,因此PHY地址为00010。

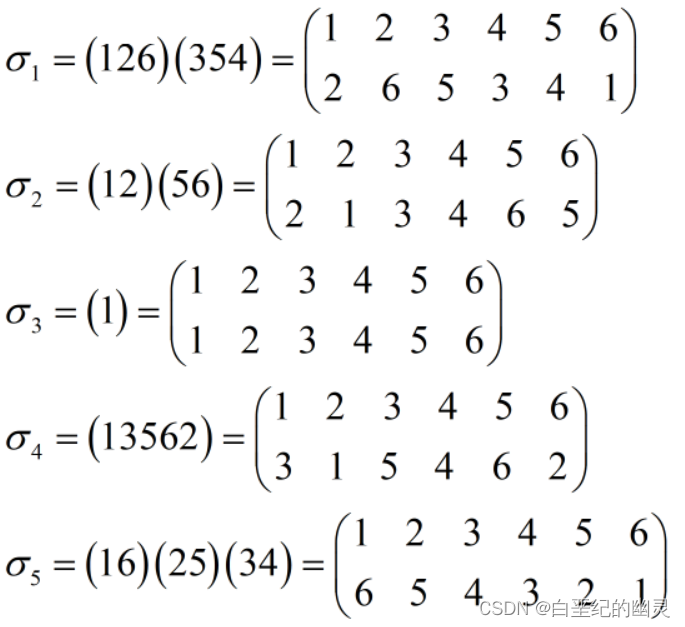

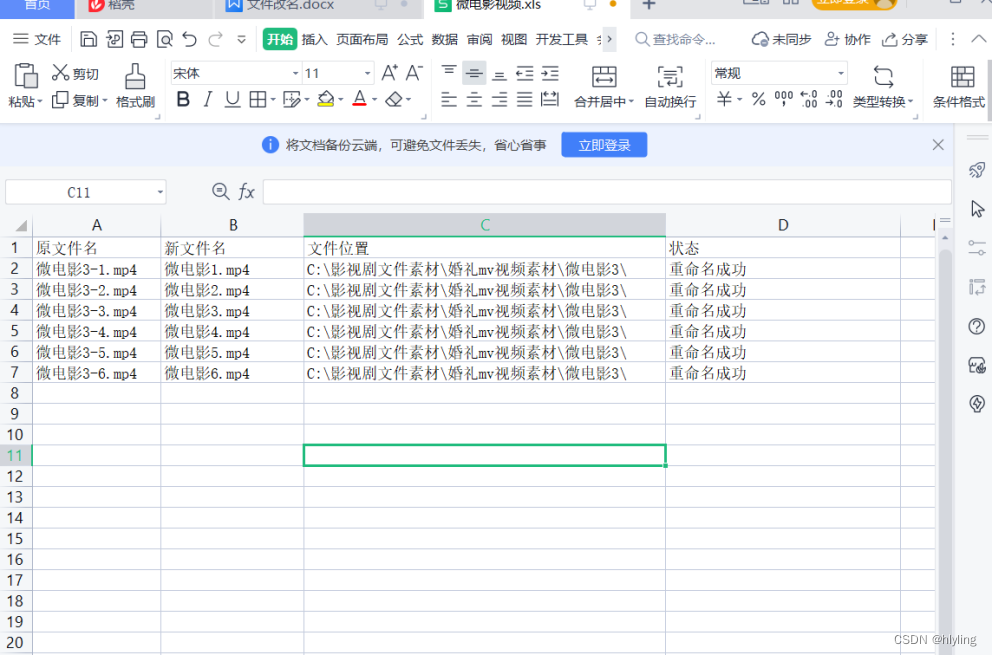

(3)寄存器地址及配置数据

我们以控制寄存器0举例,为了配置千百兆模式需要对控制寄存器0的bit6和bit13进行配置。

因此寄存器地址为0,将寄存器数据的bit13、bit6按照需要的模式进行配置,其他功能可对对应bit配置相应数据。

三、88E1111中PHY的时序

1.接收端时序

接收端信号时序如下图所示:

一般的PHY芯片包含两种RGMII接收端口时序模式,分别为延时模式和非延时模式,通过控制寄存器20的bit7实现,当其为1时是延时模式,为0时是非延时模式,默认情况下是非延时模式。

(1)非延时模式

非延时模式下,接收时钟与接收数据信号边沿对其。

(2)延时模式

延时模式下时钟信号RX_CLK的边沿处于数据和控制信号的中心位置,此时的RX_CLK相对于数据和控制信号有2ns的延迟(2ns是因为在1000M速率下时钟为125MHz,一个时钟周期为8ns,一个数据的有效时间为4ns)

2.发送端时序

发送端信号时序如下图所示:

一般的PHY芯片包含两种RGMII发送端口时序模式,分别为延时模式和非延时模式,通过控制寄存器20的bit1实现,当其为1时是延时模式,为0时是非延时模式,默认情况下是非延时模式。

(1)非延时模式

非延时模式下时序图如上图所示,可知在此模式下时钟信号TX_CLK的边沿处于数据和控制信号的中心位置,此时的TX_CLK相对于数据和控制信号有2ns的延迟(2ns是因为在1000M速率下时钟为125MHz,一个时钟周期为8ns,一个数据的有效时间为4ns)。

(2)延时模式

延时模式下,要求发送时钟和数据及控制信号的边沿对齐。

四、Xinlinx中处理RGMII接口的数据

1.IDDR

(1)作用及接口说明

IDDR(Input Double Data Rate)原语是Xilinx FPGA中用于处理双数据速率信号的一种原语,它将输入的双被速率数据转换为单倍速率信号。

| 信号名称 | 位宽 | 方向 | 描述 |

|---|---|---|---|

| CE | 1 | IN | 时钟使能信号 |

| C | 1 | IN | 时钟信号 |

| S | 1 | IN | 置位信号 |

| R | 1 | IN | 复位信号 |

| D | 1 | IN | 输入的双倍速率的数据,即D在时钟的上升沿和下降沿都会发生切换,一个时钟周期发送2bit数据 |

| Q1 | 1 | OUT | 单倍速率的输出数据 |

| Q2 | 1 | OUT | 单倍速率的输出数据 |

(2)三种工作模式

它支持三种不同的工作模式,这些模式决定了IDDR如何对输入数据进行采样以及输出数据的生成方式:

-

OPPOSITE_EDGE模式:在这种模式下,IDDR将在时钟的上升沿和下降沿都进行数据采样。这意味着每个时钟周期的上升沿和下降沿都会有数据变化,实现双沿传输。输出Q1在时钟的每个上升沿提供在该上升沿采集到的数据,而Q2在时钟的每个下降沿提供在该下降沿采集到的数据。

-

SAME_EDGE模式:此模式与OPPOSITE_EDGE模式的输入信号时序一致,但区别在于Q1和Q2都只在时钟的上升沿输出数据。在第一个上升沿,Q1输出在该上升沿采集到的数据,而在随后的下降沿,Q2采集数据,并在第二个上升沿,Q1输出第二个上升沿采集的数据,Q2输出第一个下降沿采集的数据。

-

SAME_EDGE_PIPELINED模式:这是最常用的数据采集模式。与SAME_EDGE模式类似,但Q1的输出数据会延迟一个时钟周期,使得Q1和Q2的第一个数据至最后一个数据进行对齐,这样方便后续逻辑的操作,但代价是Q1的输出数据会有一个时钟周期的延迟

(3)数据处理过程

2.ODDR

(1)作用及接口说明

它的功能是将单倍速率的数据转化成双倍速率的数据。

| 信号名称 | 位宽 | 方向 | 描述 |

|---|---|---|---|

| C | 1 | IN | 时钟信号 |

| CE | 1 | IN | 时钟使能信号 |

| S | 1 | IN | 置位信号 |

| R | 1 | IN | 复位信号 |

| D1 | 1 | IN | 单倍速率的输入数据 |

| D2 | 1 | IN | 单倍速率的输入数据 |

| Q | 1 | OUT | 输出的双倍速率的数据,即Q在时钟的上升沿和下降沿都会发生切换 |

(2)工作模式

ODDR支持两种不同的工作模式:

-

OPPOSITE_EDGE模式:在此模式下,ODDR在时钟的上升沿采集D1输入信号,并在上升沿将采集到的信号输出;在时钟的下降沿采集D2输入信号,并在下降沿将采集到的信号输出。这种模式使用起来相对复杂,因为FPGA内部需要在时钟的上升沿给D1赋值,在时钟的下降沿给D2赋值,一般不常使用1820。

-

SAME_EDGE模式:此模式下,ODDR在时钟的上升沿同时采集D1和D2的数据,然后在时钟的上升沿输出采集的D1数据,在下降沿输出采集的D2数据。这种方式实现起来比较简单,属于常用的模式20。

(3)数据处理过程

3.IDELAYE2

用于将数据延迟一段时间。

例化:

(* IODELAY_GROUP = <iodelay_group_name> *) // Specifies group name for associated

IDELAYs/ODELAYs and IDELAYCTRL

IDELAYE2 #(

.CINVCTRL_SEL("FALSE"), // Enable dynamic clock inversion (FALSE, TRUE)

.DELAY_SRC("IDATAIN"), // Delay input (IDATAIN, DATAIN)

.HIGH_PERFORMANCE_MODE("FALSE"), // Reduced jitter ("TRUE"), Reduced power ("FALSE")

.IDELAY_TYPE("FIXED"), // FIXED, VARIABLE, VAR_LOAD, VAR_LOAD_PIPE

.IDELAY_VALUE(0), // Input delay tap setting (0-31)

.PIPE_SEL("FALSE"), // Select pipelined mode, FALSE, TRUE

.REFCLK_FREQUENCY(200.0), // IDELAYCTRL clock input frequency in MHz (190.0-210.0,

290.0-310.0).

.SIGNAL_PATTERN("DATA") // DATA, CLOCK input signal

)

IDELAYE2_inst (

.CNTVALUEOUT(CNTVALUEOUT), // 5-bit output: Counter value output

.DATAOUT(DATAOUT), // 1-bit output: Delayed data output

.C(C), // 1-bit input: Clock input

.CE(CE), // 1-bit input: Active high enable increment/decrement input

.CINVCTRL(CINVCTRL), // 1-bit input: Dynamic clock inversion input

.CNTVALUEIN(CNTVALUEIN), // 5-bit input: Counter value input

.DATAIN(DATAIN), // 1-bit input: Internal delay data input

.IDATAIN(IDATAIN), // 1-bit input: Data input from the I/O

.INC(INC), // 1-bit input: Increment / Decrement tap delay input

.LD(LD), // 1-bit input: Load IDELAY_VALUE input

.LDPIPEEN(LDPIPEEN), // 1-bit input: Enable PIPELINE register to load data input

.REGRST(REGRST) // 1-bit input: Active-high reset tap-delay input

);

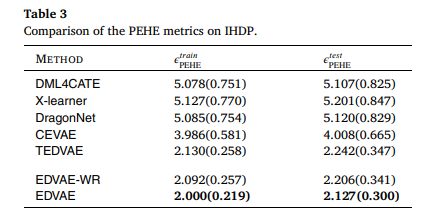

延时值如下:

延时值 = 600 p s + t a p ∗ r e s o l u t i o n r e s o l u t i o n = 1 64 ∗ f ( u s ) 延时值=600ps+tap*resolution\\ resolution=\frac{1}{64*f} (us) 延时值=600ps+tap∗resolutionresolution=64∗f1(us)

其中f频率的单位为MHz,tap值为CNTVALUEIN的值。

详细可参考下面文章:

Xilinx IDELAYE2应用笔记及仿真实操-CSDN博客