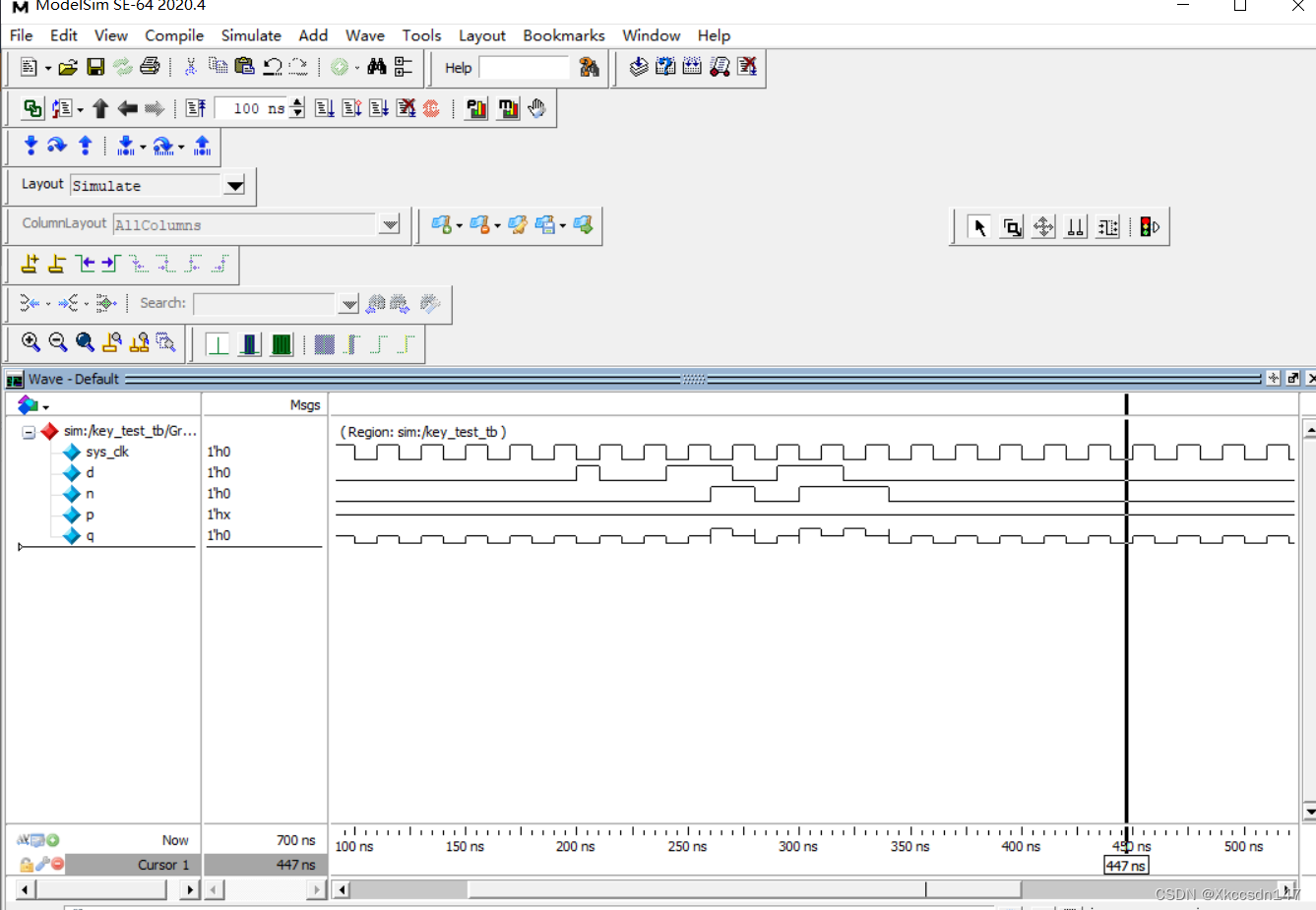

一、问题

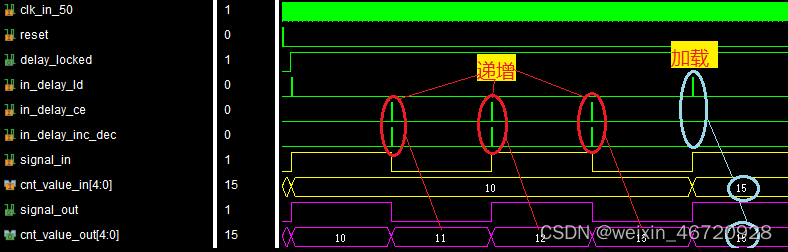

波形高度异常,忽高忽低,正常波形高电平和低电平是统一高度的

`timescale 1ns/1ns

module key_test_tb();

//parameter define

parameter CLK_PERIOD = 20;

parameter CNT_MAX = 25'd25; //仅用于仿真,对应 500ns

reg sys_clk; //周期 20ns

reg d;

wire q;

wire p;

wire n;

//信号初始化

//产生时钟

always #(CLK_PERIOD/2) sys_clk = ~sys_clk;

//例化待测设计

double_edge inst_double_edge(

.clk (sys_clk ),

.d (d ),

.q (q ),

.p (p ),

.n (n )

);

initial begin

sys_clk <= 1'b0;

d <= 0;

#(CLK_PERIOD*10)

d <= 1 ;

#(10);

d <= 0 ;

#(30);

d <= 1 ;

#(20);

d <= 1 ;

#(10);

d <= 0;

#(20);

d <= 1;

#(30);

d <= 0;

end

endmodule

module double_edge (

input clk,

input d,

output q,

output reg p,

output reg n

);

always@(posedge clk)begin

p <= q;

end

always@(negedge clk)begin

n <= d;

end

assign q = clk ? p : n;

endmodule

二、原因

在进行ModelSim波形仿真时,由于p和n的初始值是未定义的,所以它们的波形值显示为x,表示未确定的值,并且p的x态传递给q,p就被交替赋值为0,x,1,所以出现波形错乱。

always@(posedge clk)begin

p <= q;

end

x态:表示Unknown,仿真发生了不能解决的逻辑冲突。

出现状态x的原因:

- 未初始化信号:当你在模块中定义信号但没有明确初始化它们时,它们的值会被默认设置为 ‘x’。

- 冒险行为:在 Verilog 中,如果存在冒险行为(比如设置一个寄存器和读取它的值的操作之间的延迟很小),可能导致信号值为 ‘x’。

赋初值后波形中的x状态消失

module double_edge (

input clk,

input d,

output q,

output reg p = 0,

output reg n = 0

);

always@(posedge clk)begin

p <= q;

end

always@(negedge clk)begin

n <= d;

end

assign q = clk ? p : n;

endmodule