为双

QSPI (x8)

器件创建配置存储器文件

您可使用

write_cfgmem

Tcl

命令来为双

QSPI (x8)

器件生成

.mcs

镜像。此命令会将配置数据自动拆分为

2

个独立 的 .mcs

文件。

注释

:

为

SPIx8

生成

.mcs

时指定的大小即为这

2

个四通道闪存器件的总大小。

注释

:

write_cfgmem

Tcl

命令在为双

QSPI (x8)

模式构建

.mcs

文件时会将起始地址一分为二。

write_cfgmem

使用示例

此示例演示了如何为多重启动设计生成

.mcs

文件

,

此设计在地址

0

加载“黄金镜像”比特流并在地址

0x0100_0000 加载多重启动比特流。

器件

:

2

个

256 Mib QSPI

闪存器件

:

256 Mib = 32 MiB

总存储空间大小

:

2 * 32 MiB = 64 MiB

加载地址

:

黄金

:

0 * 2 = 0

多重启动

:

0x0100_0000 * 2 = 0x0200_0000

write_cfgmem -format mcs -interface spix8 -size 32 \

-loadbit "up 0 ./design1_spix8.bit up 0x02000000 ./design2_spix8.bit" \

-file design1_design2_spix8.mcs

连接到

Vivado

中的硬件目标

要连接到

Vivado

中的硬件目标

,

请执行以下操作

:

1.

确保在硬件目标的

FPGA

模式管脚上已选中相应的配置模式

(

Master SPI

或

Master BPI

),

以便从配置存储器器 件配置此 FPGA

。

如需了解更多信息

,

请参阅目标器件的相应“配置用户指南”。

2.

遵循“对

FPGA

器件进行编程”中的步骤

,

连接至硬件目标。

重要提示

!

如果开发板已掉电或者电缆已断开连接

,

那么

Vivado IDE

会关闭硬件目标。同时还会取消 Vivado 主线程中的任意

Vivado

操作。

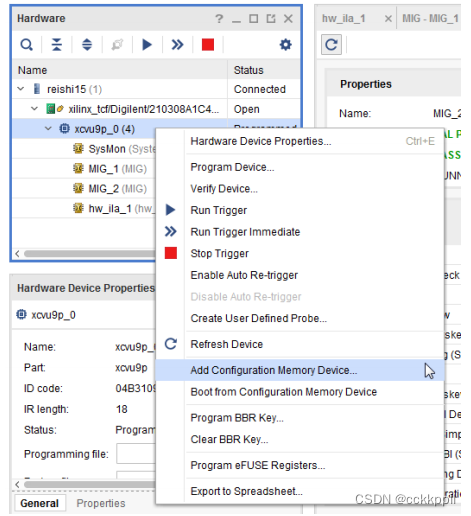

添加配置存储器器件

要将配置存储器器件添加至

Vivado

器件编程器中的硬件目标

,

请执行以下操作

:

1.

如上所述连接至硬件目标后

,

请右键单击硬件目标

(

如下所示

)

并选中“

Add Configuration Memory Device

”以 添加配置存储器器件。

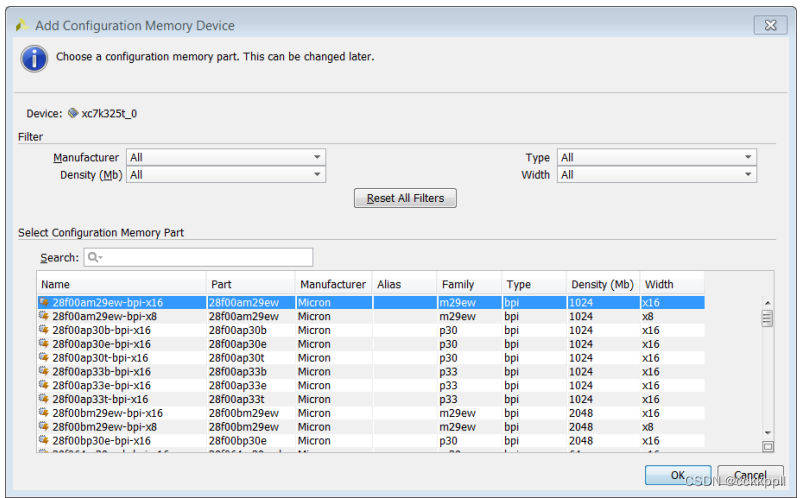

单击此菜单项即可打开“

Add Configuration Memory Device

”对话框

:

2.

选中相应的配置存储器器件

,

然后选择“

OK

”。

提示

:

选择“制造商

(Manufacturer)

”、“密度

(Density)

”或“类型

(Type)

”信息

,

并使用“

Search

”字段

缩小列表显示信息范围。 这样即可将配置存储器器件添加至硬件目标器件中。

对配置存储器器件进行编程

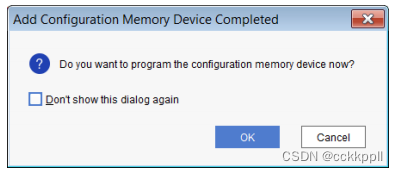

1.

创建配置存储器器件后

,

Vivado

器件编程器会发出如下提示

:

“您现在是否想要对配置存储器器件进行编程

?

(Do you want to program the configuration memory device now?)”。

单击“

OK

”即可打开“对配置存储器器件进行编程

(Program Configuration Memory Device)

”对话框。

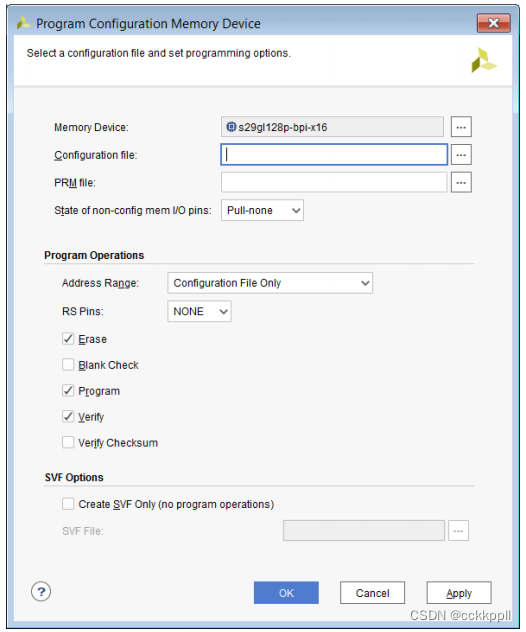

2.

选中此对话框中的所有字段

:

• “

Configuration file

”

(

.mcs

或

.bin

)

-

指定用于对配置存储器器件进行编程的文件。存储器配置文件将使 用 write_cfgmem

Tcl

命令来创建。请参阅“创建配置存储器文件”

,

以获取更多信息。

• 非配置存储器

I/O

管脚的状态

:

○

“

Pull-none

”

-

指定编程到

FPGA

中的间接配置比特流将未使用的

I/O

管脚设置为“

pull-none

”。

○

“

Pull-up

”

-

指定编程到

FPGA

中的间接配置比特流将未使用的

I/O

管脚设置为“

pull-up

”。

○

“

Pull-down

”

-

指定编程到

FPGA

中的间接配置比特流将未使用的

I/O

管脚设置为“

pull-down

”。

重要提示

!

确保非配置存储器

I/O

管脚的状态与

write_bitstream

属性中的设置相匹配。该属性默

认值为

pull-down

。

• “

Program Operations

”

(

在配置存储器器件上执行

)

。

○

“

Address Range

”

-

指定要编程的配置存储器器件的地址范围。可能的地址范围值如下

:

-

“

Configuration File Only

”

-

仅使用存储器配置文件所需的地址空间来执行擦除、空白检查、编程和验 证。

-

“

Entire Configuration Memory Device

”

-

将在整个器件上执行擦除、空白检查、编程和验证。

• “

RS Pins

”

-

可选。版本选择管脚映射

(Revision Select Pin Mapping)

,

仅限配合

BPI

配置存储器器件一起使用 (其中闪存上的前

2

个

FPGA

地址管脚绑定到

FPGA RS[1:0]

)

。启用该选项时

,

Vivado

会驱动

FPGA RS[1:0] 用于编程。请参阅相应的 FPGA

配置用户指南

,

以了解应用的用法。

• “

Erase

”

-

擦除配置存储器器件的内容。

• “

Blank Check

”

-

检查配置存储器器件

,

确保编程前器件中不含数据。

• “

Program

”

-

使用指定的配置文件

(

.mcs

或

.bin

)

对配置存储器器件进行编程。

• “

Verify

”

-

编程后

,

验证配置存储器器件的内容与配置文件

(

.mcs

或

.bin

)

相匹配。

• “

Verify Checksum

”

-

验证配置存储器器件中已编程的数据。该工具会基于配置存储器器件中已编程的数据来 计算校验和值,

然后将其与

.prm

文件中指定的校验和值进行比较。

提示

:

用户可生成

cfgmem

文件并指定

-checksum write_cftmem

选项。此步骤会创建

.prm

文

件

,

其中包含有关

cfgmem

输出文件的校验和信息。

• “

Create SVF Only

”

-

启用该选项即可支持以您指定的编程操作来创建

.svf

文件。其它第三方工具可使用 此 .svf

文件在

Vivado

外部对配置存储器器件进行编程。

重要提示

!

启用该选项时

,

Vivado

仅生成含相关编程选项的

.svf

文件。它不会实际对配置存储器器件执 行编程。

3.

单击“

OK

”以根据此对话框中的选择

,

在配置存储器器件上启动擦除、空白检查、编程和验证操作。每项操作完 成后,

Vivado

都会通知您。

注释

:

按下“

Apply

”将存储配置存储器设置

,

但不会对配置存储器器件进行编程。如果您在按下“应用

(Apply)

” 后按下“取消 (Cancel)

”

,

那么配置存储器器件将完成设置

,

并且可稍后执行编程。

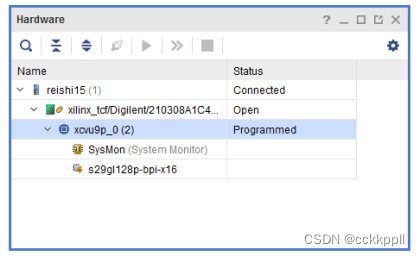

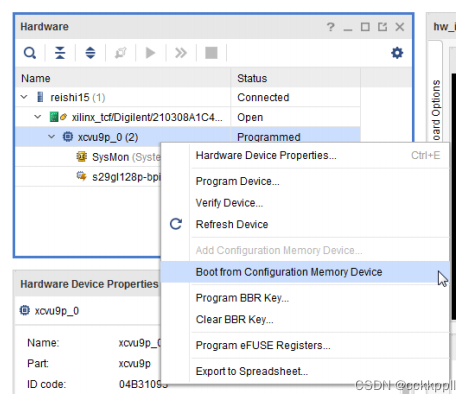

启动器件

对配置存储器器件进行编程后

,

您可发出软启动操作

(

即

,

JPROGRAM

)

以从所连配置存储器器件启动

FPGA

配置。

如果要在目标

FPGA

器件上执行启动操作

,

请选中目标器件

,

右键单击并选择“

Boot from Configuration Memory Device”。

重要提示

!

从配置存储器启动后

,

可能出现由于系统启动设置而导致调试核不立即显示的情况。赛灵思建议您等 待一段时间,

具体时间可在

Vivado

硬件管理器的

Tcl

控制台内使用

boot_hw_device

Tcl

命令来指定

,

如下所 示:

boot_hw_device after 1000 [refresh_hw_device]

其中

,

可指定的最大

wait_on

值为

1000

。

在主模式下配置失败

注释

:

以下内容在

MPSoC

或

Versal

架构上不予支持。

当开发板处于“主

BPI (Master BPI)

”模式或“主

SPI (Master SPI)

”模式下且

JTAG

线缆连接至

Vivado

硬件管理器 时,

可能会发生配置失败。如果硬件管理器轮询和恢复功能导致主模式配置中断

,

那么在上电时可能会发生间歇性配置 失败。为避免出现此问题,

请在

Vivado

硬件管理器

Tcl

控制台中设置以下参数以确保不对配置状态寄存器进行更新

:

set_param xicom.allow_cfgin_commands false

注释

:

此参数会影响整条链上的所有器件。