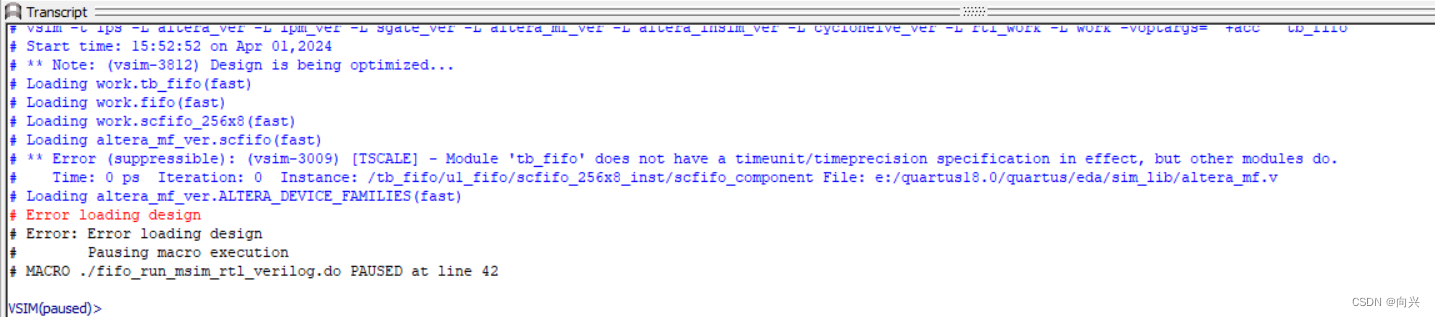

解决Quartus与modelsim联合仿真问题:# Error loading design解决,是tb文件中没加:timescale

- 1,一直走下来,在modelsim中出现了下面问题

- 2,rtl文件、tb文件

- 2.1,rtl代码

- 2.2,tb测试

- 2.3,netlist viewer

- 3,modelsim仿真波形

- 3.1,quartusII中的文件配置

- 3.2,modelsim中的波形

- 3.2.3,总体波形

- 3.2.2,局部波形

参考文献1,QuartusII18.0l与Modelsim10.5版本的联合仿真案例成功:3-8通路三态门输出

参考文献3,quartus 调用FIFO ip核

参考文献3,Quartus联合modelsim的ip核仿真——以FIFO为例——(报错问题解决)

1,一直走下来,在modelsim中出现了下面问题

解决:

(1)在tb中,加上时间刻度,时序必须加

(2)在rtl文件中,可以不含时间刻度

2,rtl文件、tb文件

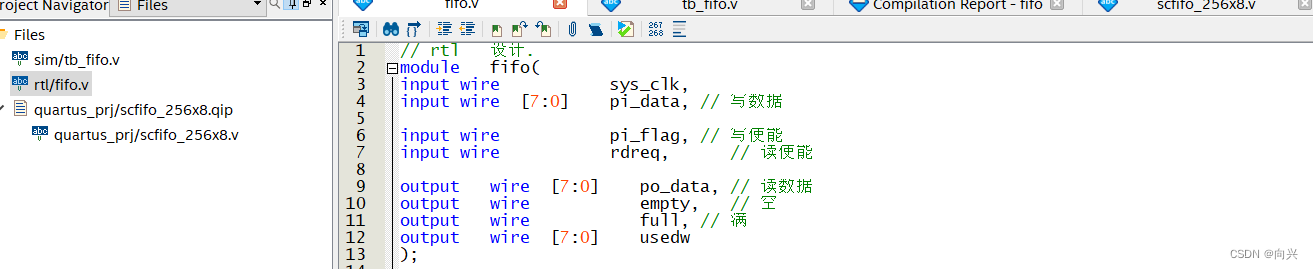

2.1,rtl代码

// rtl 设计.

module fifo(

input wire sys_clk,

input wire [7:0] pi_data, // 写数据

input wire pi_flag, // 写使能

input wire rdreq, // 读使能

output wire [7:0] po_data, // 读数据

output wire empty, // 空

output wire full, // 满

output wire [7:0] usedw

);

scfifo_256x8 scfifo_256x8_inst( // ip_core fifo

.clock (sys_clk ),

.data (pi_data ),

.rdreq (rdreq ),

.wrreq (pi_flag ),

.empty (empty ),

.full (full ),

.q (po_data ),

.usedw (usedw )

);

endmodule

2.2,tb测试

// 测试文件

`timescale 1ns/1ns

module tb_fifo;

reg sys_clk;

reg [7:0] pi_data;

reg pi_flag;

reg rdreq;

wire [7:0] po_data;

wire empty;

wire full;

wire [7:0] usedw;

always #5 sys_clk = ~sys_clk; // T = 10

initial begin

sys_clk = 1;

end

reg [7:0] cnt; // 计数器,计数写读个数.

initial begin

cnt = 8'd0;

pi_flag = 0; // 不写

pi_data = {$random}%256;

rdreq = 0; // 不读

#10

pi_flag = 1; // 写

pi_data = {$random}%256;

rdreq = 0;

repeat(256) begin // 只写

#10 pi_flag = 1; // 写

pi_data = {$random}%256;

rdreq = 0;

cnt = cnt + 1;

end

repeat(256) begin // 只读

#10 pi_flag = 0;

pi_data = 0;

rdreq = 1; // 读

cnt = cnt - 1;

end

repeat(10) begin // 同时写读

#10 pi_flag = 1;

pi_data = {$random}%256;

rdreq = 1;

cnt = cnt;

end

#100 $finish;

end

fifo u1_fifo(

.sys_clk (sys_clk ),

.pi_data (pi_data ), // 写数据

.pi_flag (pi_flag ), // 写使能

.rdreq (rdreq ), // 读使能

.po_data (po_data ),

.empty (empty ),

.full (full ),

.usedw (usedw )

);

endmodule

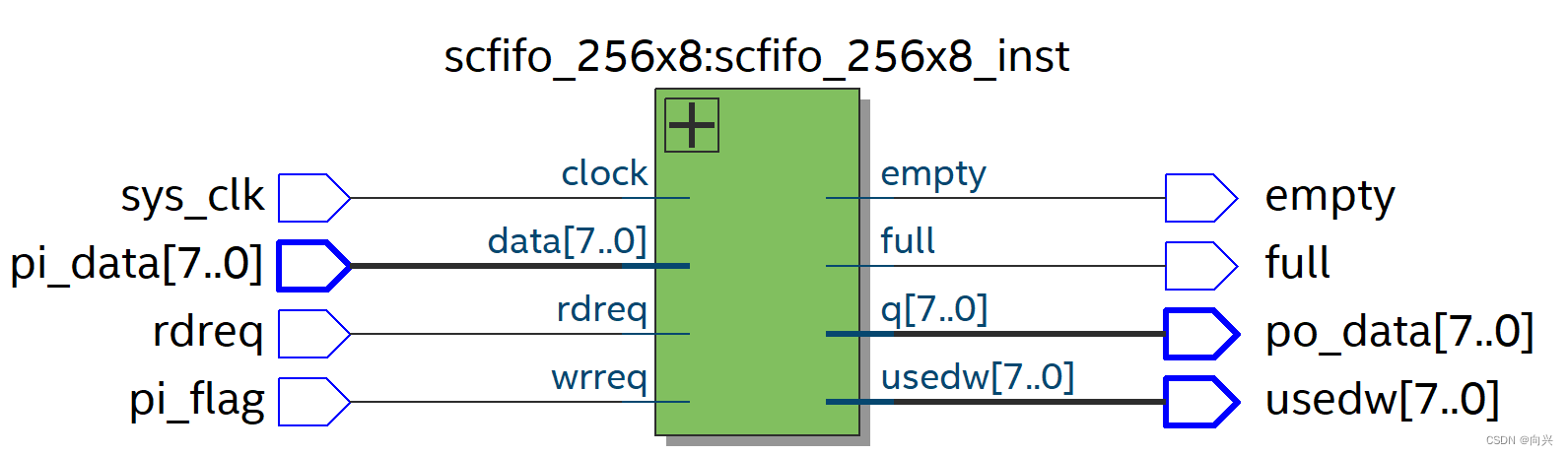

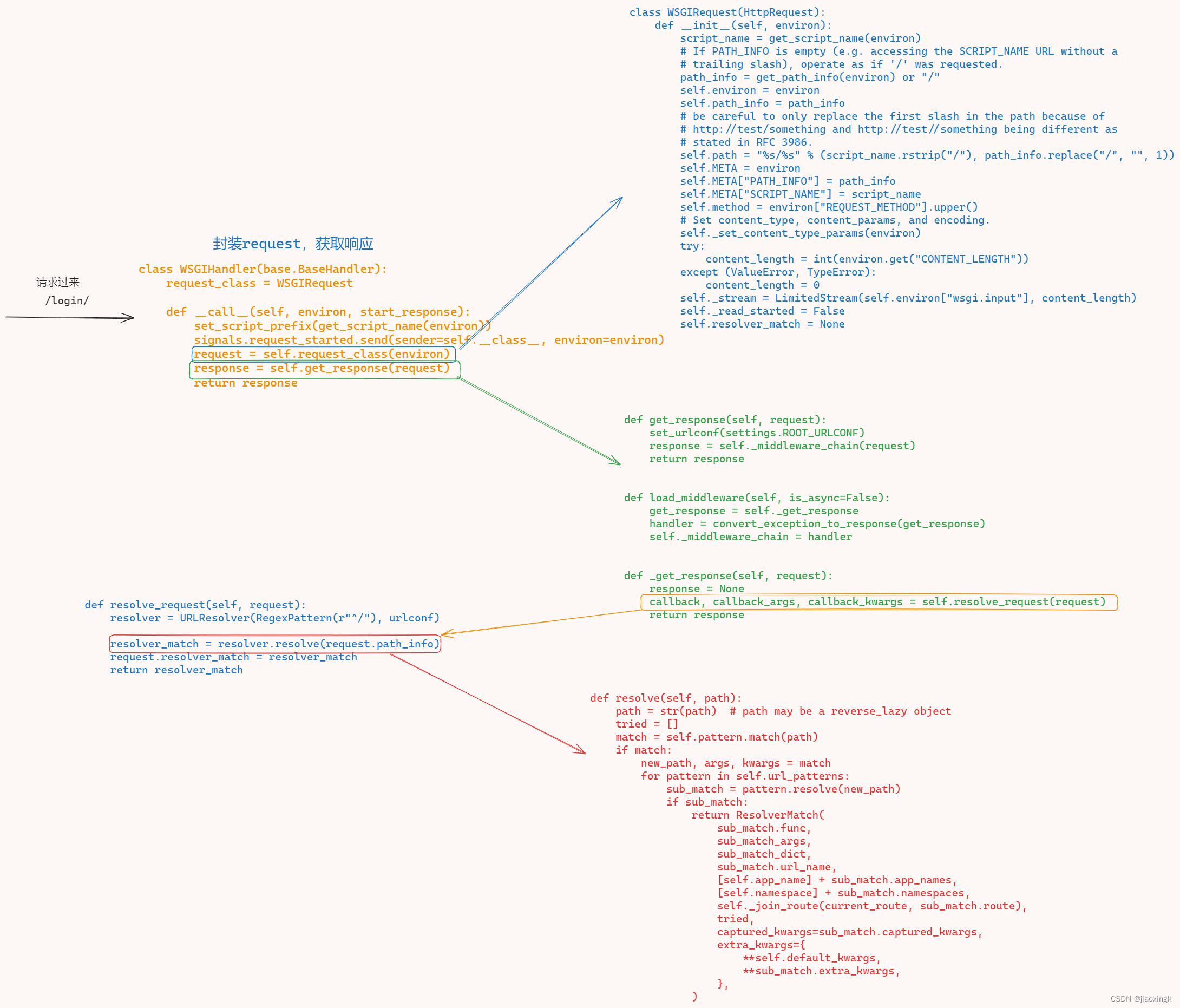

2.3,netlist viewer

(1)

(2)

3,modelsim仿真波形

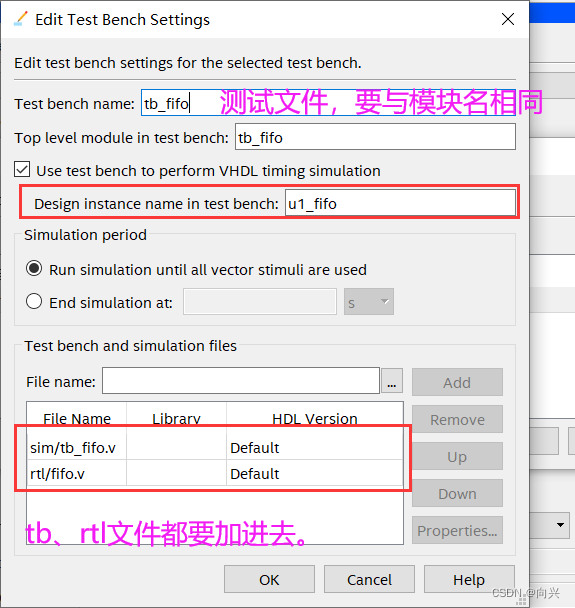

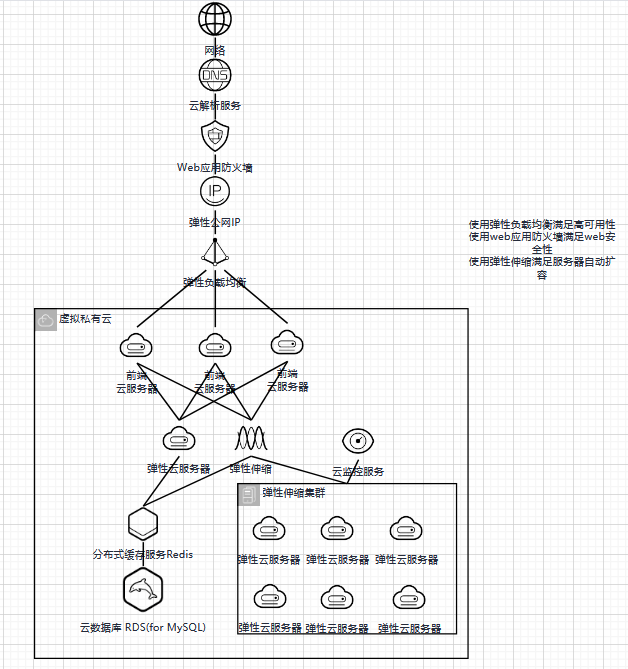

3.1,quartusII中的文件配置

(1)

(2)

3.2,modelsim中的波形

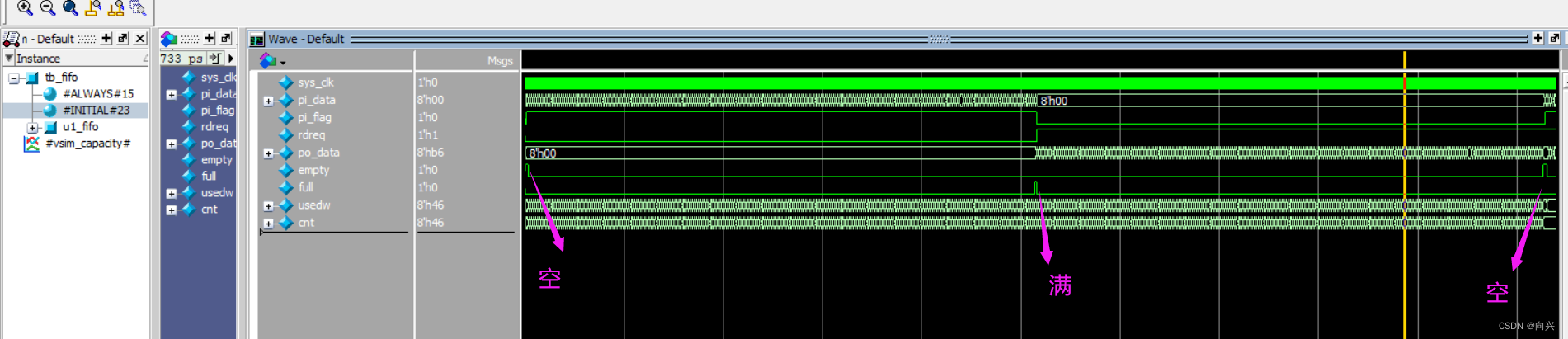

3.2.3,总体波形

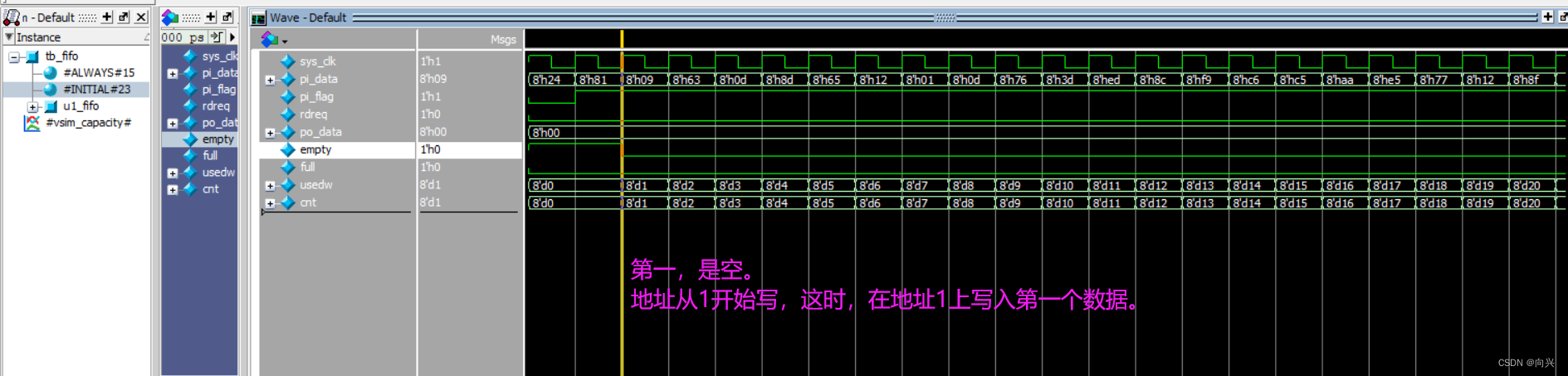

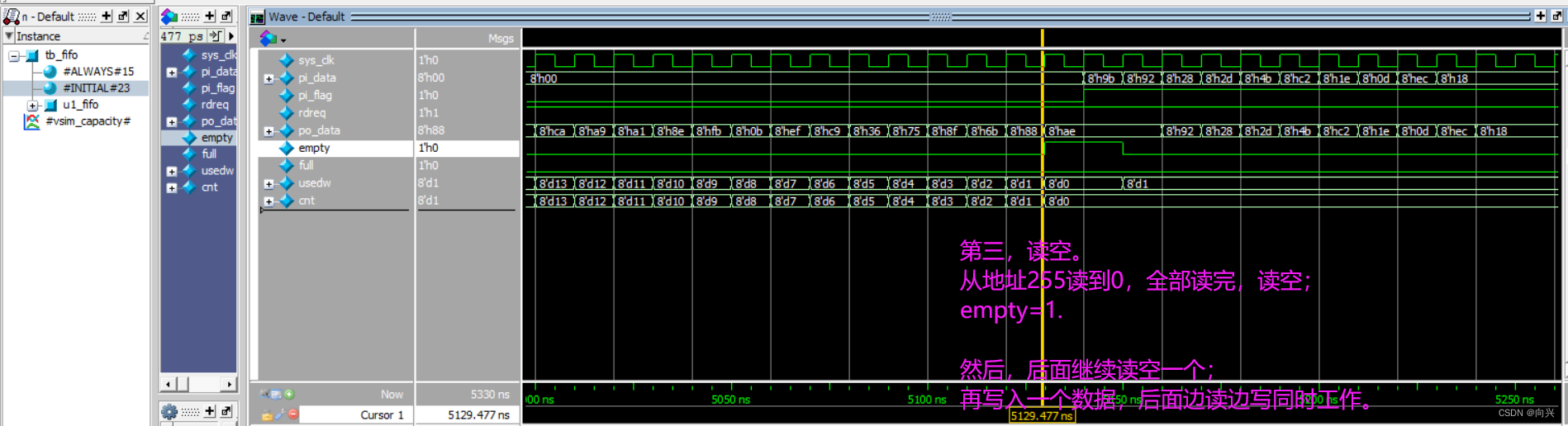

3.2.2,局部波形

(1)开始处,读空

(2)中间处,写满

(3),结束处,读空

![Vue项目中引入html页面(vue.js中引入echarts数据大屏html [静态非数据传递!] )](https://img-blog.csdnimg.cn/direct/becfb6e45b47419ab7abae46a4aa4c9e.png)