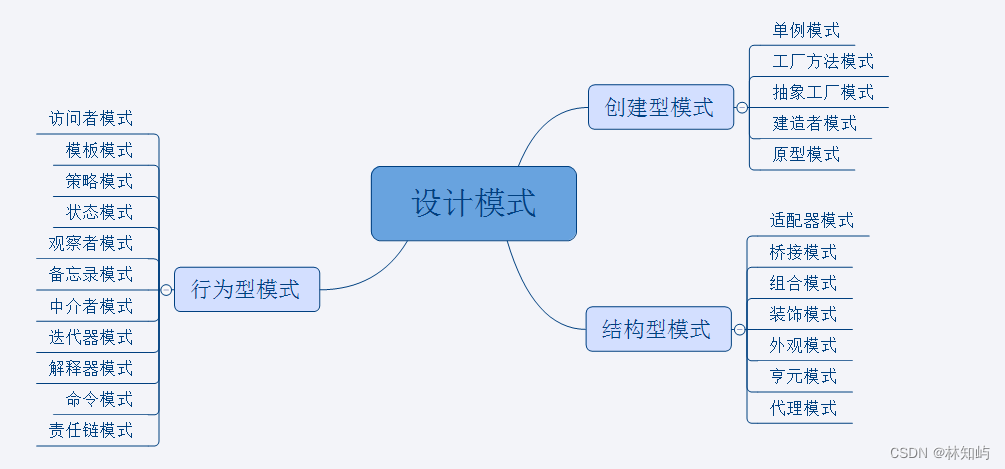

Chapter 17 Input Filter Design

在switching converter前面我们总想加一个input filter, 这样可以减少输入电流的谐波EMI(conducted electromagnetic interference).

另外, Input filter可以保护converter和负载不受输入电压瞬态变化的影响, 从而提高了系统稳定性.

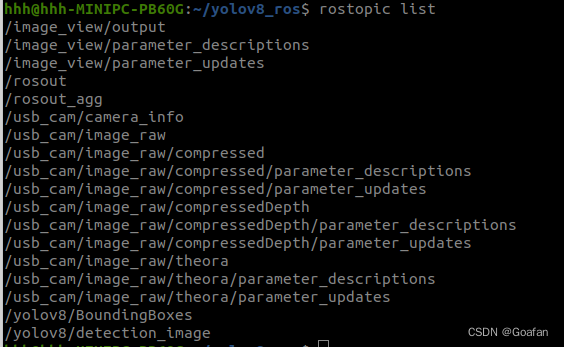

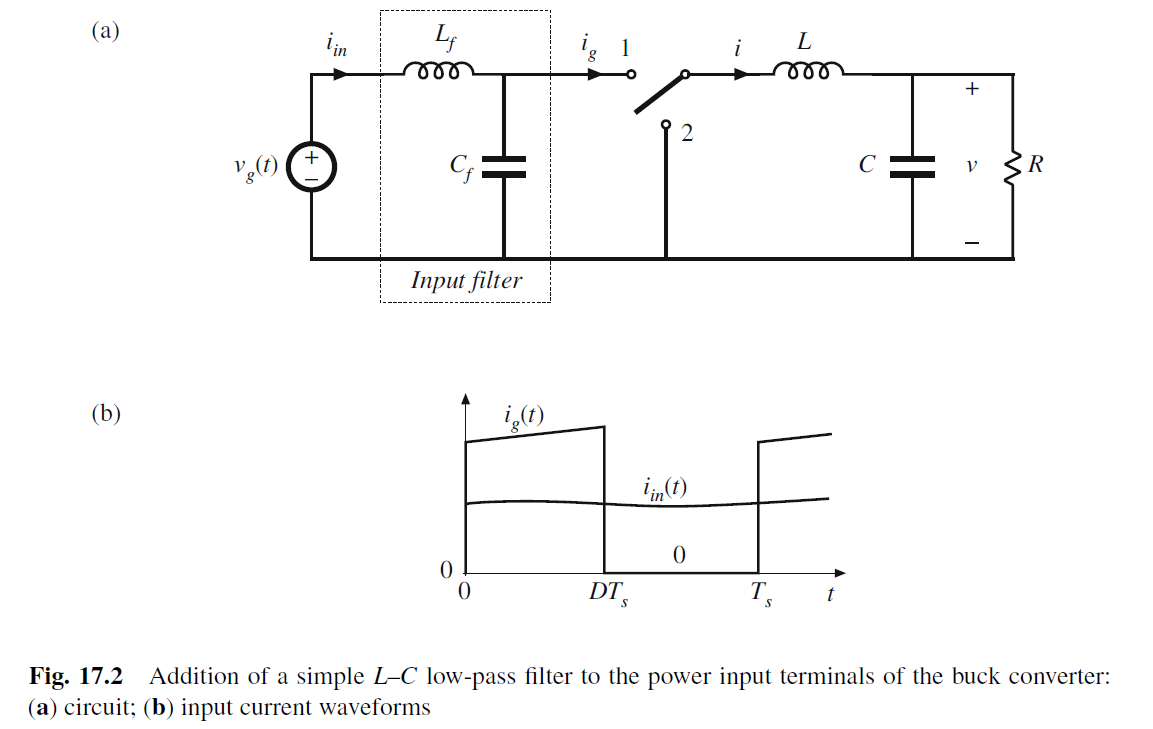

如下图所示, 加入LC filter, 输入电流的谐波大大减小, 不再是方波.

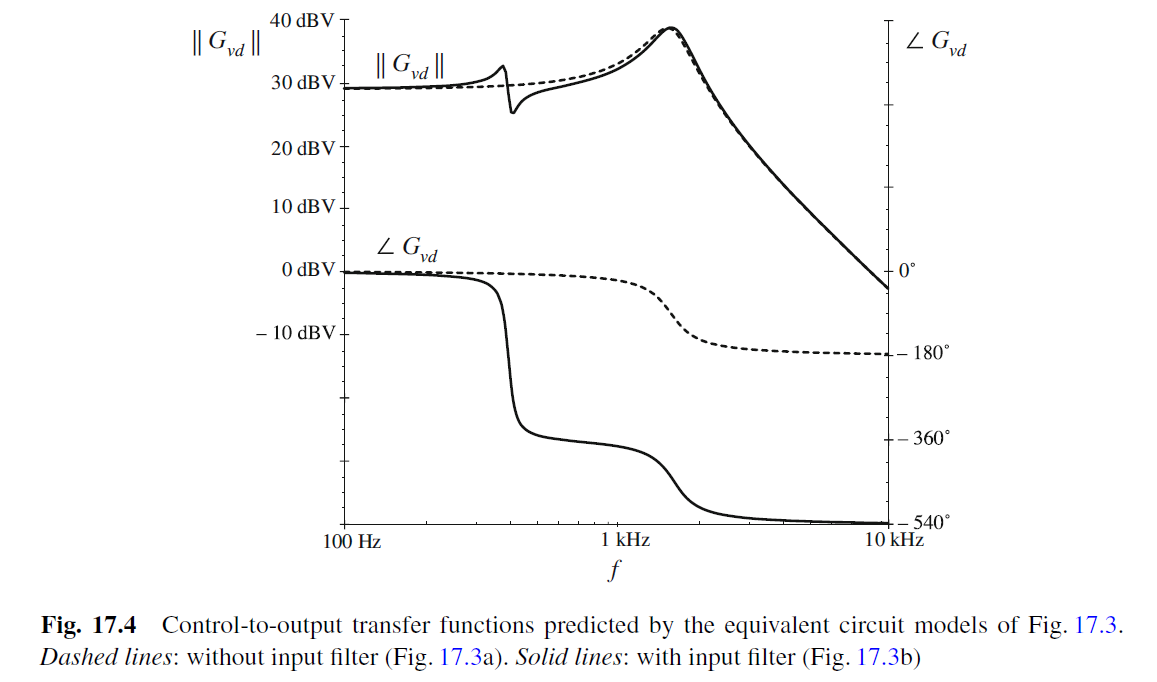

但是问题是加入LC input filter后, 系统引入共轭极点, 传输函数的phase大幅下降, stability出现大问题

17.2 Effect of an Input Filter on Converter Transfer Functions

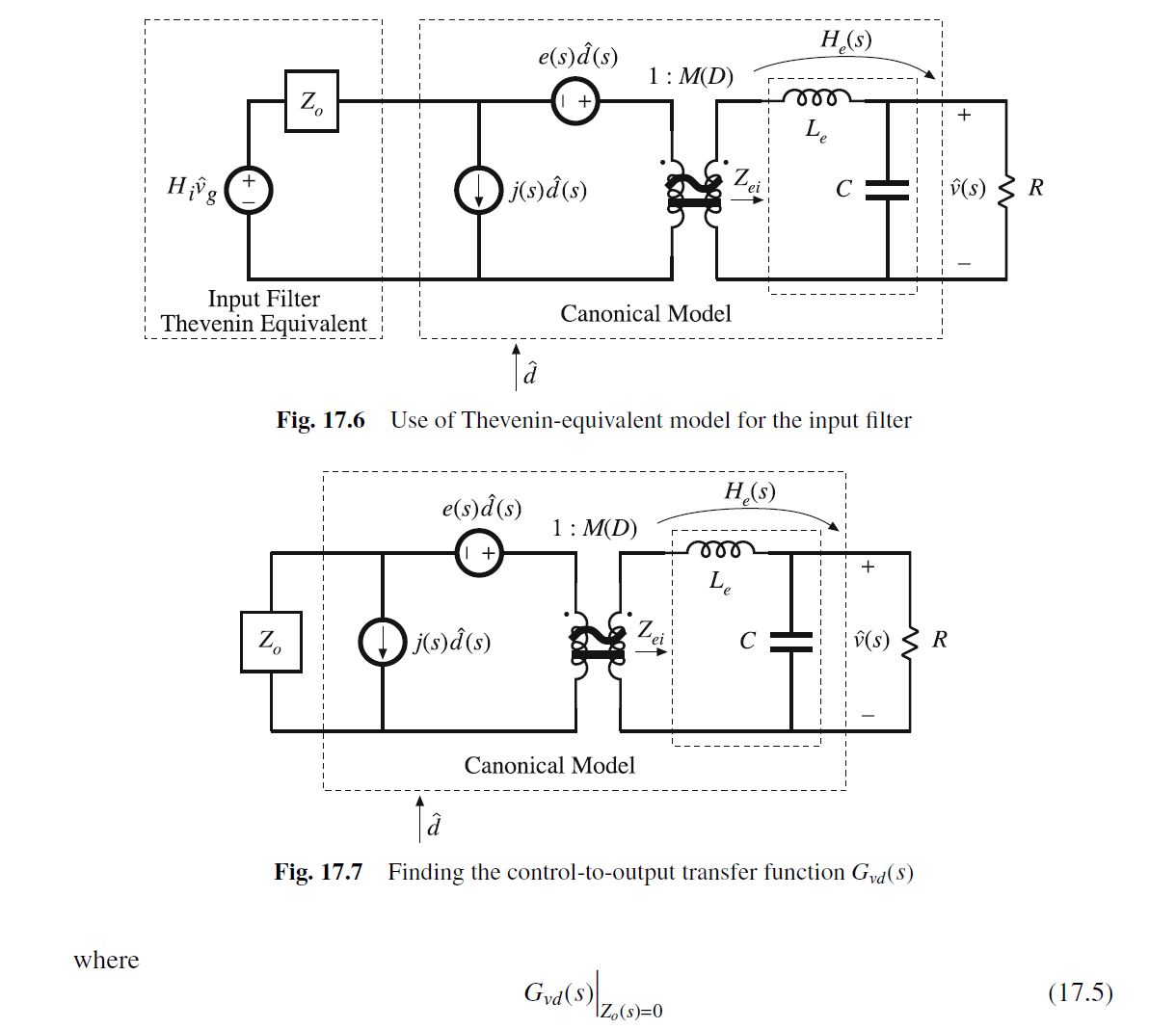

我们可以使用Chapter 16的Extra Element Theorem来得到加入input filter的传输函数.

G

v

d

(

s

)

=

(

G

v

d

(

s

)

∣

z

0

(

s

)

=

0

)

(

1

+

Z

0

(

s

)

Z

N

(

s

)

1

+

Z

0

(

s

)

Z

D

(

s

)

)

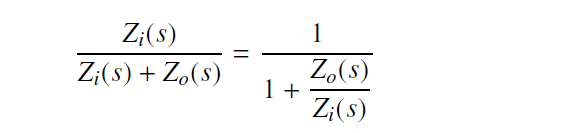

G_{vd}(s)=\left(G_{vd}(s)\bigg|_{z_0(s)=0}\right)\left( \frac{1+\frac{Z_0(s)}{Z_{N}(s)}}{1+\frac{Z_0(s)}{Z_{D}(s)}} \right)

Gvd(s)=(Gvd(s)

z0(s)=0)

1+ZD(s)Z0(s)1+ZN(s)Z0(s)

对于输出阻抗, 可以得到相似形式

ZN=Vtest/Itest at Vout nulled to Zero

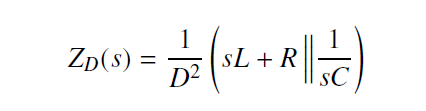

ZD=Vtest/Itest at d shorted to Zero. 注意是d,也就是duty ratio小信号模型

Z0=输入电压Vg set to zero, 看进去的impedance

我们希望设计

Z0<< ZN并且Z0<< ZD, 这样correction factor 就约等于1, input filter就不会影响原来传输函数的Loop Gain和补偿网络的设计.

如果

Z0<< ZE并且Z0<< ZE, 那么converter的open-loop impedance Zout就不会受到影响.

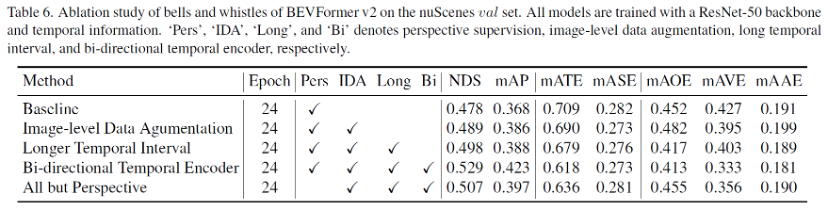

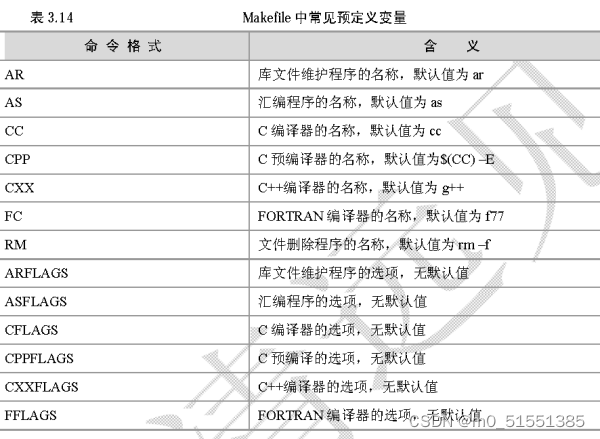

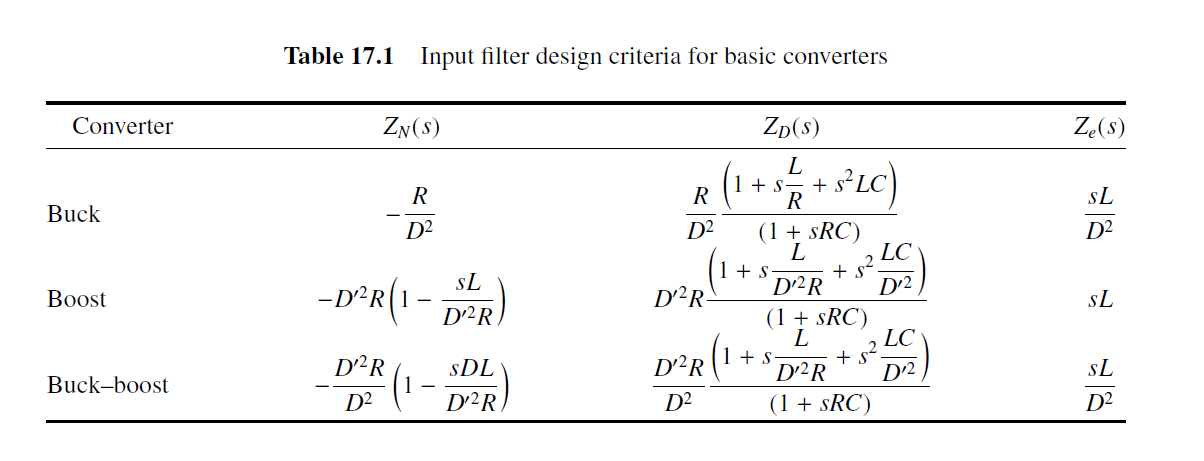

Buck, Boost, Buck-Boost的ZN和ZD表达式如下

17.3 Buck Converter Example

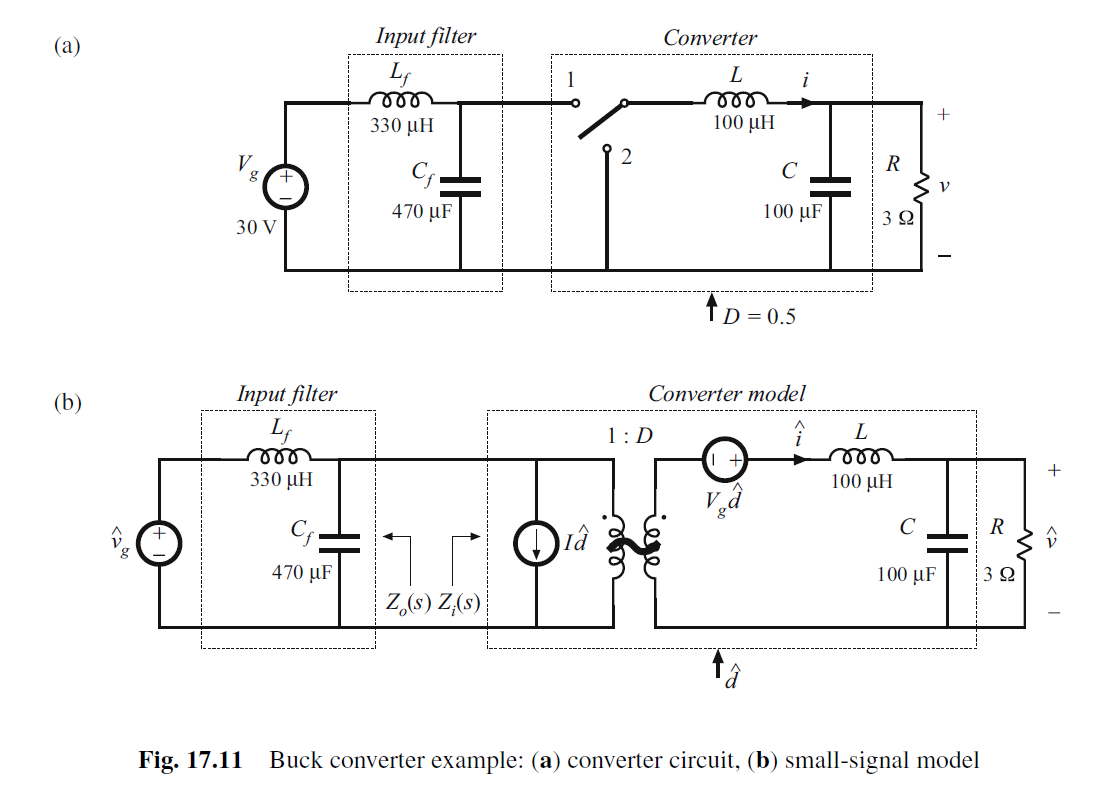

考虑Buck带上input filter的小信号模型

Buck的ZD=Vtest/Itest at d shorted to Zero

f

0

=

1

2

π

L

C

f_0=\frac{1}{2\pi \sqrt{LC}}

f0=2πLC1

ZN=Vtest/Itest at Vout nulled to Zero

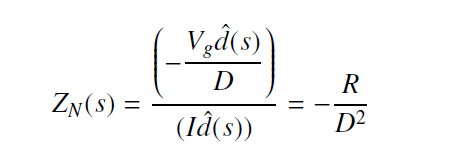

Z0=输入电压Vg set to zero, 看进去的impedance

Z

0

=

s

L

f

∥

1

s

C

f

Z_0=sL_f\parallel \frac{1}{sC_f}

Z0=sLf∥sCf1

f f = 1 2 π L f C f f_f=\frac{1}{2\pi \sqrt{L_fC_f}} ff=2πLfCf1

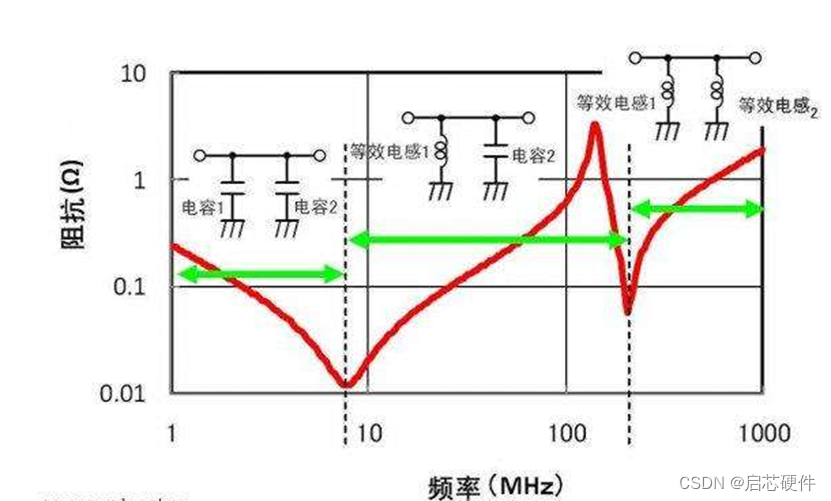

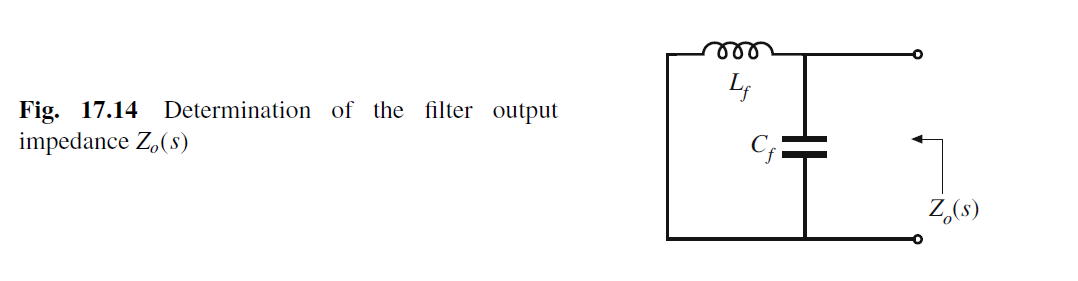

合理的input filter设计, 其impedance频率分布如下, 即ff和f0错开, 确保Z0<< ZN并且Z0<< ZD

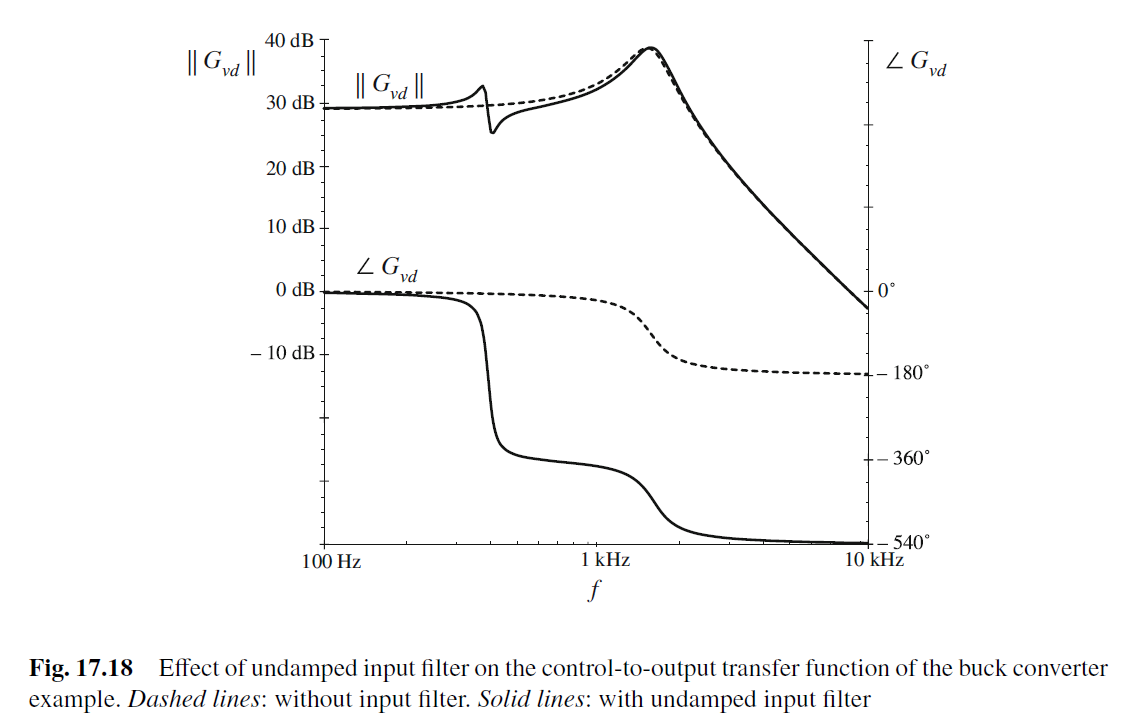

加入input filter后传输函数Gvd的变化, 虚线为原始波形, 实线为加入undamped input filter.

17.3.2 Damping the Input Filter

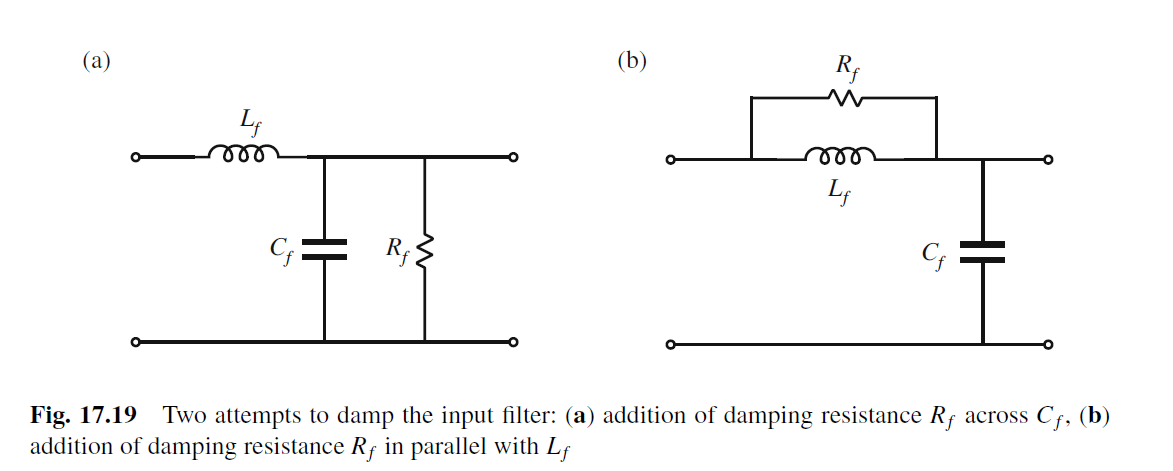

考虑在input filter加入damping resistor, 这样在所有频率下都可以满足impedance要求

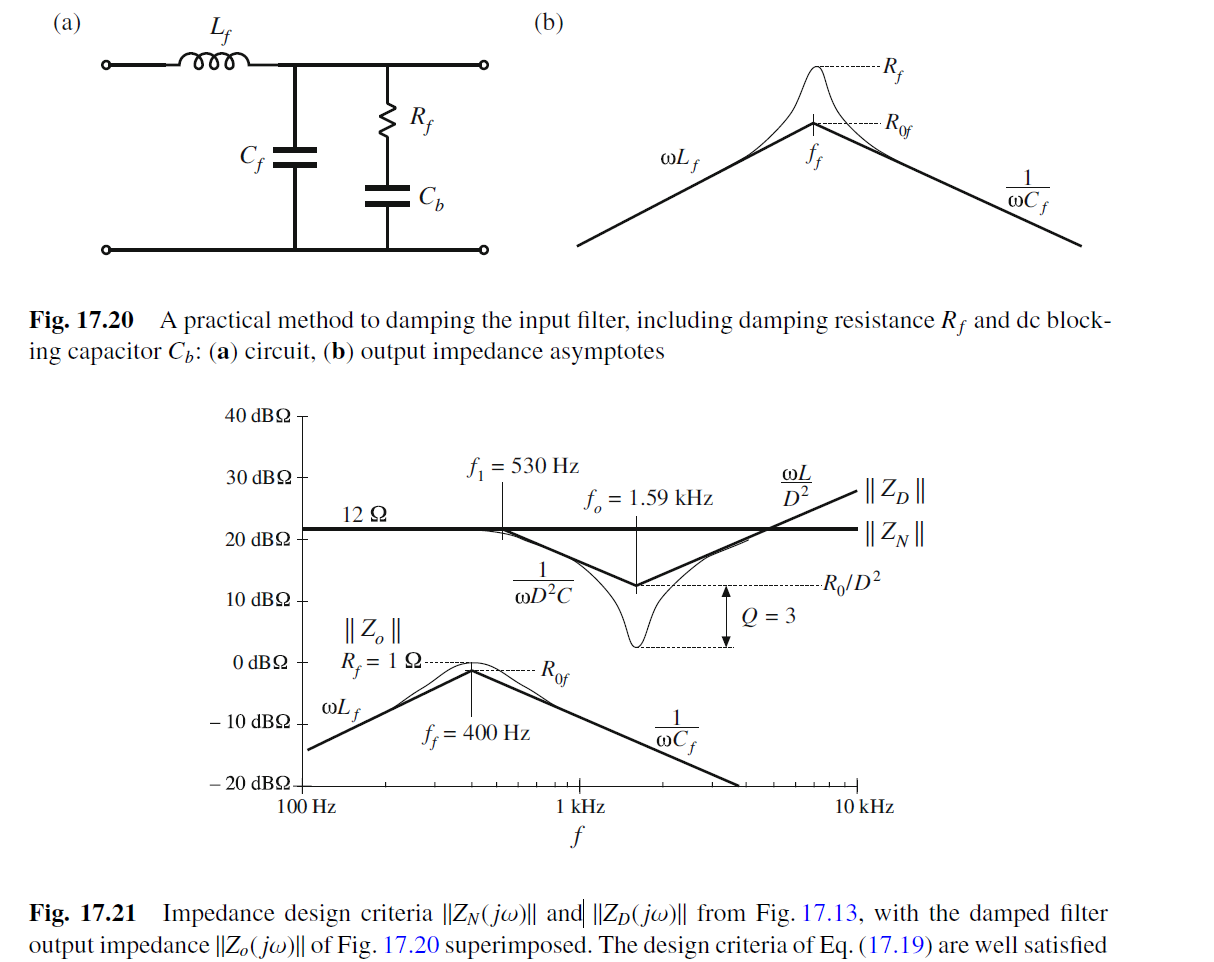

实际应用中会在resistor上加入dc blocking电容, 其impedance频率分布如下. 注意Cb = 10*Cf

17.4 Design of a Damped Input Filter

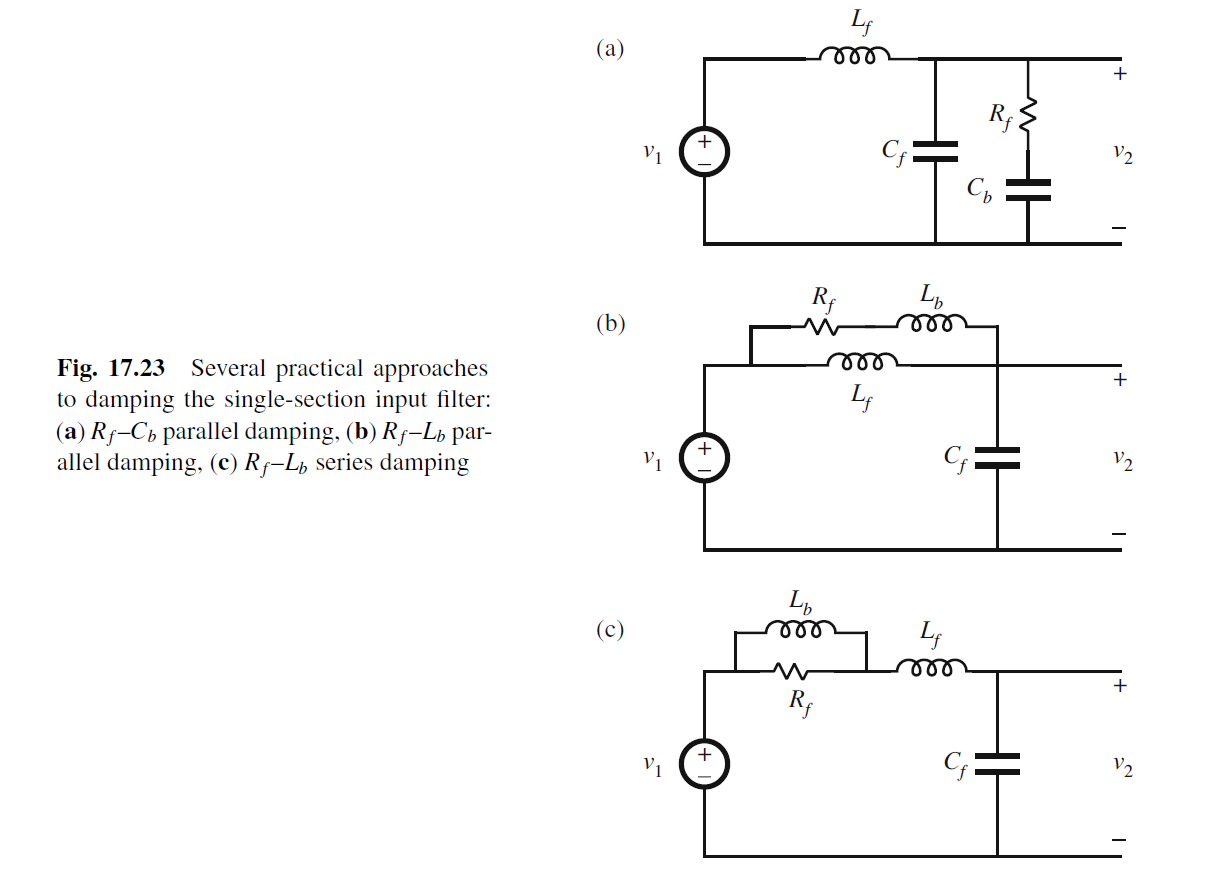

三种Damped Input Filter设计

问题是给定Cb和Lb, 如何找到Rf的值来minimizes the peak output impedance

17.5 Stability Criteria

前面章节关注input filter对Gvd的影响, 这一节我们关注input filter对Loop Gain的稳定性影响.

17.5.1 Modified Phase Margin

加入undamped input filter会引入共轭极点, 导致phase margin恶化, 掉360 deg.

因此需要减小loop crossover frequency, 确保环路稳定.

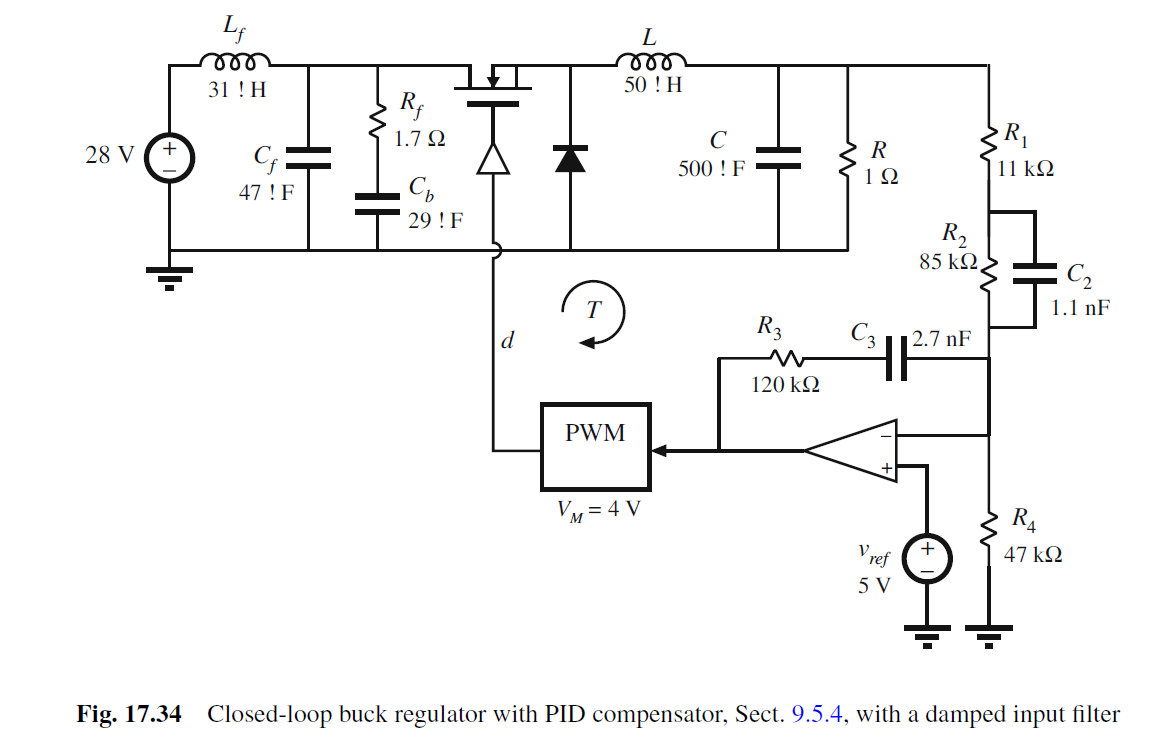

以下面这个buck为例

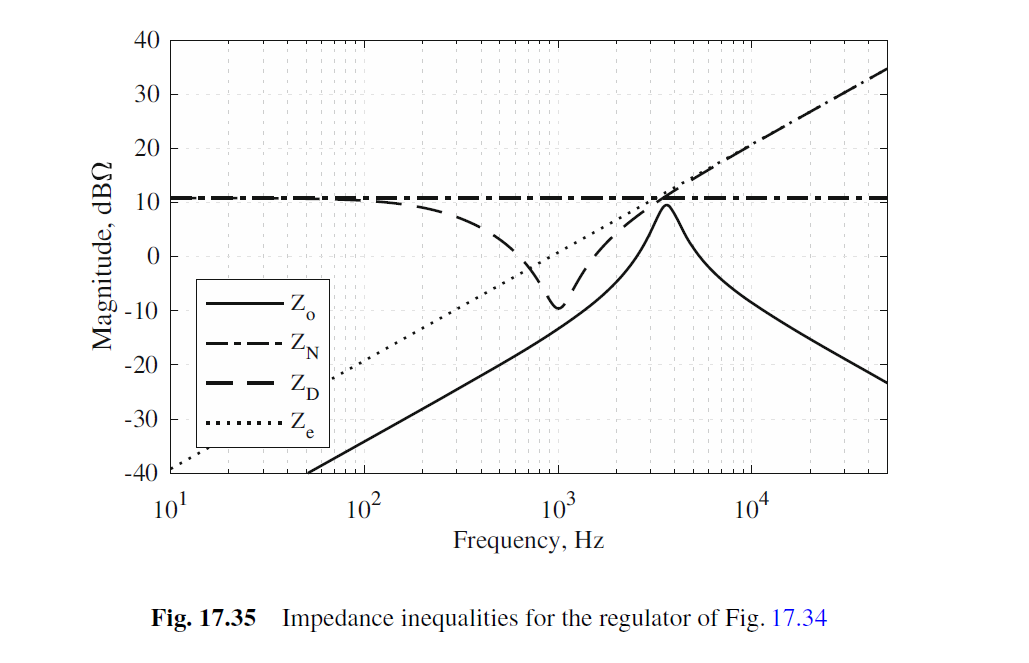

ZD, ZN, Ze分布

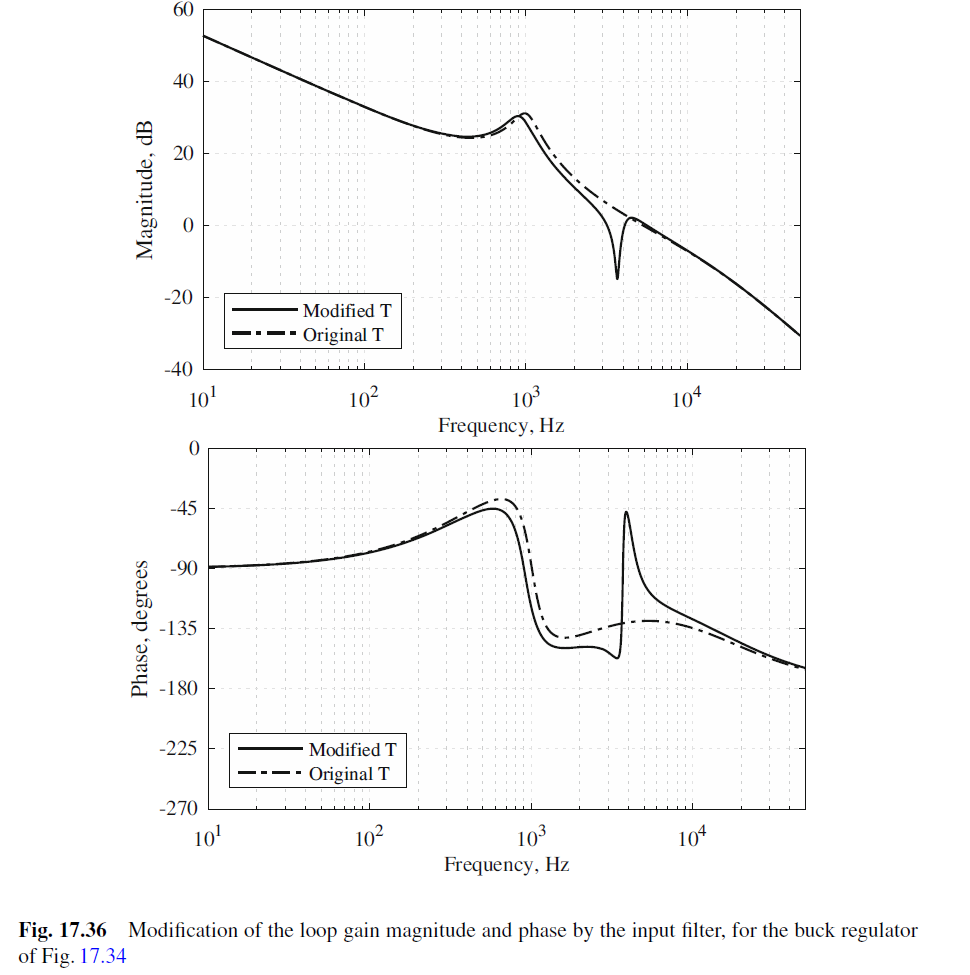

Loop Gain bode plot

17.5.2 Closed-Loop Input Impedance

在input filter上加closed-loop 的input impedance做voltage divider. 这样Zo可能引入右半极点