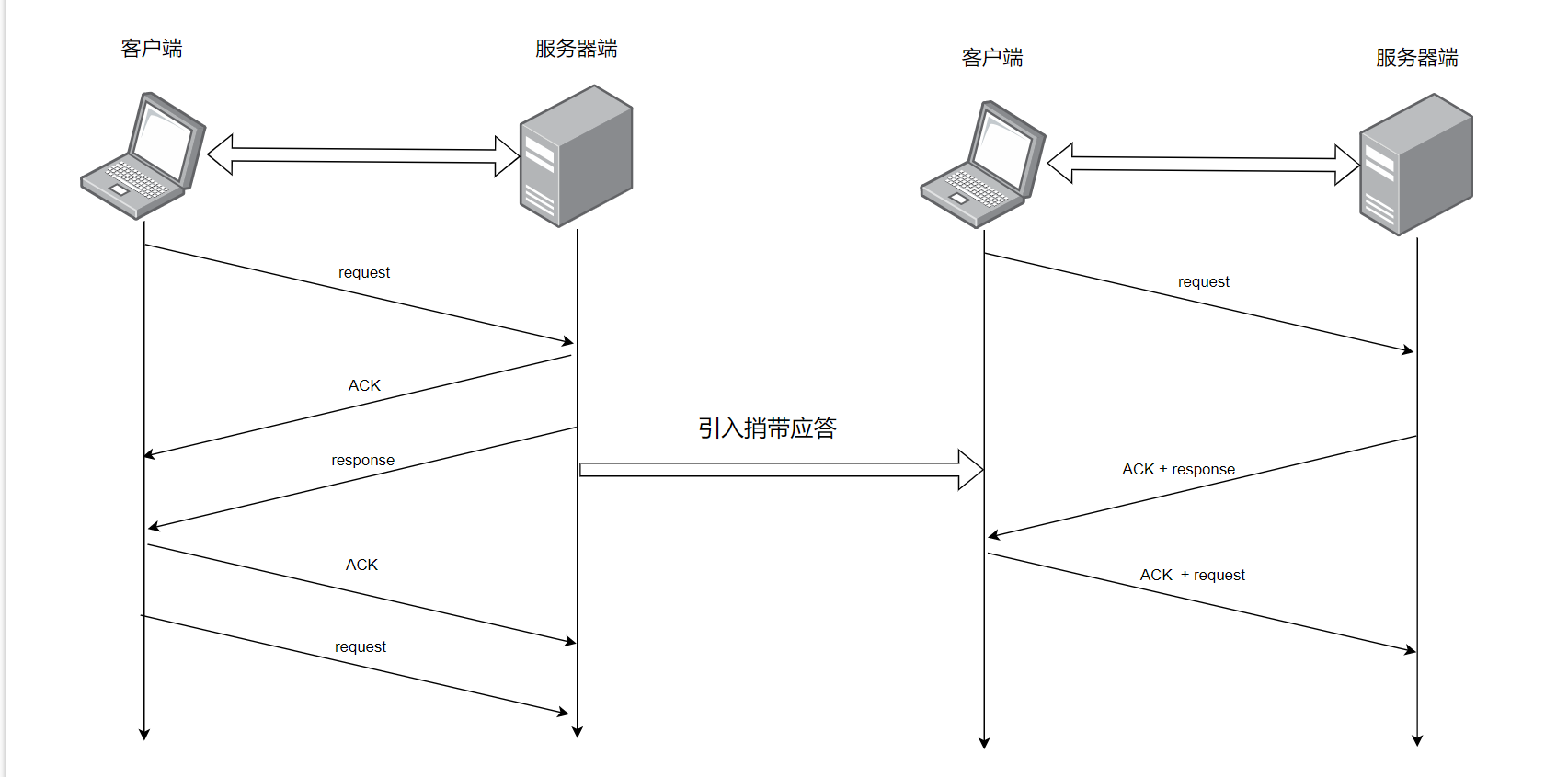

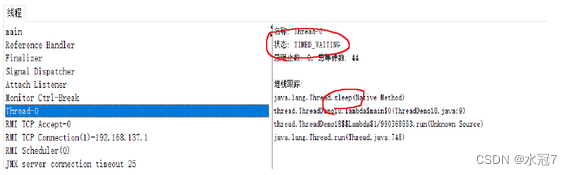

MDR取出数据,然后通过数据总线传递给CPU,

地址总线传递信号给到MAR

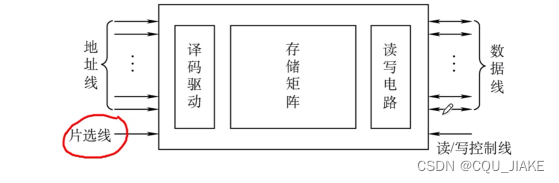

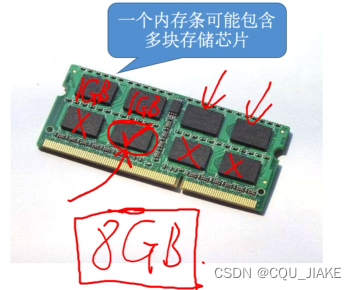

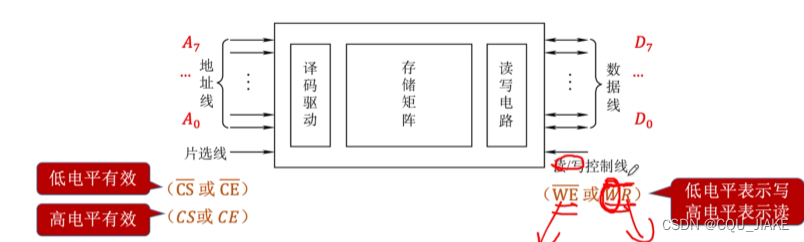

就是说片选线是用来选择操作哪个芯片

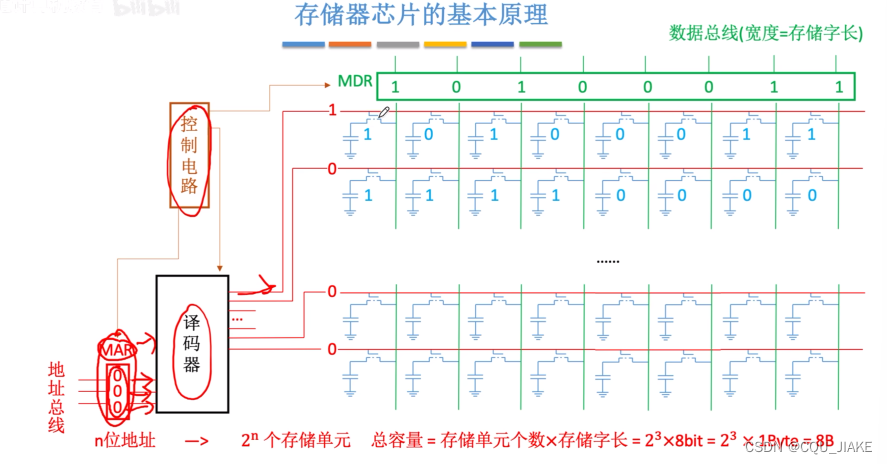

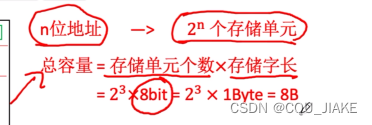

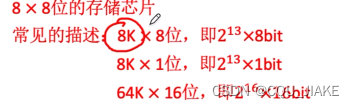

8*8位

第一个代表存储单元的数量,第二个代表存储字长

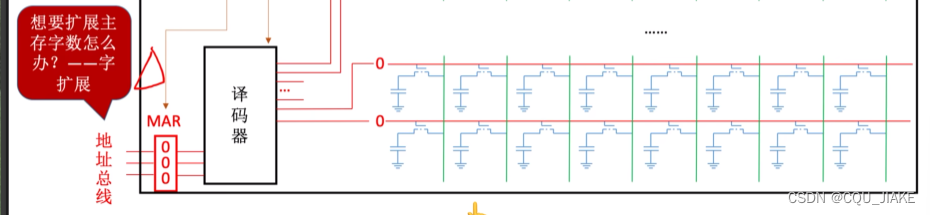

有几个存储单元,就对应多少位地址以及多少的地址线

存储字长决定数据线的数量

字节寻址,1B是一字节8BIT,总容量=个数*大小,寻址的时候变的是大小,因此变的是个数

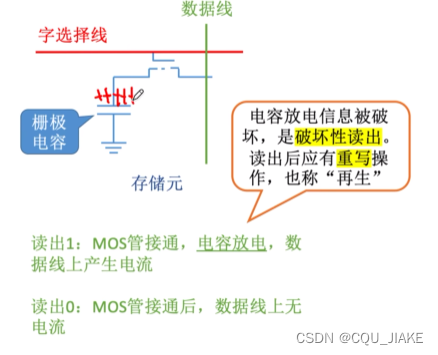

充电的过程是写的过程,放电是读的过程

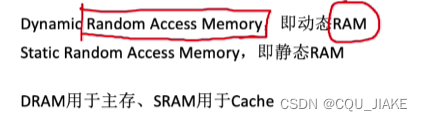

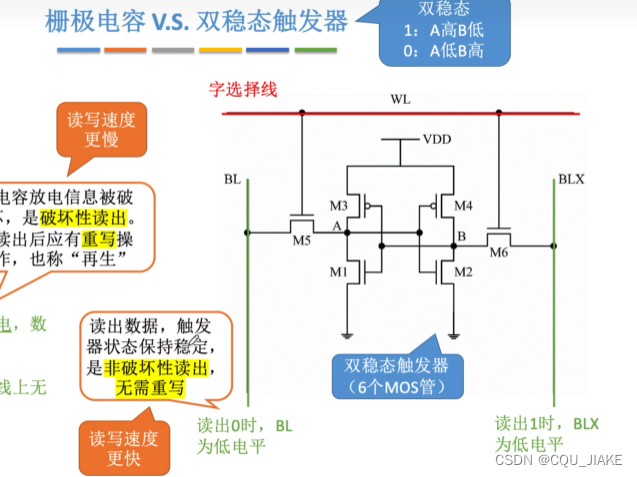

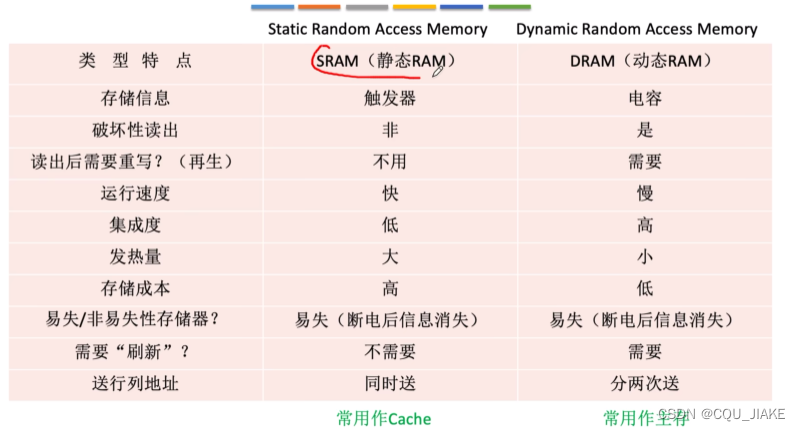

SRAM,DRAM

DRAM

栅极电容的读出数据线只有1根,而双稳态有两根

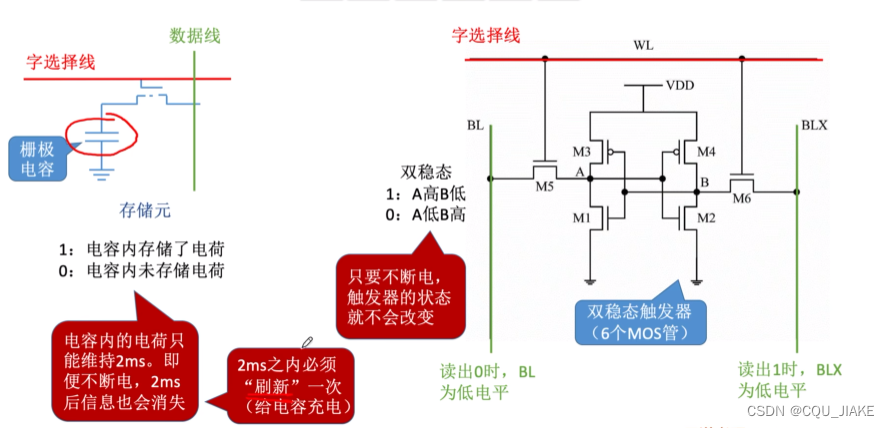

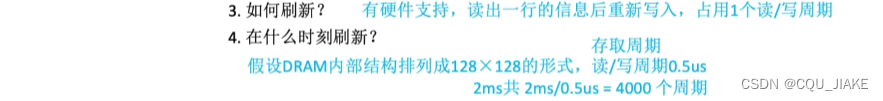

所谓刷新就是这个

所谓刷新就是这个

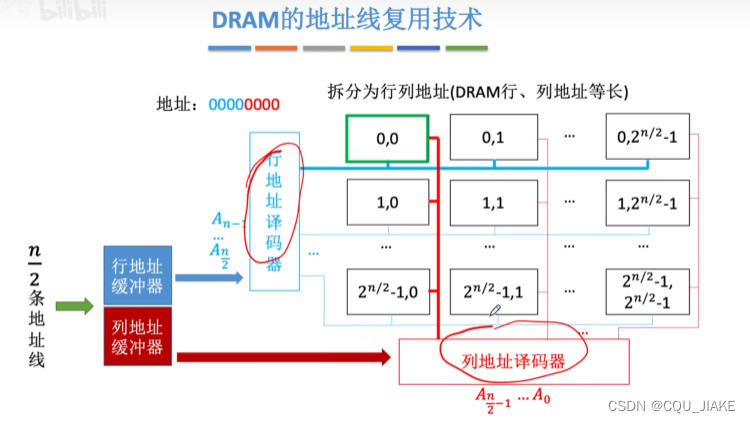

行列地址分两次送,地址线数量更少,芯片引脚更少

对于DRAM常用作主存,存储数量多,地址线多,所以要分两次送,可以减少一半的引脚数量;而对于SRAM,存储数量少,就不需要分两次

DRAM刷新

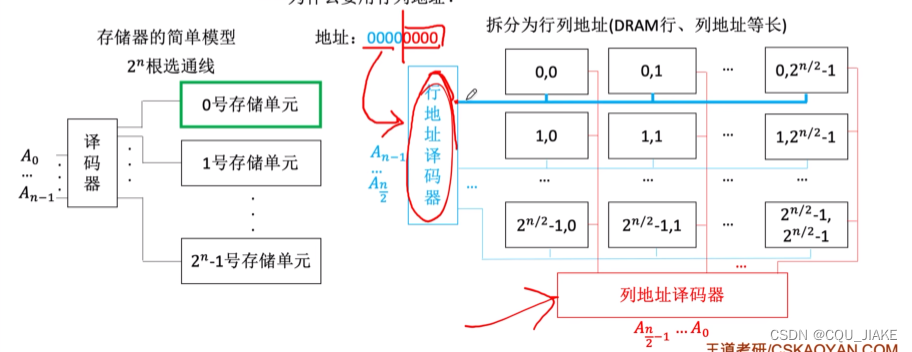

目的是减少线的数量,减少选通线的数量

对于一维时,地址就直接是位置,二维时前一半是行的坐标,后一半是列的坐标

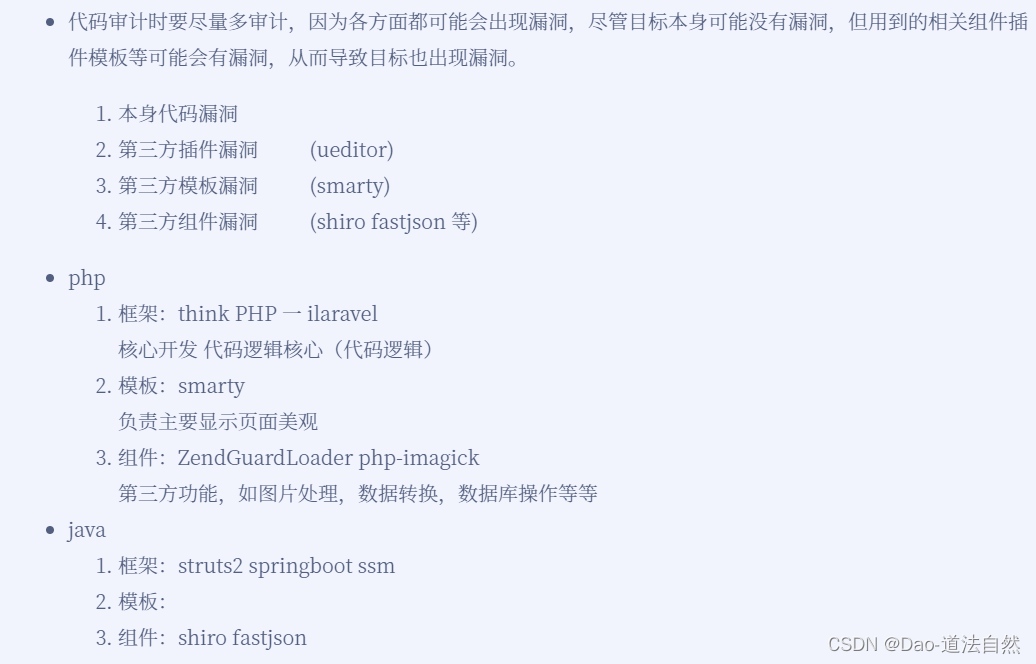

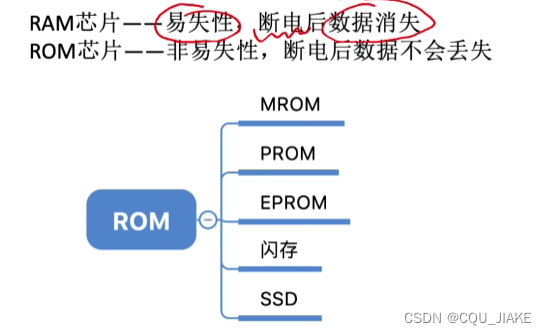

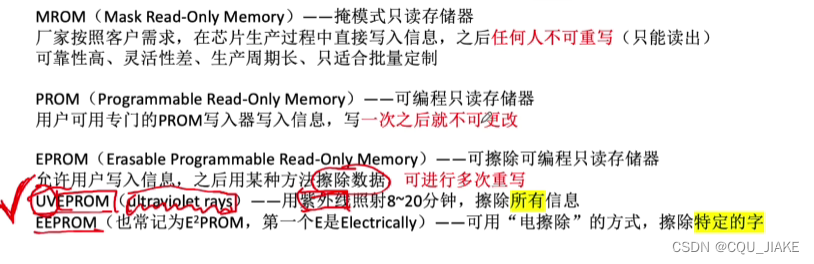

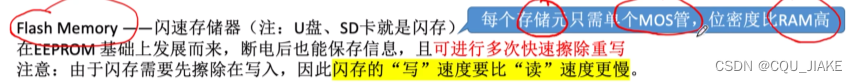

ROM

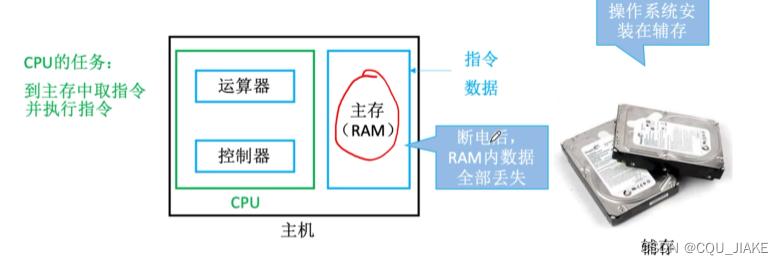

RAM是内存,ROM是辅存

所谓断电就是开机关机

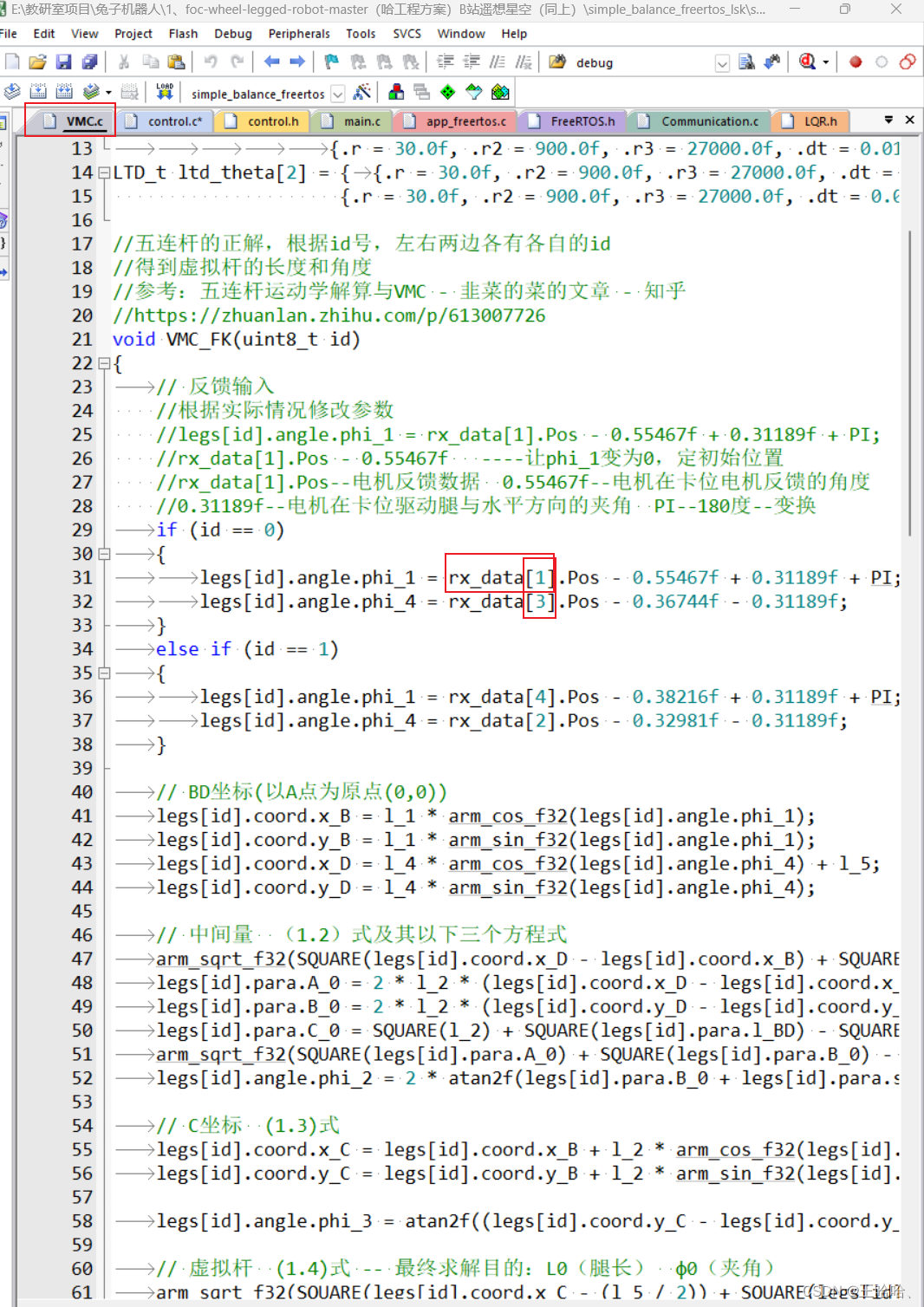

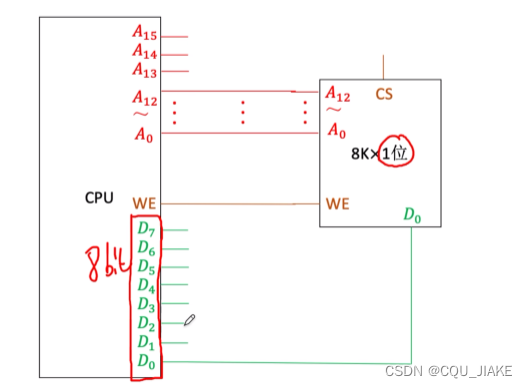

主存储器与CPU连接

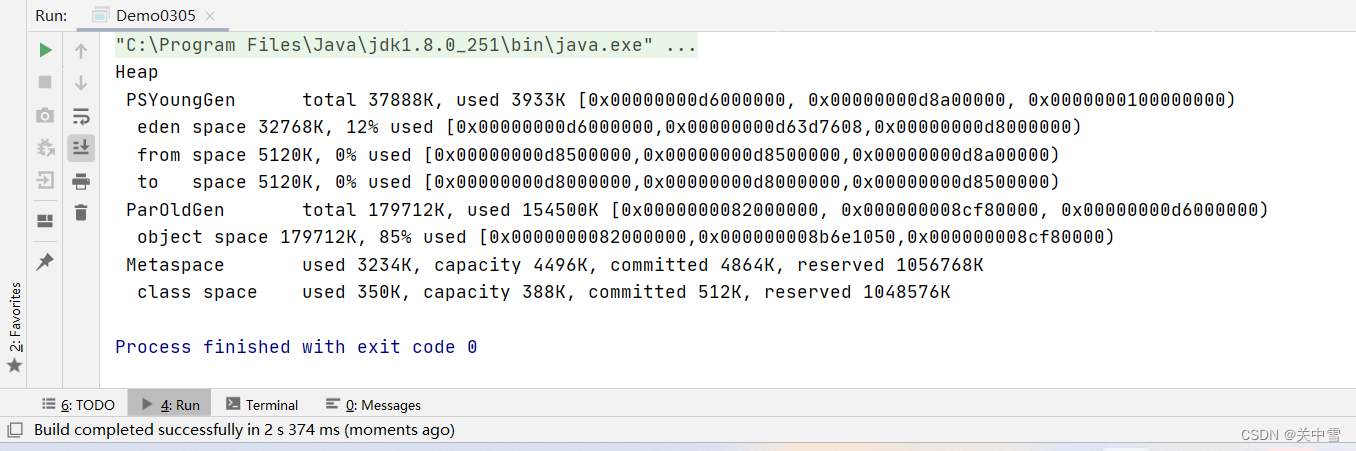

8K*1位是说有8K个存储单元,每个数据的位数是1位

1K是2^10

CPU的数据总线利用能力不充分