前言:

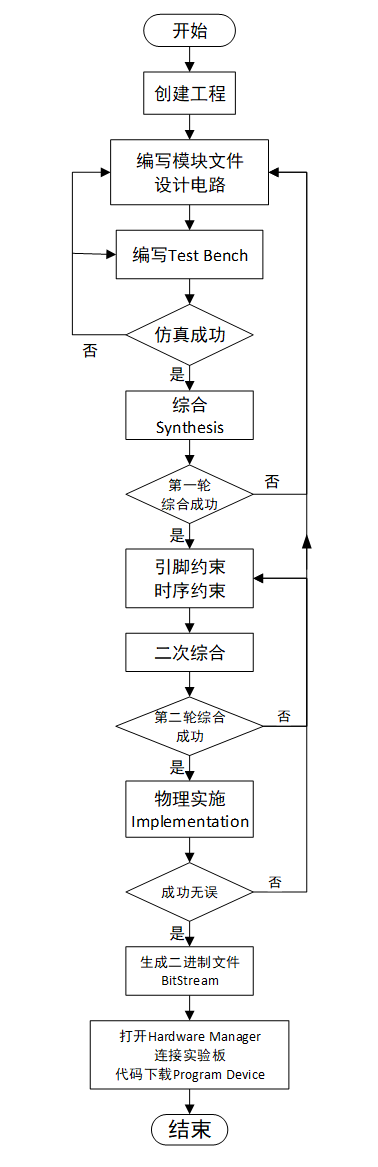

本章内容主要是演示Vivado下利用Verilog语言进行电路设计、仿真、综合和下载的完整过程、Verilog语言基本运用,电路设计和Test Bench程序的编写、以及实验开发板的使用,通过观察和数据记录理解仿真和FGPA实现的差异。

目录

Ⅰ. 基础知识速览:

0x00 硬件信息

0x01 实验流程分析

Ⅱ. Verilog代码设计

0x00 工程的创建

0x01 功能电路的创建

0x02 添加仿真激励程序

0x03 观察记录仿真波形

Ⅲ. 通过实验板观察与验证

0x00 添加硬件约束文件

0x01 电路生成

0x02 实验板使用

Ⅰ. 基础知识速览:

0x00 硬件信息

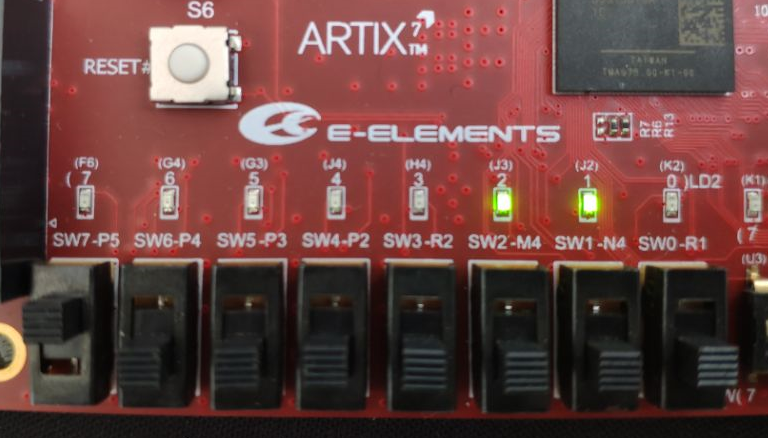

- 功能特性: 采用 Xilinx Artix-7 XC7A35T芯片

- 配置方式:USB-JTAG/SPI Flash

- 高达100MHz 的内部时钟速度

- 存储器:2Mbit SRAM N25Q064A SPI Flash(样图旧款为N25Q032A)

- 通用IO:Switch :x8LED:x16Button:x5DIP:x8 通用扩展IO:32pin

- 音视频/显示: 7段数码管:x8 VGA视频输出接口 Audio音频接口

- 通信接口:UART:USB转UART Bluetooth:蓝牙模块

- 模拟接口: DAC:8-bit分辨率 XADC:2路12bit 1Msps ADC

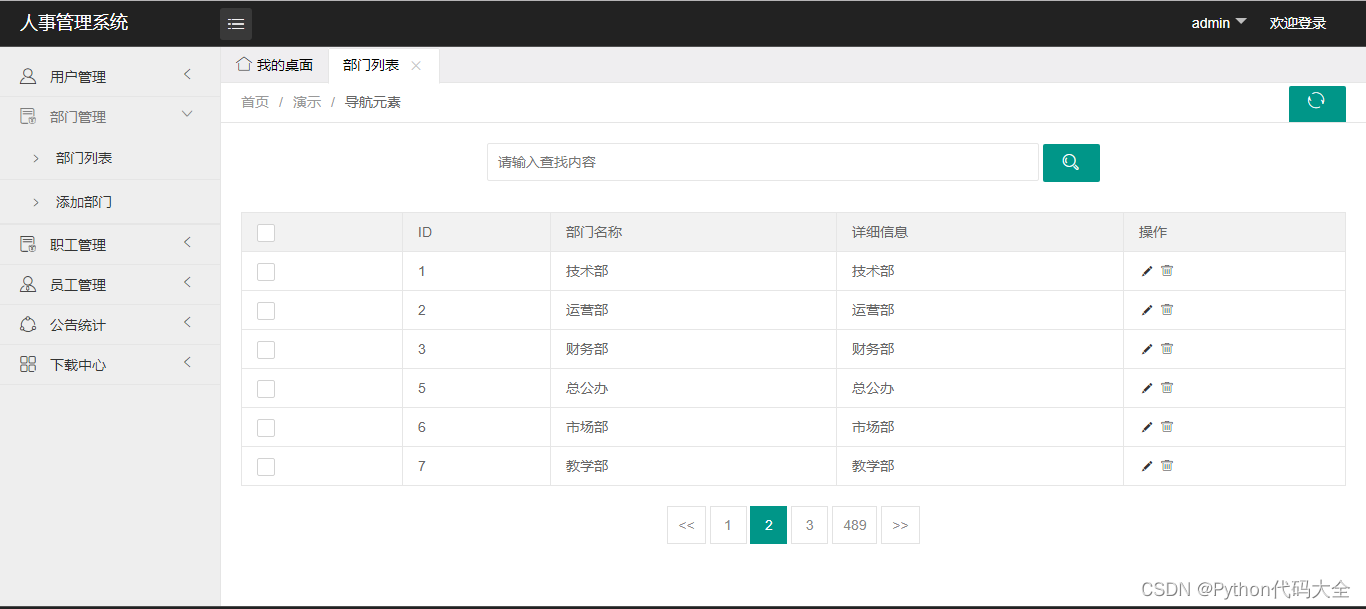

0x01 实验流程分析

Ⅱ. Verilog代码设计

0x00 工程的创建

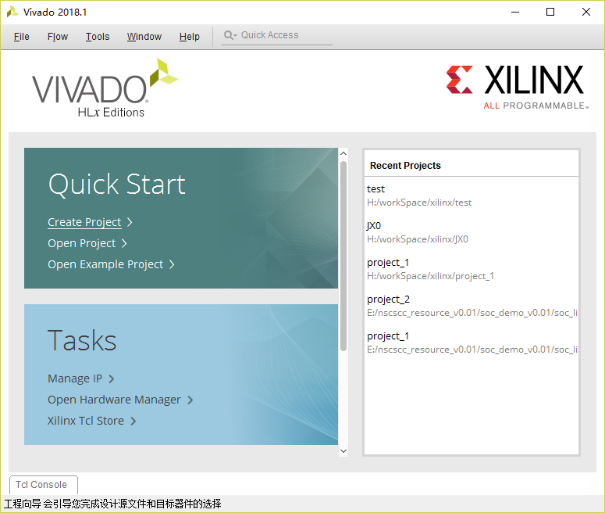

打开vivado,点击create project新建工程;

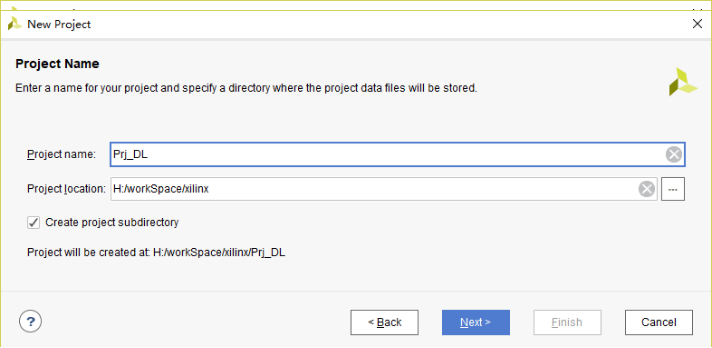

选择自己的工作区文件夹,输入合适的工程名;

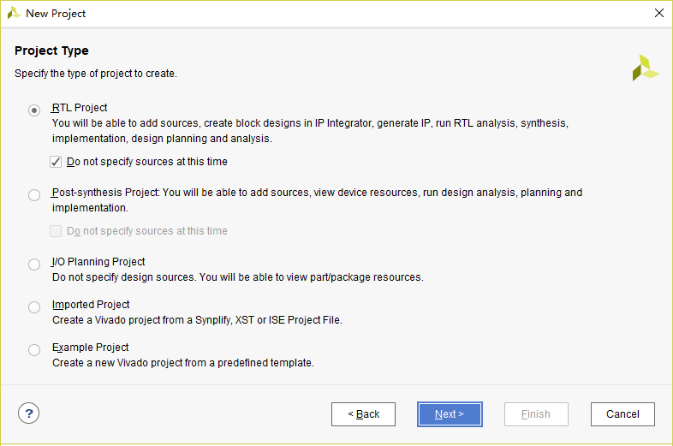

工程类型可以默认,即RTL项目,不包含指定代码;

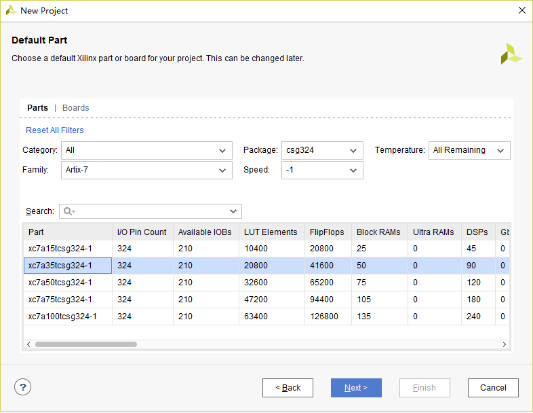

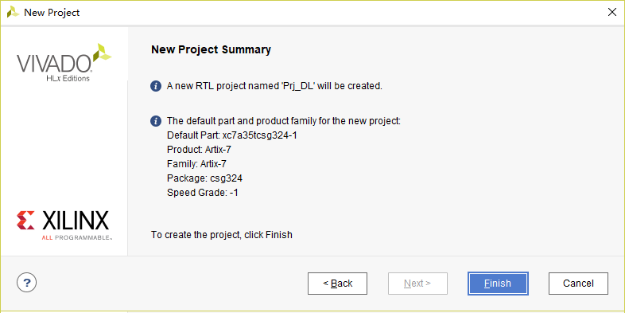

器件选择需要跟硬件一致,本专栏采用Family:Artix-7,Package:csg324,具体型号为xc7a35tcsg324-1;

最后核对相应工程信息,检查无误后点击Finish即可进入工程操作界面

到此,创建完成!

0x01 功能电路的创建

A)创建功能电路有两种方法,本专栏介绍方法一:利用verilog语言描述设计电路。

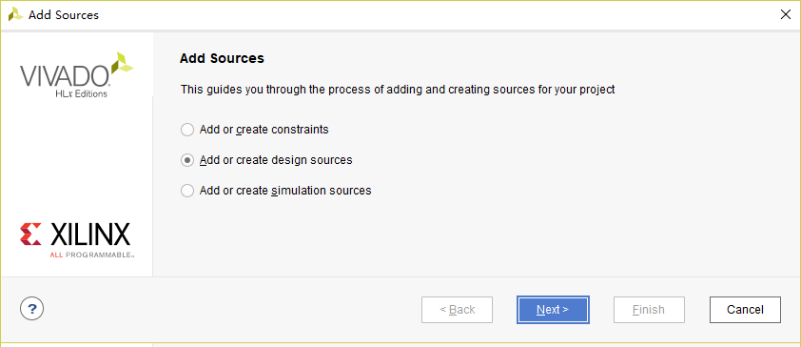

点击左边Flow Navigator中,PROJECT MANAGER中Add Sources,(或者点击Source窗口中“Add Sources”按钮或快捷键Alt+A)

在对话框中选中design sources类型后点击next,

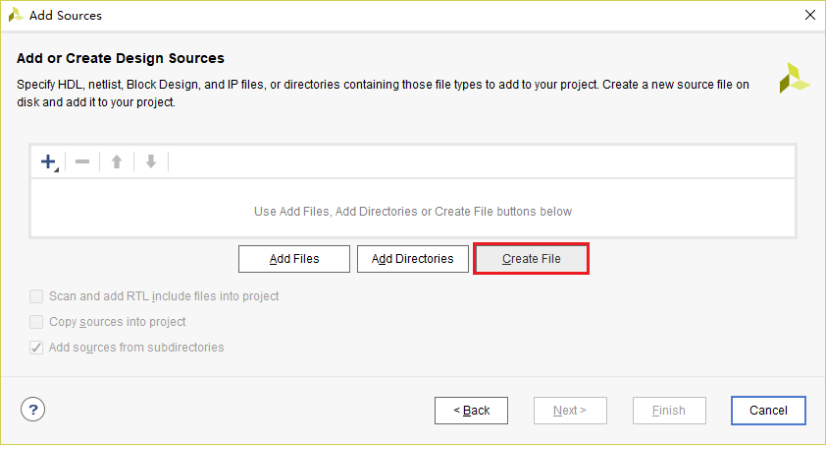

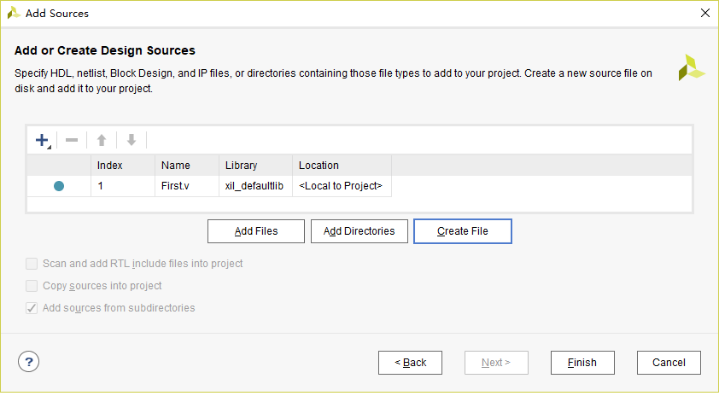

在对话框中点击create按钮,

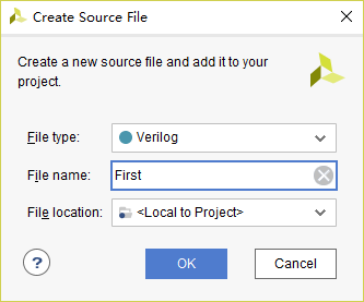

在对话框中设定文件名之后

对话框会自动变成如图所示

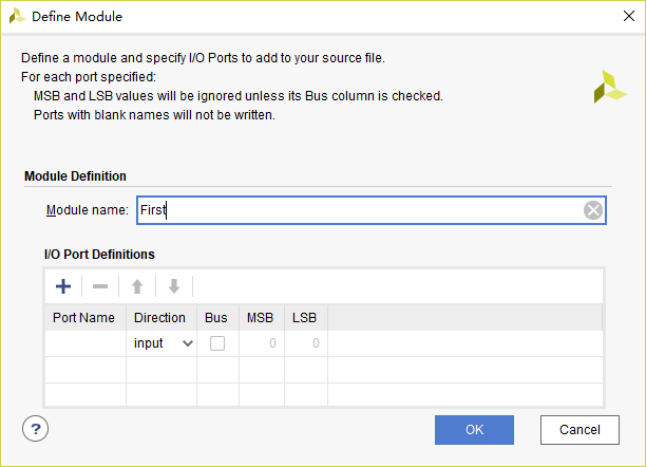

点击Finish后会自动出现如图的引脚配置。

值得一提的是,本篇博客旨在演示如何实施基本步骤操作,因此先做原理仿真,不会深入讲解。

这里可以直接点击OK并确认跳过;

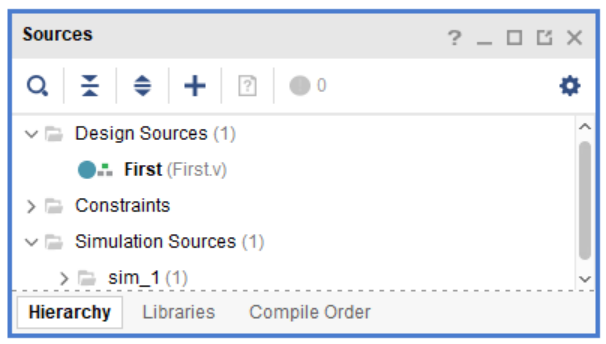

操作区的源码列表自动update后如图:

图 1.12

B)点击First.v,编辑Verilog文件,保存。

module First( input wire a, input wire b, output wire [2:0] z );

assign z[0] = a&b;

assign z[1] = a|b;

assign z[2] = a^b;

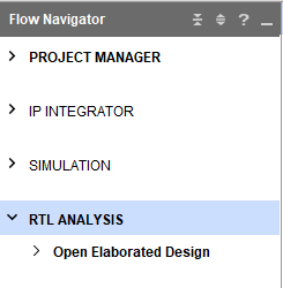

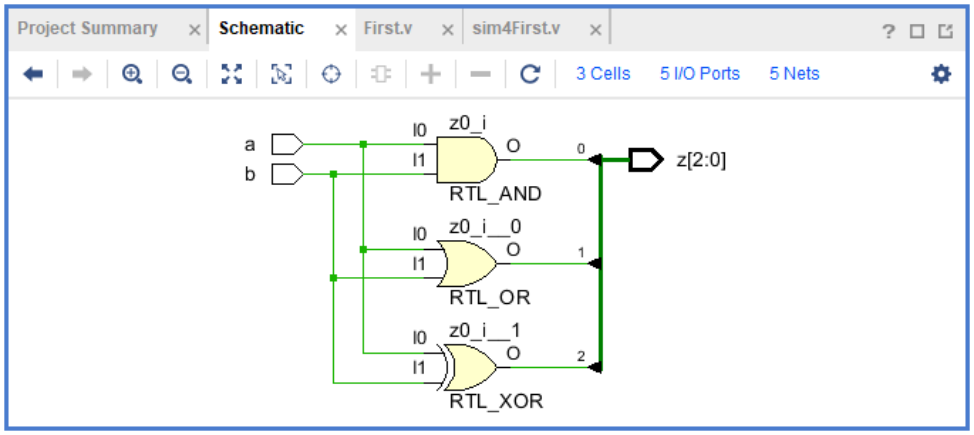

endmoduleC)点击Flow Navigator中的RTL ANALYSIS的Open Elaborated Design,

如图:

自动生成器件原理图,如图:

0x02 添加仿真激励程序

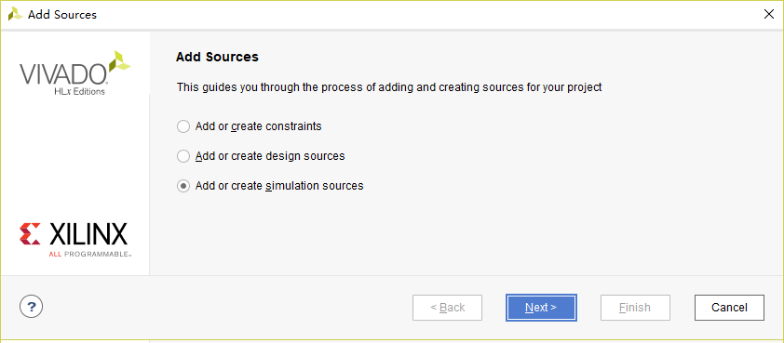

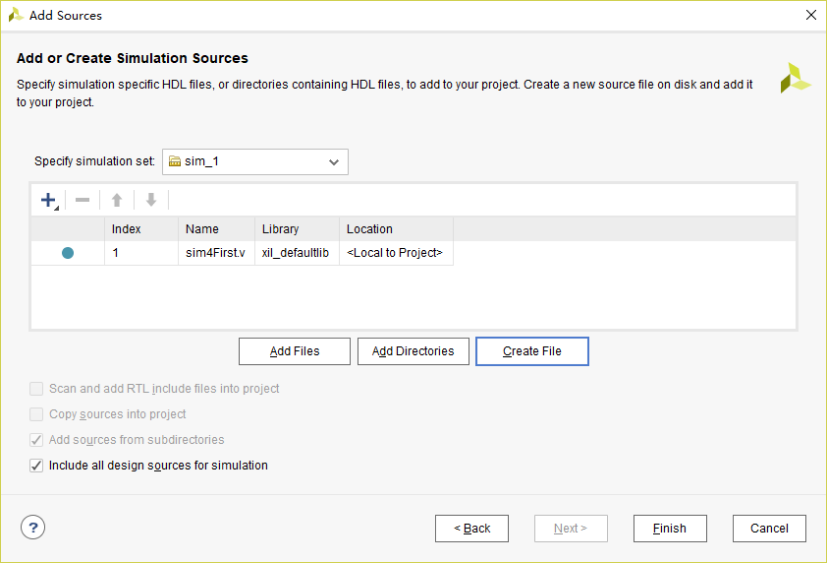

依照第2步A内容,点击左边Flow Navigator中,PROJECT MANAGER中Add Sources,(或者点击Source窗口中“Add Sources”按钮或快捷键Alt+A);

在如图对话框中选中simulation sources类型后点击next:

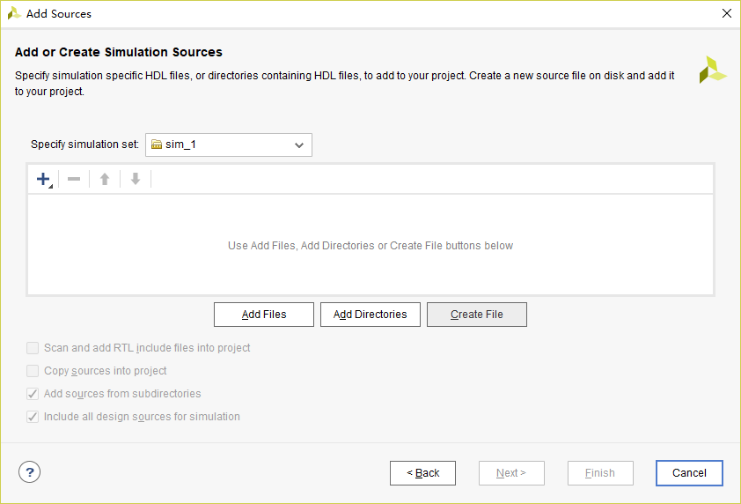

接着在话框中点击create按钮:

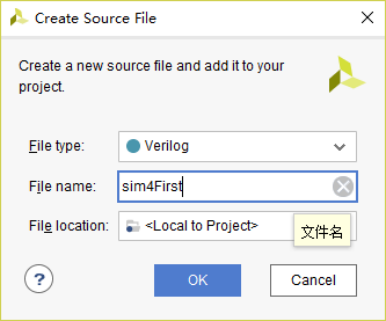

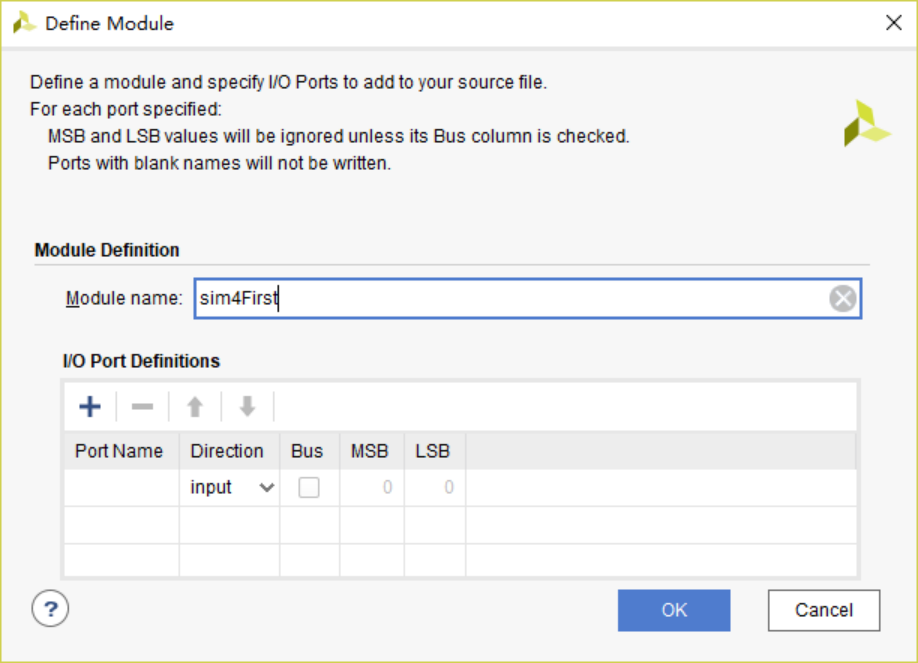

在如图对话框中设定文件名后:

对话框会自动变成如图所示:

点击Finish后会自动出现如图示意的引脚配置:

可以直接点击OK并确认跳过。

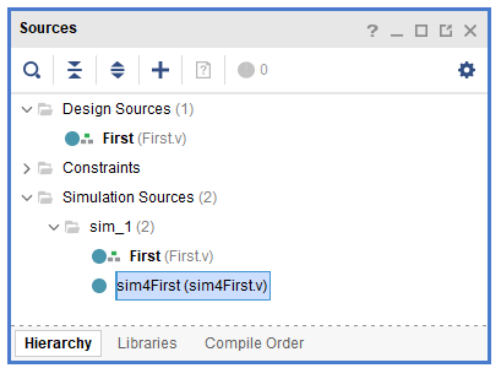

操作区的源码列表自动update后如图:

编辑sim4First.v,加入仿真输入信号和时序。

`timescale 1ns / 1ps

module sim4First( );

reg a;

reg b;

wire [2:0] z;

First uut( .a(a), .b(b), .z(z) );

always begin

a = 0; b = 0; #100;

a = 1; b = 0; #100;

a = 0; b = 1; #100;

a = 1; b = 1; #100;

end

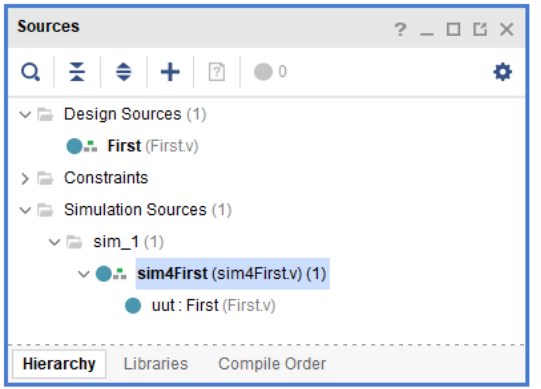

endmodule保存后,操作区的源码列表会自动update,得结构如图:

0x03 观察记录仿真波形

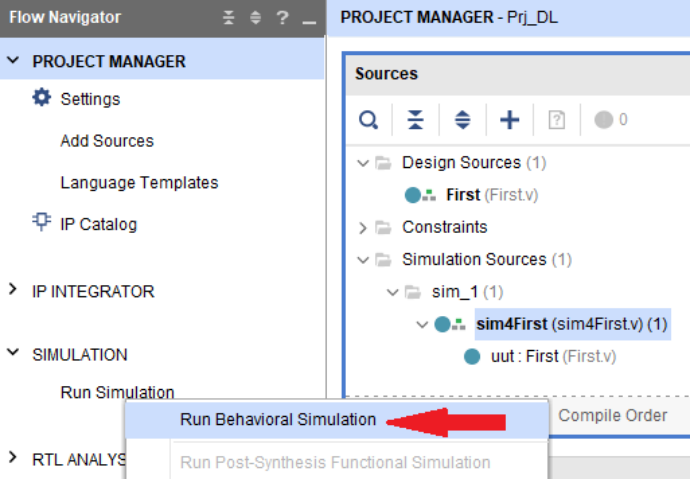

点击Flow Navigator – SIMULATION – Run Simulation,如图:

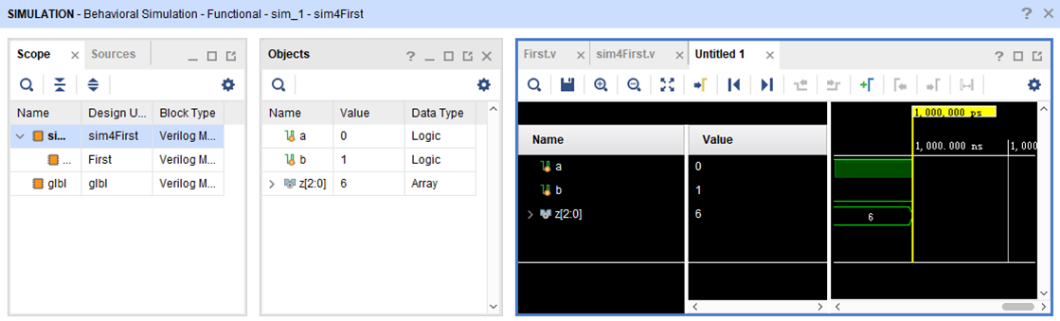

进入仿真状态,如图:

注意此时工具栏的变化,如图:

![]()

点击![]() 按钮,将仿真时间点切换至开始。

按钮,将仿真时间点切换至开始。

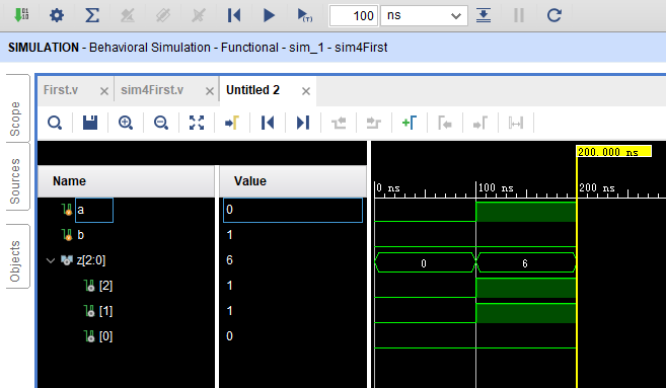

由于仿真文件中我们加了时间间隙为#100ns,为仿真的简便起见,我们将运行时间片设为100ns,如图:

![]()

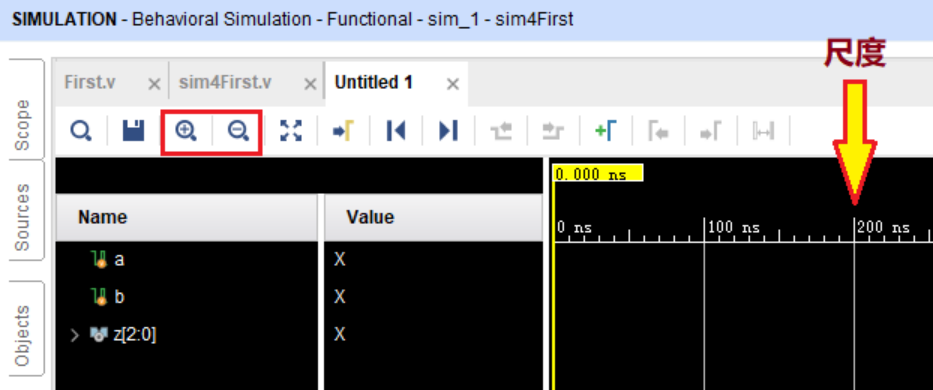

为了观察方便,运行前点击![]() 将波形时间窗调整至合适的尺度,如图:

将波形时间窗调整至合适的尺度,如图:

点击![]() ,观察输出波形,局部效果如图:

,观察输出波形,局部效果如图:

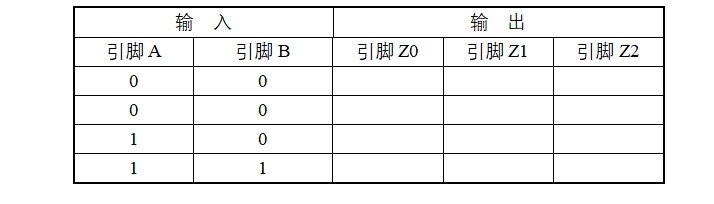

可以进一步来验证,根据波形,记录输出引脚状态至表,检验真值表与逻辑电路的对应关系。

Ⅲ. 通过实验板观察与验证

0x00 添加硬件约束文件

本篇博客的目的之一,也是为电路的输入输出配置合适的开发板资源。有两种方法可以添加约束文件:

- 一是可利用Vivado 中IO planning 功能;

- 二是可以直接新建XDC 的约束文件,手动输入约束命令。

a、先来看第一种方法,利用IO planning。

a.1、点击Flow Navigator 中Synthesis 中的Run Synthesis,先对工程进行综合。

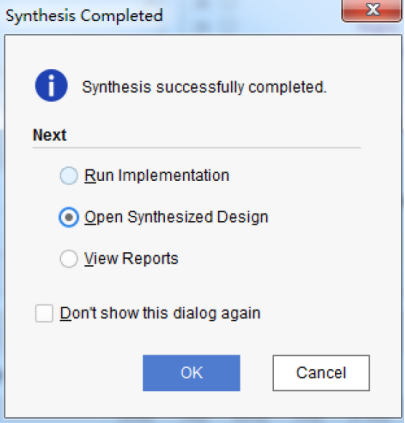

a.2、综合完成之后,选择Open Synthesized Design,打开综合结果。

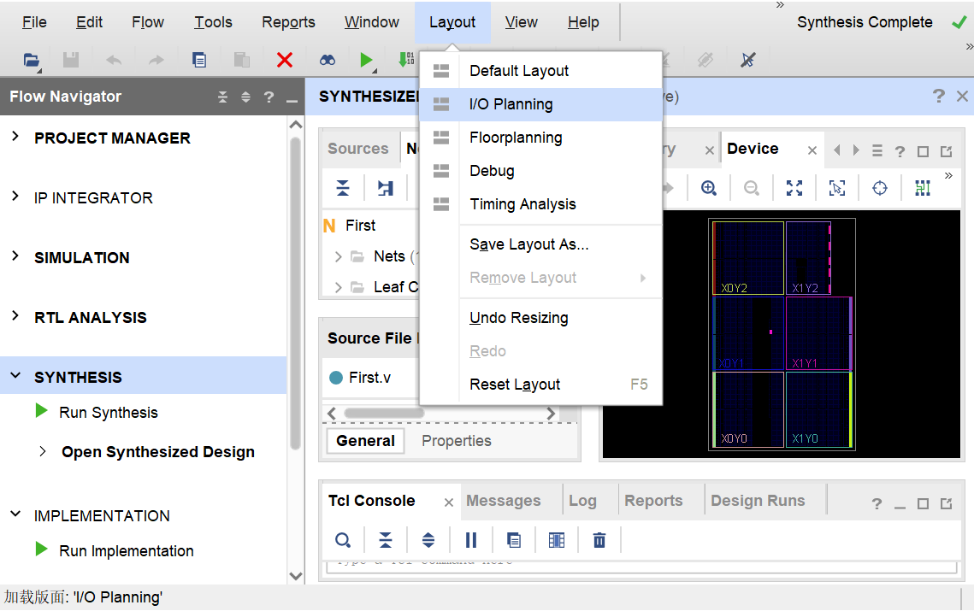

a.3、此时应看到如下界面,如果没出现如下界面,在图示位置的layout 中选择IO Ports一项。

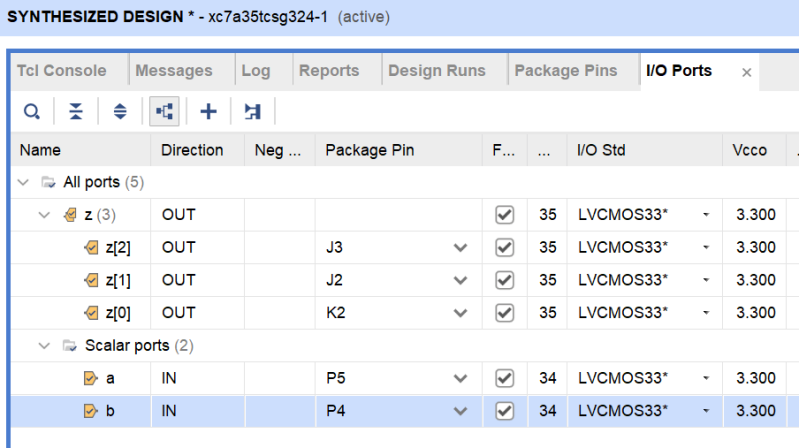

a.4、在右下方的选项卡中切换到I/O ports 一栏,并在对应的信号后,输入对应的FPGA 管脚标号(或将信号拖拽到右上方Package 图中对应的管脚上),并指定I/O std。具体的FPGA约束管脚和IO 电平标准,可参考对应板卡的用户手册或原理图)。

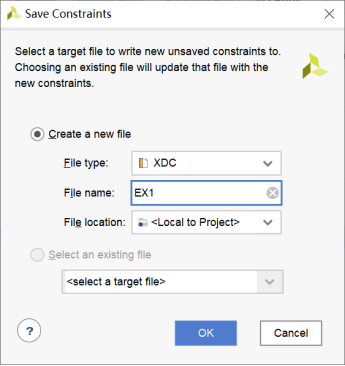

a.5、完成之后,点击左上方工具栏中的保存按钮,工程提示新建XDC 文件或选择工程中已有的XDC 文件。在这里,我们要Create a new file,输入File name,点击OK 完成约束过程。

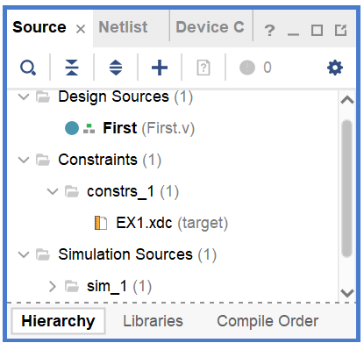

a.6、此时,在Sources 下Constraints 中会找到新建的XDC 文件。

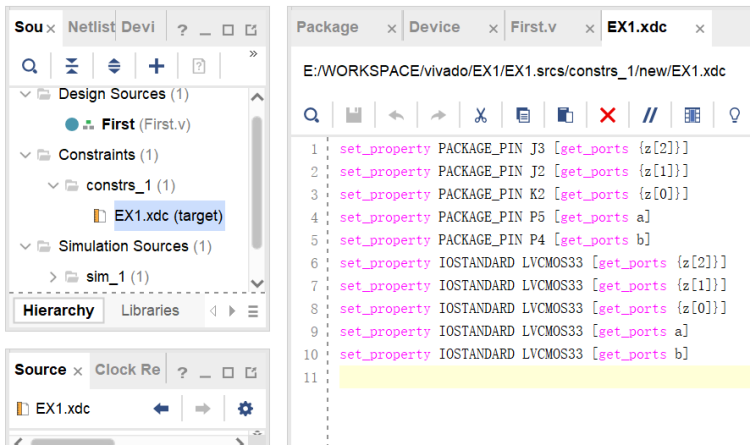

b、如何利用第二种方法添加约束文件。

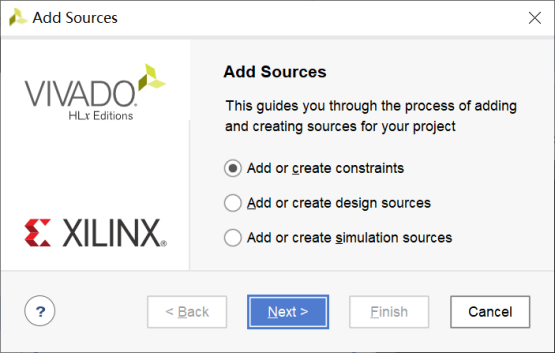

b.1、点击Add Sources,选择第一项Add or Create Constraints 一项,点击Next。

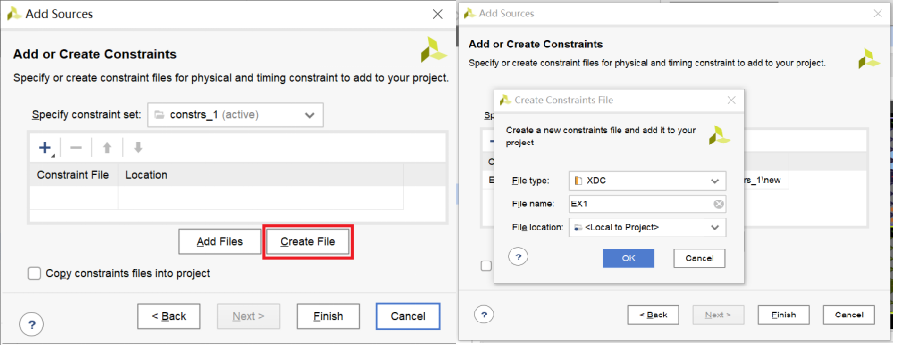

b.2、点击Create File,新建一个XDC 文件,输入XDC 文件名,点击OK。点击Finish。

b.3、双击打开新建好的XDC 文件,并按照如图37所示规则,输入相应的FPGA 管脚约束信息和电平标准。

本实验电路属于简单的组合逻辑电路,因此可以跳过时序约束设计。

若要实现时序约束,按以下步骤完成。

a、在综合完成后打开选择Open Synthesis Design,或者从Flow Navigator中选择Open Synthesis Design。

b、在Flow Navigator 中选择Synthesis > Synthesized Design > Edit Timing Constraints,打开时序约束界面,为电路添加时钟并配置引脚,进而完成时序约束。

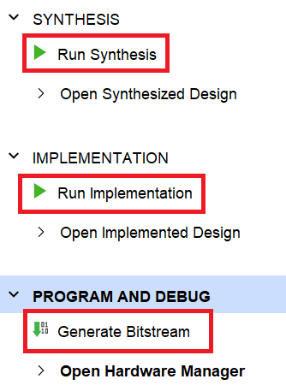

0x01 电路生成

设计网表综合SYNTHESIS和硬件实施IMPLEMENTATION,并生成二进制流文件。

0x02 实验板使用

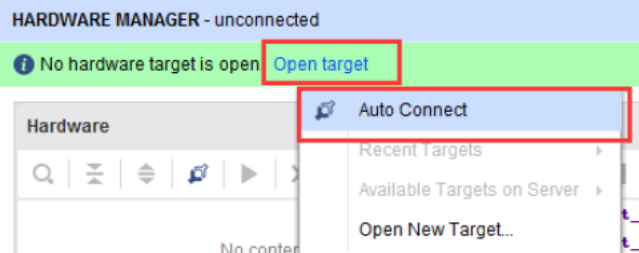

a、将EGO1实验板通过USB连接电脑,打开实验板电源。

b、点击Flow Navigator 中Open Hardware Manager 一项,进入硬件编程管理(HARDWARE MANAGER),选择Auto Connect连接到板卡,(也可在Flow Navigator 中展开Hardware Manager,点击Open Target,选择Auto Connect连接到板卡)

如下图:

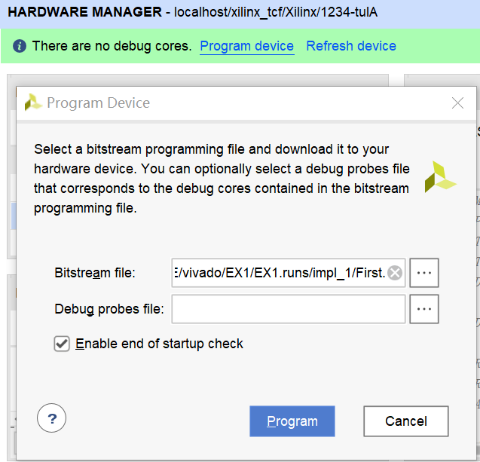

c、连接成功后,在目标芯片上右击,选择“Program Device”。在弹出的对话框中“Bitstream File” 一栏已经自动加载本工程生成的比特流文件,点击“Program”对FPGA芯片进行编程,

如图:

成功下载后,目标板芯片会显示“Programmed”,如图:

d、拨动开关SW7和SW6,观察LD2灯组中2-0的状态