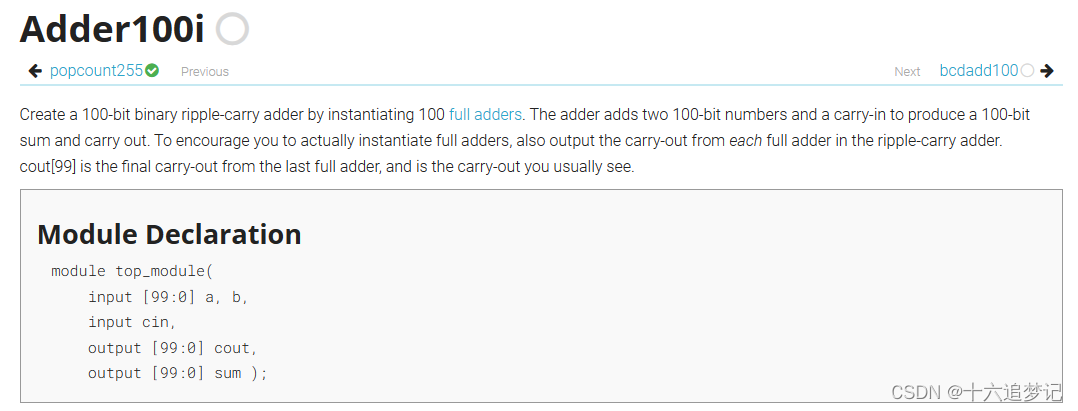

题目:

Create a 100-bit binary ripple-carry adder by instantiating 100 full adders. The adder adds two 100-bit numbers and a carry-in to produce a 100-bit sum and carry out. To encourage you to actually instantiate full adders, also output the carry-out from each full adder in the ripple-carry adder. cout[99] is the final carry-out from the last full adder, and is the carry-out you usually see.

解题:

module top_module(

input [99:0] a, b,

input cin,

output [99:0] cout,

output [99:0] sum );

integer i;

reg cined;

always@(*)begin

cined=cin;

for(i=0;i<100;i++)

begin

sum[i]=cined^a[i]^b[i];

cout[i]=(a[i]&b[i])|((a[i]^b[i])&cined);

cined=cout[i];

end

end

endmodule

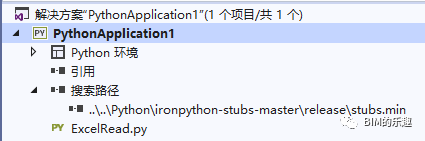

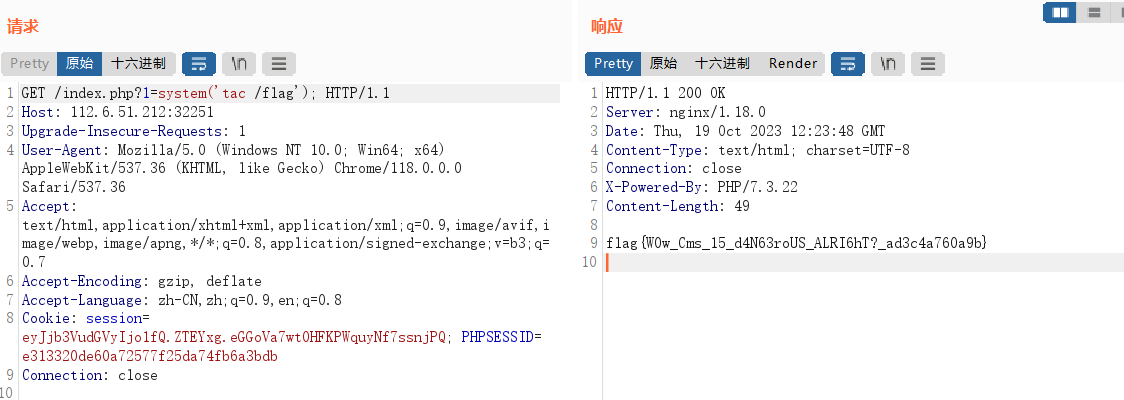

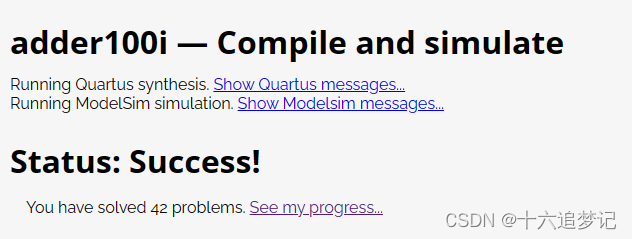

结果正确:

说明:

为什么需要reg cined?

输入端口在 Verilog 中是不允许赋值的,因为它是顶层模块的输入端口,需要从模块外部提供数据。因此创建了一个cined(内部的变量)来代替 “cin”,然后在 always 块的行为语句内使用这个变量。这样做可以避免直接修改输入端口的值。