【安全硬件】Chap.4 如何插入一个硬件木马到芯片的时序逻辑电路的漏洞里?如何构建可信赖的状态机?

- 前言:硬件木马

- 1. 时序逻辑电路中的设计漏洞Design Vulnerabilities

- 序列检测器的设计漏洞——以智能门锁的虚位密码漏洞为例

- 易受攻击的状态机写法Vulnerable State Machine Specification

- 第一种漏洞:设置一个“隐藏密码”

- 构建可信赖的智能门锁状态机写法

- 第二种漏洞:使得状态机失效,无法正常检测密码

- 2. Design for Trust Techniques

- 设计混淆 Design Obfuscation

- 3. 时序逻辑电路的一般设计流程与卡诺图化简

- 时序逻辑电路的状态机设计过程

前言:硬件木马

硬件木马(hardware Trojan)

- 对现有电路元件的恶意添加或修改。 A malicious addition or modification to the existing circuit elements.

硬件木马能做什么?What can hardware Trojans do?

- 更改功能(Change the functionality)

- 降低可靠性(Reduce the reliability )

- 泄露有价值的信息(Leak valuable information)

1. 时序逻辑电路中的设计漏洞Design Vulnerabilities

时序逻辑电路中,任意时刻的输出信号不仅与当时刻的输入有关,而且与电路原来的状态有关。

序列检测器的设计漏洞——以智能门锁的虚位密码漏洞为例

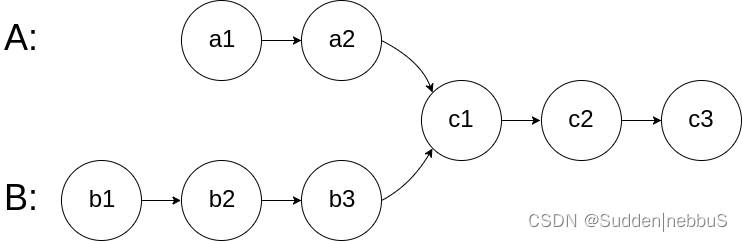

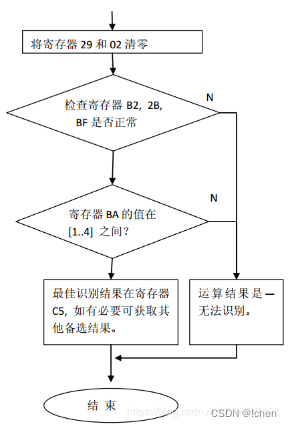

有些智能门锁具备虚位密码的功能,可以在正确密码的前面和后面加上任意数字,只要中间有连续正确的密码就可开门。小明设计了一个序列检测器实现虚位密码解锁功能,即在海量输入下检测对其中一串敏感的密码进行识别。

-

序列检测器检查二进制数据位流,并在检测到特定序列时将输出信号置1。

-

有限状态机(Finite-state machine)将读取一系列输入。对于给定的输入,每个状态指定要切换到哪个状态,并给出输出。

易受攻击的状态机写法Vulnerable State Machine Specification

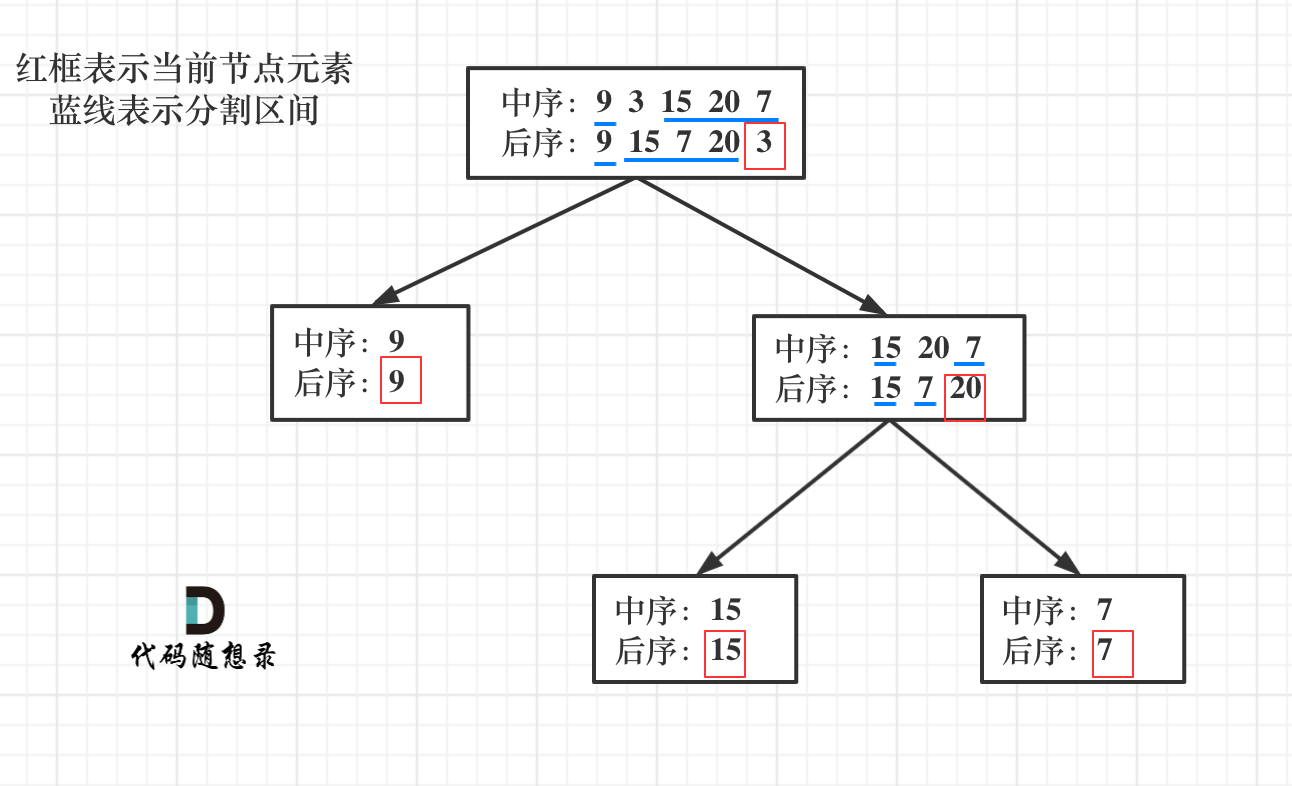

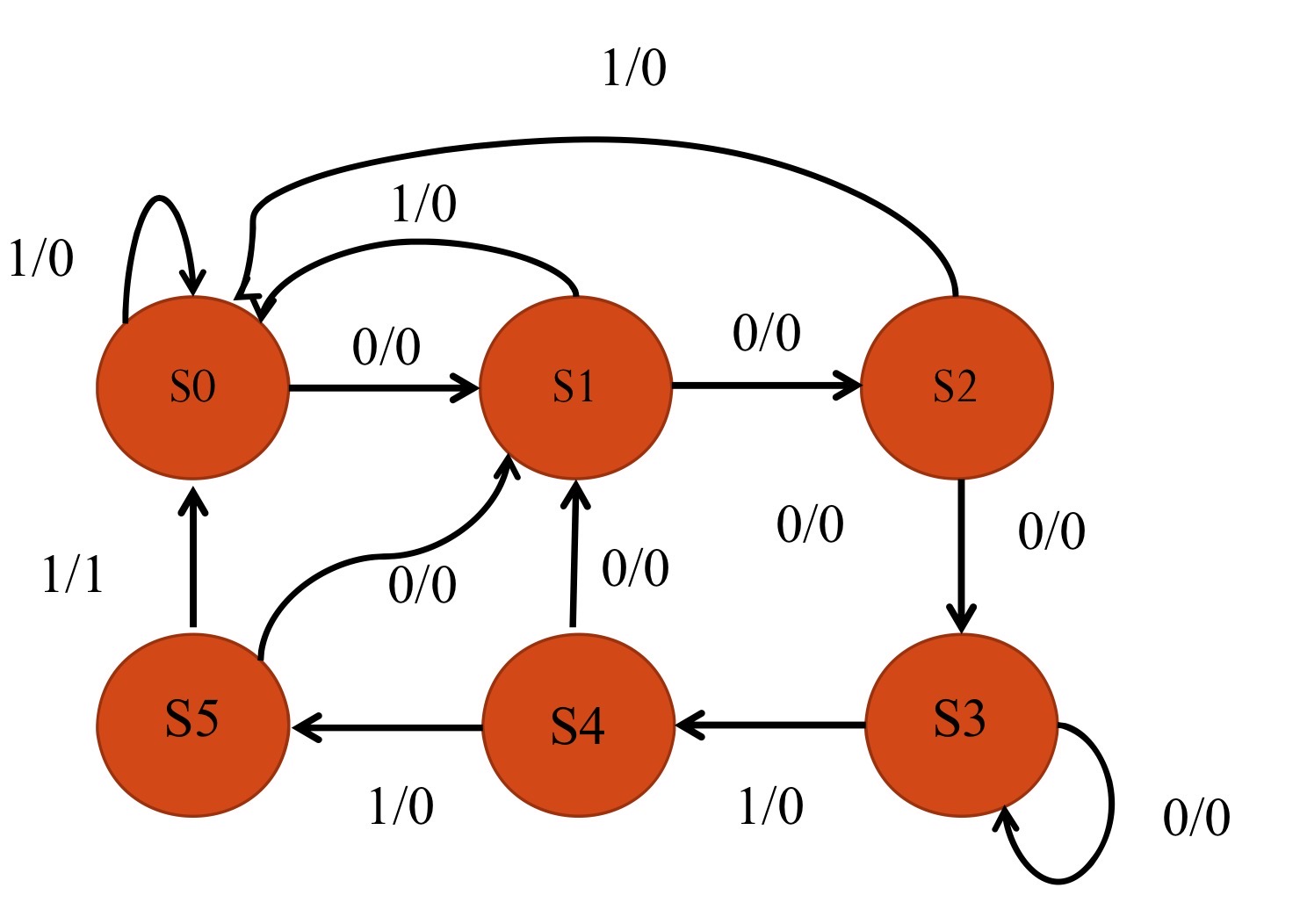

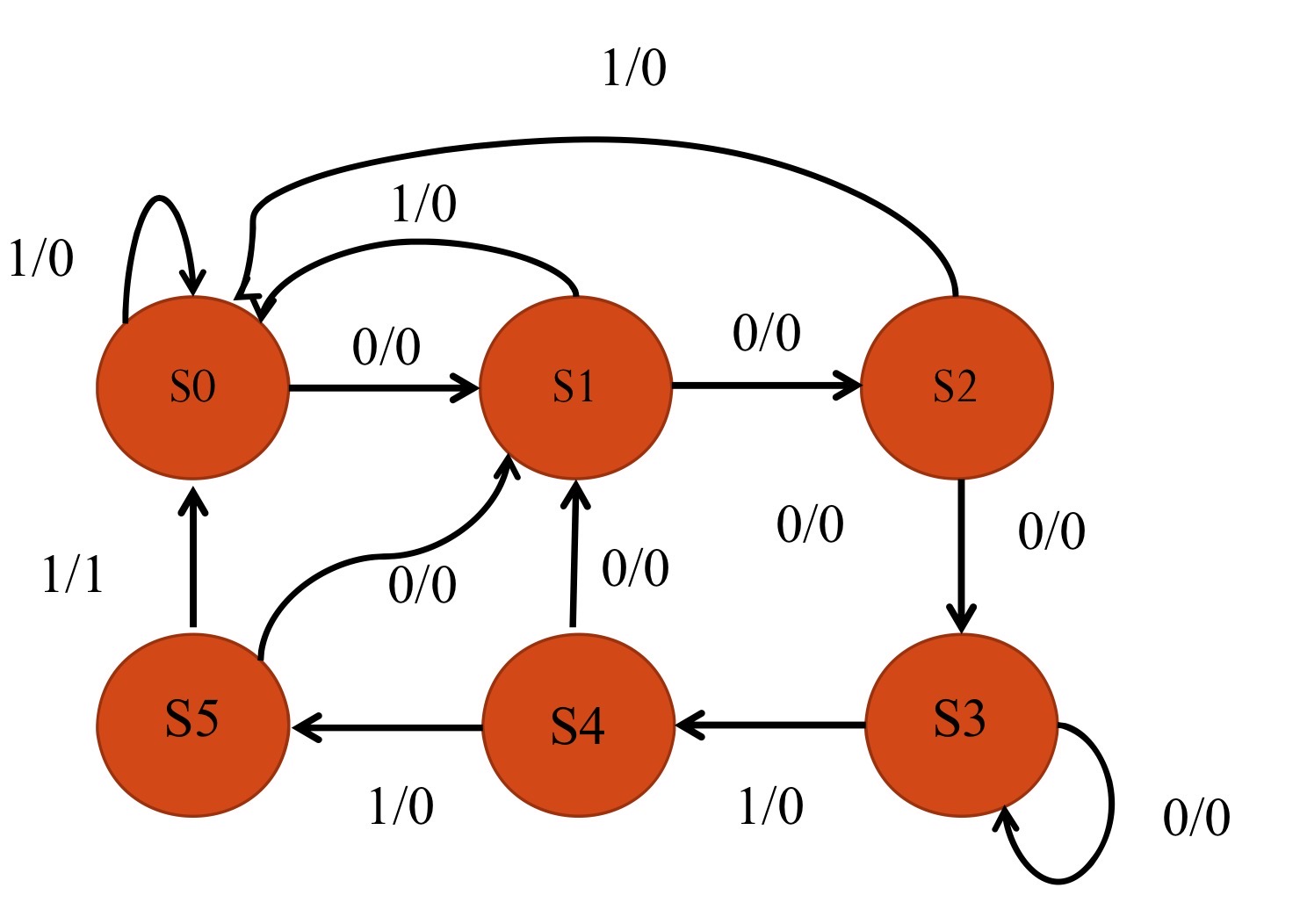

假设用户门锁的解锁密码是000111,小明设计了一个序列检测器如下所示:

当输入信号的其中一段为000111时:

- 状态跳转顺序为 S 0 → S 1 → S 2 → S 3 → S 4 → S 5 → S 0 S_0 \rightarrow S_1 \rightarrow S_2 \rightarrow S_3 \rightarrow S_4 \rightarrow S_5 \rightarrow S_0 S0→S1→S2→S3→S4→S5→S0

- 在 S 5 → S 0 S_5 \rightarrow S_0 S5→S0的时候输出“1”产生一个高电平

- 状态一共有6个,需要编码000,001,010,011,100,101;一共三位,共需要3个触发器(flip-flop)才能

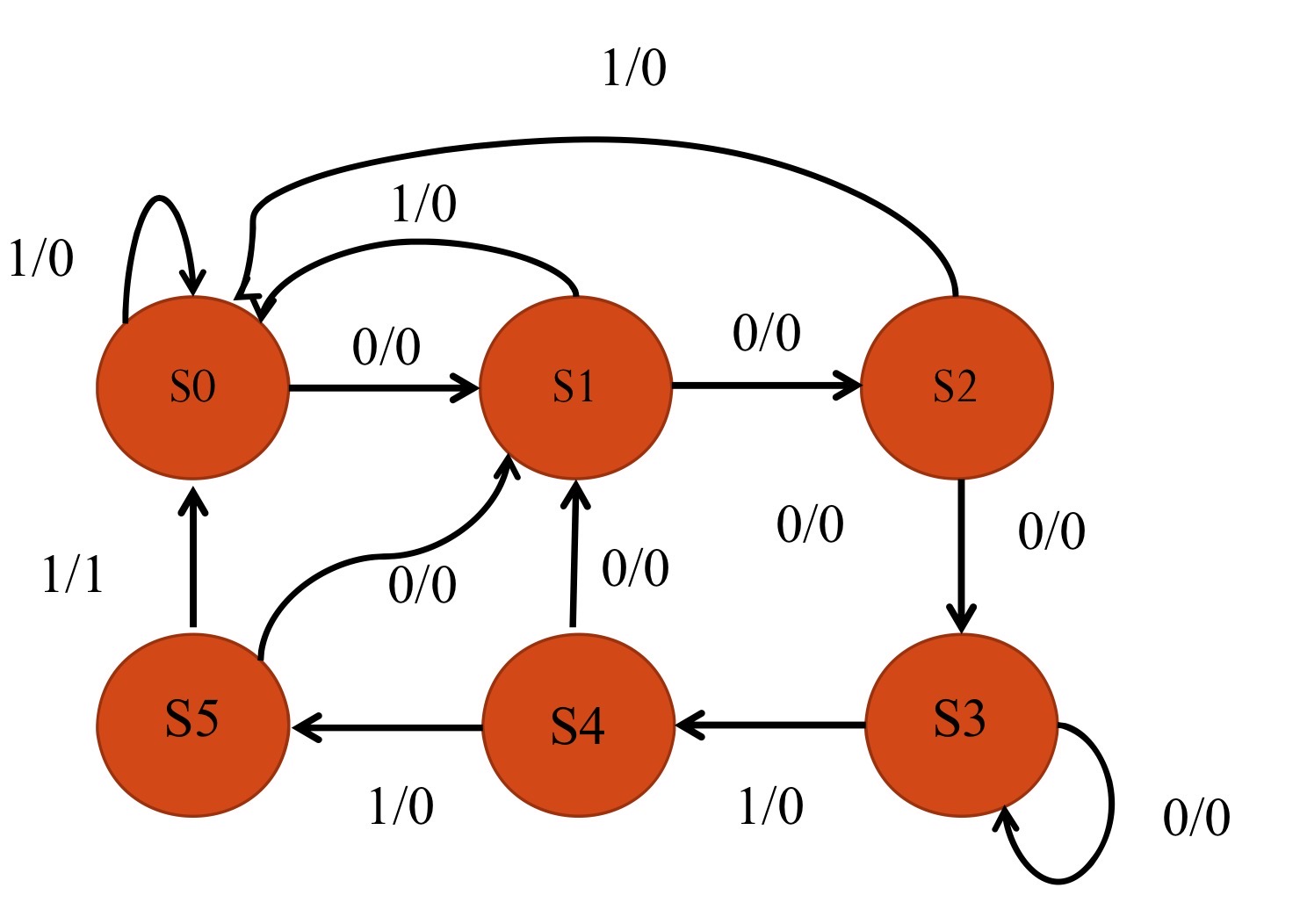

第一种漏洞:设置一个“隐藏密码”

有一个小偷想越过这个密码,设置一个“隐藏密码”可以开启门锁,也就是说,需要在不破坏正常情况下此状态机跳转的同时,在硬件上植入一个木马。分析原设计发现了漏洞如下:

- 3个触发器编码的6个状态,其中是可以再编写两个状态的,可以通过增加其他状态的方式设置“后门”。

-

S

0

S_0

S0状态和

S

3

S_3

S3状态都可以跳转到自身,可以利用这个漏洞,破开其中一个(这里选择

S

0

S_0

S0)跳转到自身的状态,加一个中间的状态。

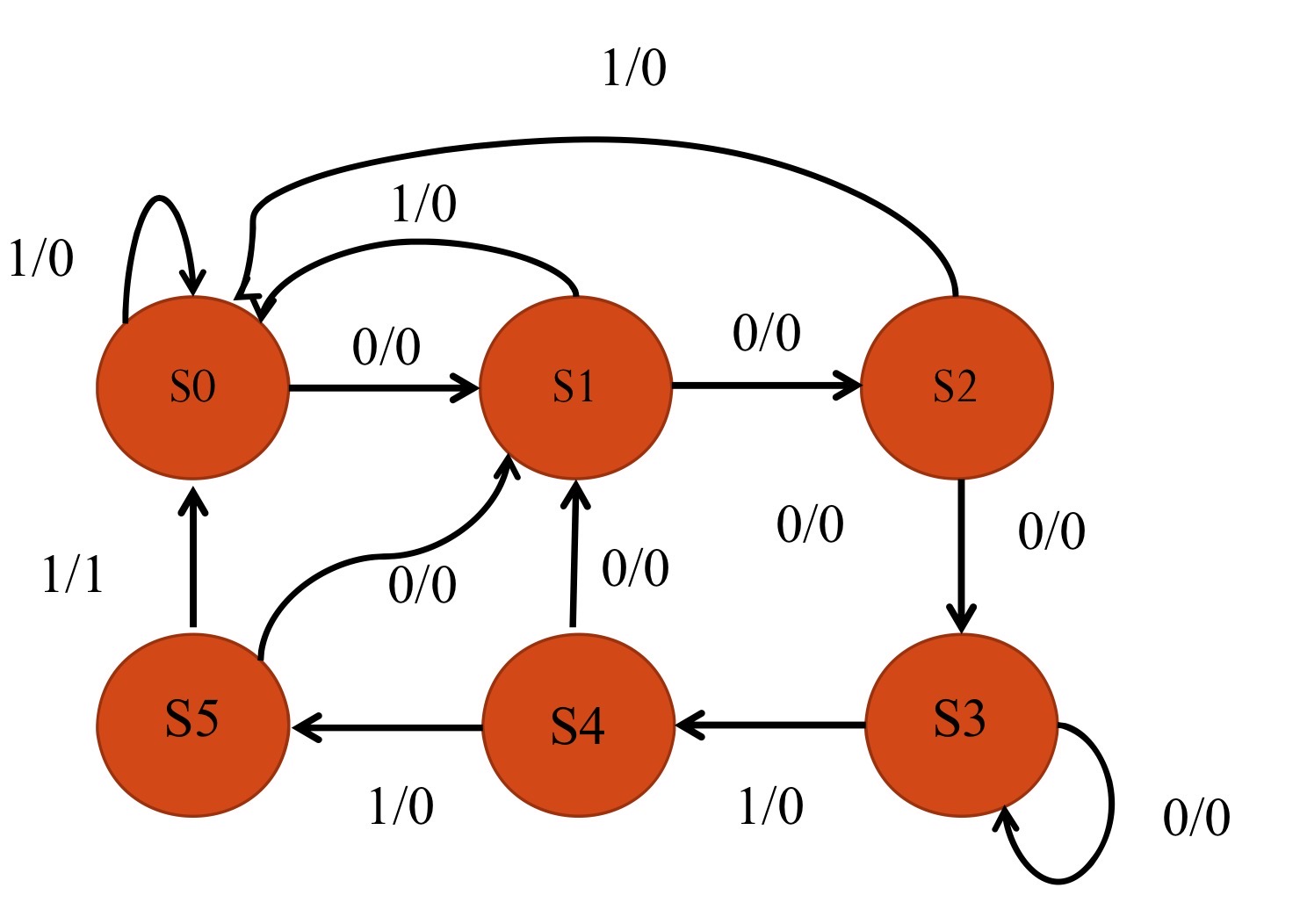

于是小偷在硬件上通过接线又植入了一个木马(过程这里不叙述了),改变了状态机的跳转,如下图所示:

图1 原设计 图1 原设计

|

图2 木马1:设置一个“隐藏密码” 图2 木马1:设置一个“隐藏密码”

|

分析这个状态机不难发现,除了用户密码“000111”还植入了一个隐藏密码“111111”,直接给小偷留了个后门。因为3个触发器编写8个状态不成问题,所以用户在正常使用的时候很难发现硬件木马。

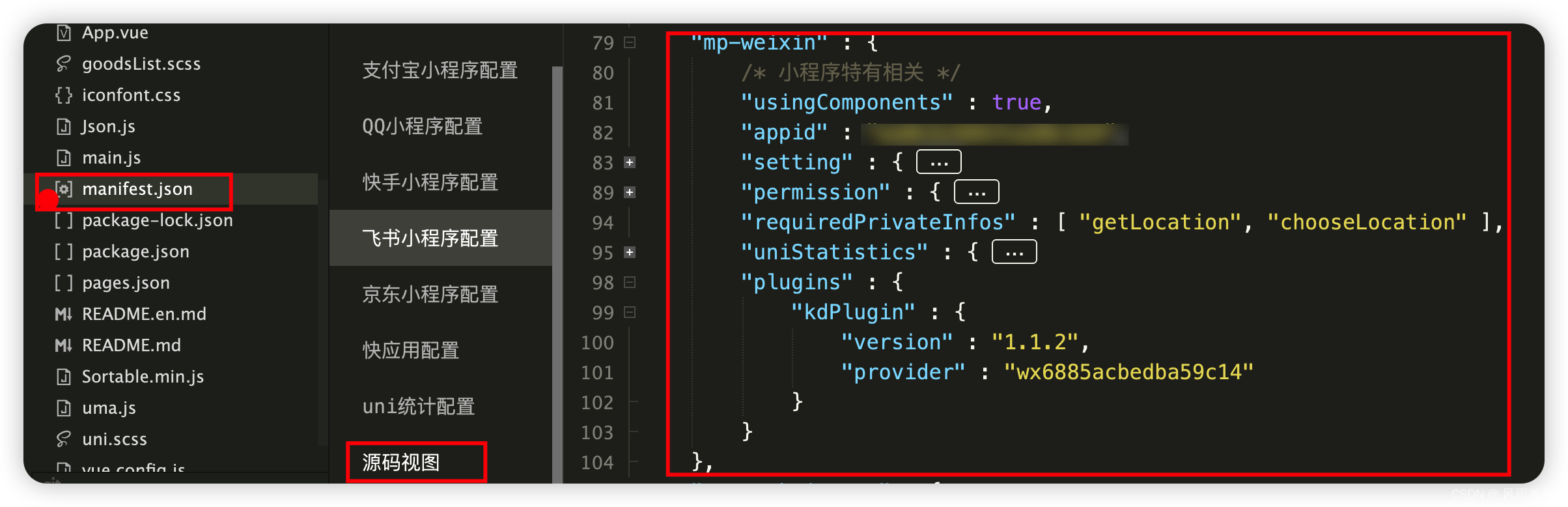

构建可信赖的智能门锁状态机写法

就具备虚位密码的智能门锁这个例子而言,为了构建可信赖的状态机可以实行以下规范:

- 不留空余状态,不给硬件木马给状态机添加状态的机会;

- 分辨所有状态机可能存在的状态的跳转,包括冗余状态,设计让冗余状态不论输入什么都跳转到初始化状态。

- 在构建可信赖的状态机之后,再分析哪些状态有歧义容易受到攻击造成安全隐患。

构造的状态机如下所示,、

图1 原设计 图1 原设计

|

图2 Design for Trust可信赖状态机 图2 Design for Trust可信赖状态机

|

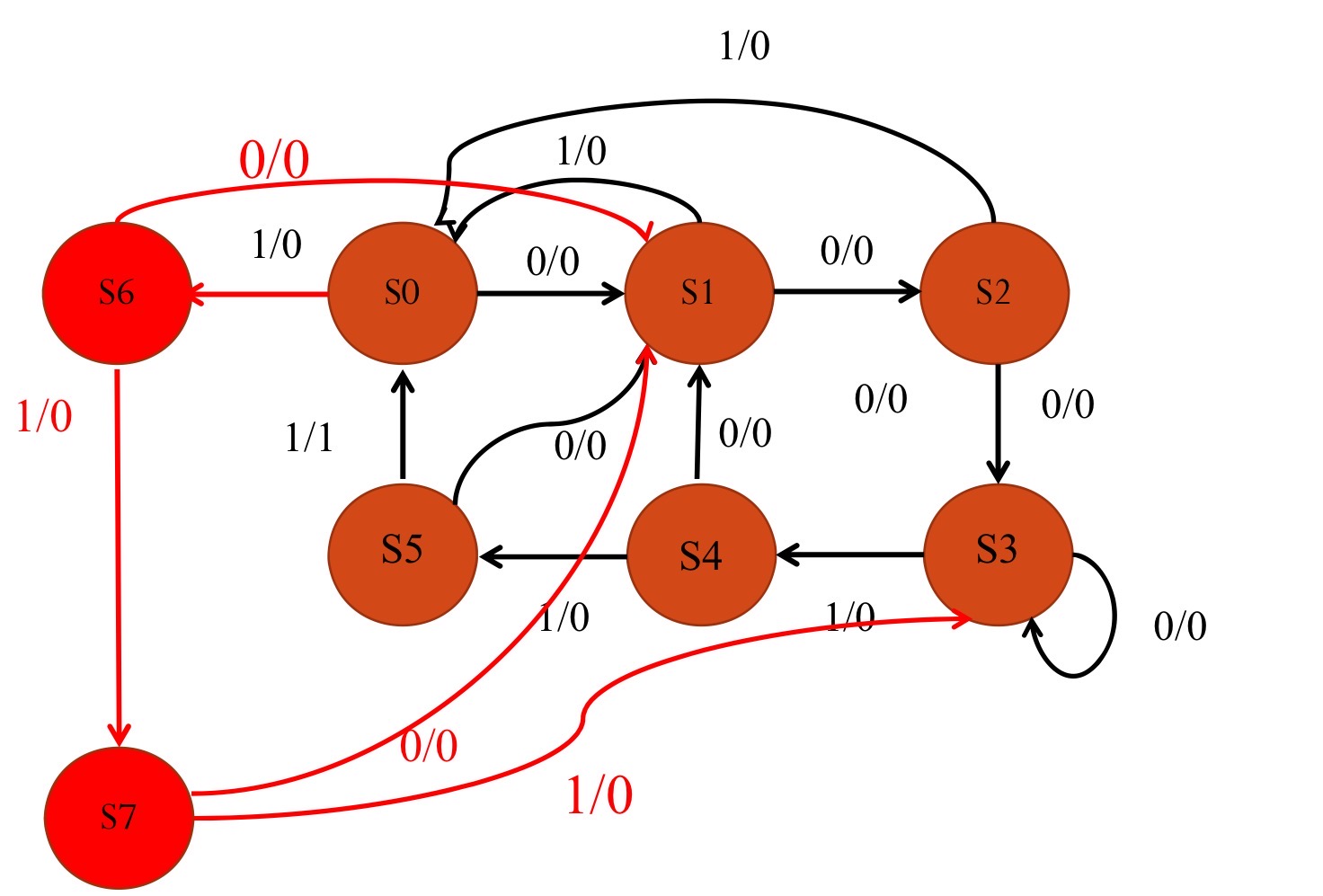

第二种漏洞:使得状态机失效,无法正常检测密码

隐藏密码的功能:在正确6位密码前后可以输入任意的乱码,只要中间的6位密码是正确的就可以开门,这样就避免了输入密码开门时刻意遮掩的窘境。

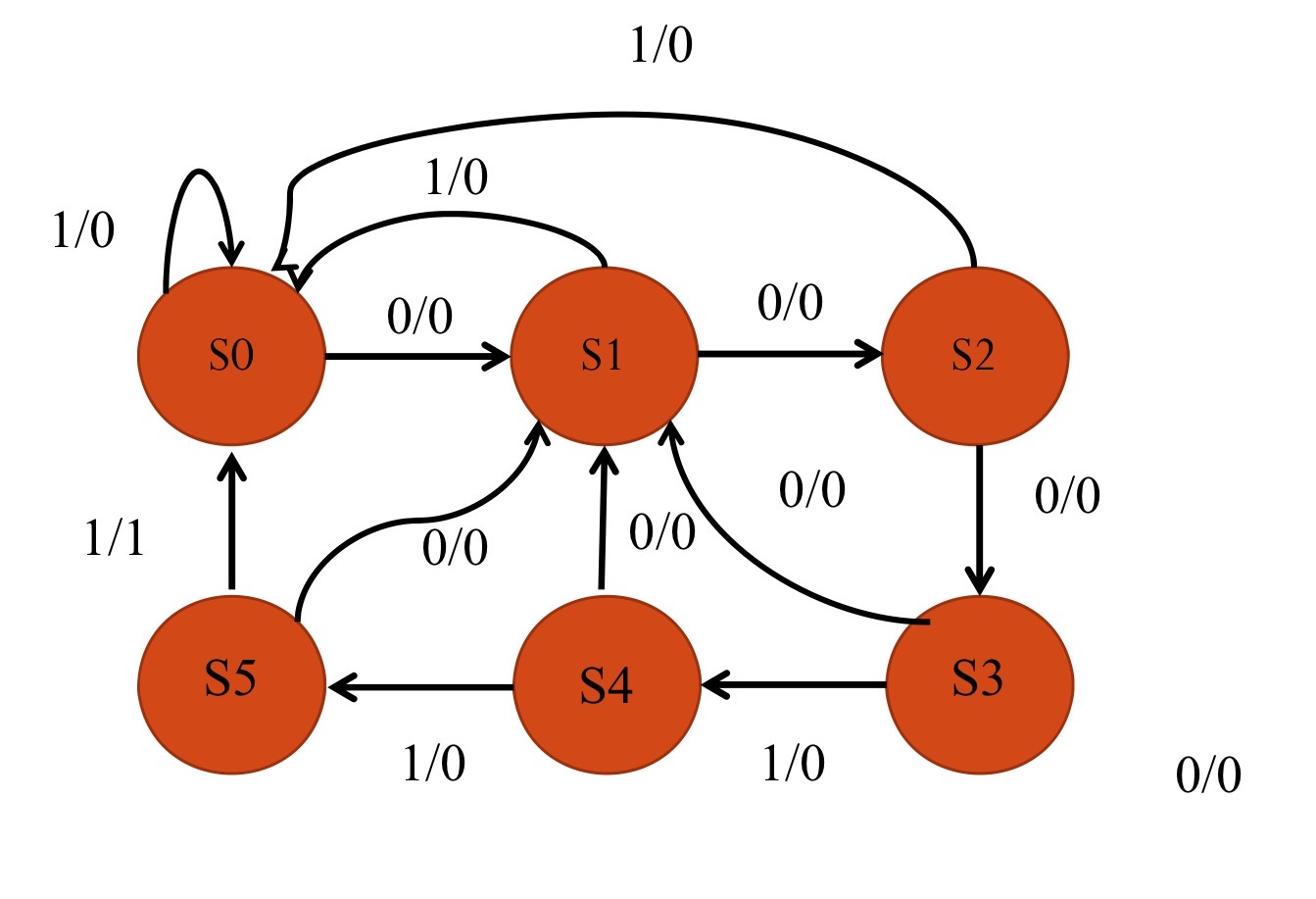

有一个人想让这个密码失效,输入隐藏密码也不能打开门锁,也就是说,破坏了正常情况下此状态机跳转,在硬件上植入一个木马。分析原设计发现了漏洞如下:

-

S

0

S_0

S0状态和

S

3

S_3

S3状态都可以跳转到自身,可以利用这个漏洞,破开其中一个(这里选择

S

3

S_3

S3)跳转到自身的状态,让其无法跳转到自身。

于是小偷在硬件上通过接线又植入了一个木马(过程这里不叙述了),改变了状态机的跳转,如下图所示:

图1 原设计 图1 原设计

|

图2 木马2:使得状态机失效,无法正常检测密码 图2 木马2:使得状态机失效,无法正常检测密码

|

分析插入木马2后的状态机:

-

正常直接输入000111时,状态跳转顺序为 S 0 → S 1 → S 2 → S 3 → S 4 → S 5 → S 0 S_0 \rightarrow S_1 \rightarrow S_2 \rightarrow S_3 \rightarrow S_4 \rightarrow S_5 \rightarrow S_0 S0→S1→S2→S3→S4→S5→S0,在 S 5 → S 0 S_5 \rightarrow S_0 S5→S0的时候输出“1”产生一个高电平。

-

当你尝试输入00001111,状态跳转顺序为 S 0 → S 1 → S 2 → S 3 → S 1 → S 0 → S 0 → S 0 S_0 \rightarrow S_1 \rightarrow S_2 \rightarrow S_3 \rightarrow S_1 \rightarrow S_0 \rightarrow S_0 \rightarrow S_0 S0→S1→S2→S3→S1→S0→S0→S0,输出低电平没有变化,即虽然输入密码正确为“000111”,但是门锁没有打开。

-

破坏了其中一条连线,让状态机失效,无法正常检测密码。

-

The circuits will not recognize the correct sequence if it was preceded by one or more zeros, so even if you’ve got a correct sequence then the state will stop will not recognize

-

so the circuit does not function as you tended

同样的,也可以构建可信赖的智能门锁状态机写法解决这个漏洞。

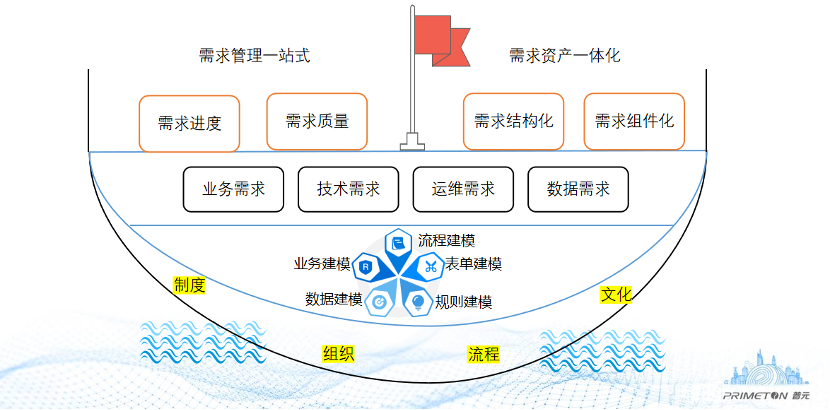

2. Design for Trust Techniques

Design for Trust是一种思想,使用预防性设计技术来克服硬件木马的漏洞。策略是构建可信赖的 IC电路,它完全按照要求进行设计逻辑,不多也不少包括电路中每个状态的全面规范(有时候为了安全性可能造成成本高昂且不切实际),有许多新兴技术可以通过以下方式提高硬件的安全性:

- 促进特洛伊木马检测方法,例如,通过插入额外的探测点,更容易分析敏感块的时间和功率。Facilitating Trojan detection methods for example by making it easier to analyze timing and power of sensitive blocks through the insertion of additional probing points

- 使用设计混淆技术防止特洛伊木马插入。Preventing Trojan insertion using design obfuscation techniques

- Including comprehensive specifications for every single state in the circuit may be costly and impractical

设计混淆 Design Obfuscation

Security against hardware Trojan through a novel application of design obfuscation

设计混淆,意味着创建原始设计的功能等效版本,这会使得设计更难理解以及不易被恶意修改。

以下图为例,使用额外插入的状态,正常操作时因为这些状态没有输入,所以无法到达,仅在特殊混淆操作模式下才被使用。

混淆状态空间(里面全是冗余的状态)的构造可以显着受益于给定电路中无法到达状态的确定,因为这些状态可以用于初始化或隔离状态空间。

3. 时序逻辑电路的一般设计流程与卡诺图化简

- 分析要解决的问题。什么信息需要被存储到内存里面,即选择可能的状态。

- 使用合适的设计表示来表述问题。画状态转换图用于描述系统的行为。(formulate the problem using a suitable design representation)

- 选实施的功能性模块,如触发器。(Choose implementation target)

- 按照步骤实施,逻辑综合导出触发器输入与输出的结构图,卡诺图化简成想要的形式(可能是两层括号的表达式方便控制延迟)、硬件描述语言verilog描述并用工具解释(Follow implementation procedure)。

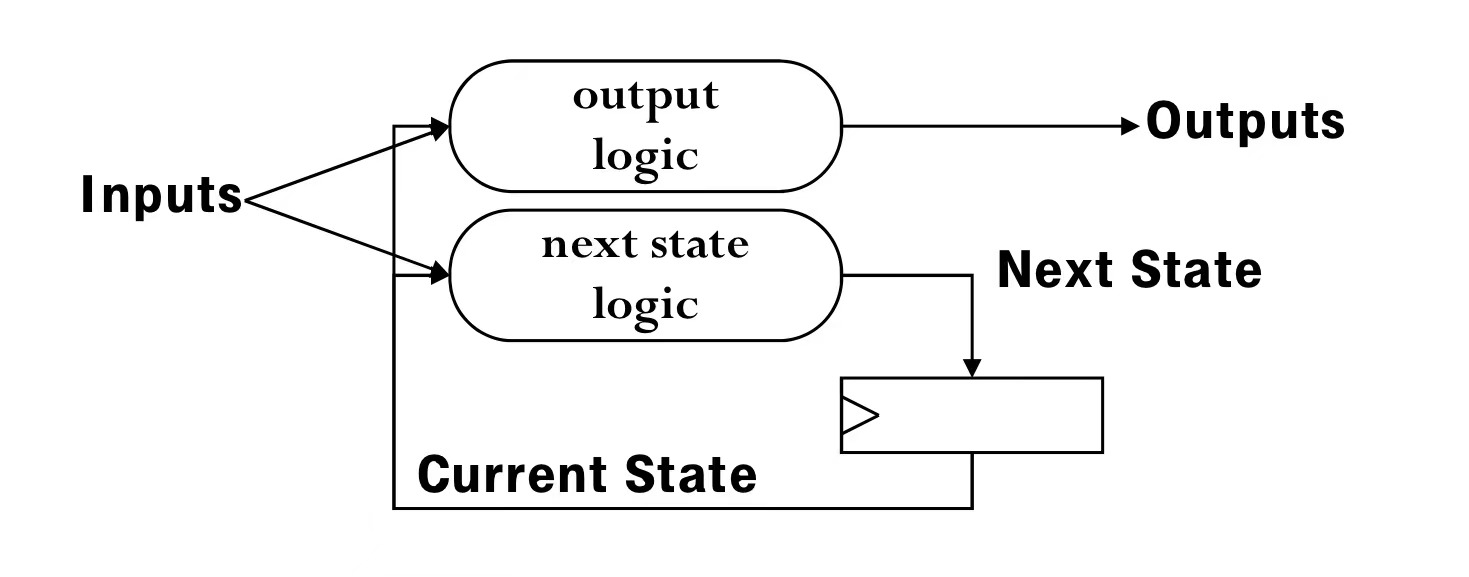

时序逻辑电路的状态机设计过程

- assign binary codes to states

- Generate the logic equations for the next state functions

- Generate the logic equations for output function (Identify is it Mealy or Moore machine)

- Map to a circuit