使用Vitis HLS源

AMD Vitis™ 高级综合(HLS)工具将C规范转换为寄存器传输级(RTL)实现,您可以将其合成到AMD设备中。你可以写CC、C++或SystemC中的规范,AMD设备提供了大规模并行与传统处理器相比,该体系结构在性能、成本和功耗方面都有优势。Vitis HLS的输出包括硬件描述语言中的RTL实现文件(HDL)格式,可以在Vivado合成中合成或打包为IP块以供使用来自IP目录。有关更多信息,请参阅《Vitis高级合成用户指南》(UG1399)。

使用模型生成器源

Model Composer是一种基于模型的设计工具,可实现快速的设计探索和通过自动代码生成加速AMD设备的生产。模型Composer是作为AMD工具箱构建的,适用于MathWorks Simulink®软件MATLAB®软件的附加产品,提供交互式图形环境用于建模、模拟、分析和验证系统级设计。可以使用模型生成器中的块在模型生成器中表达算法库以及用户导入的自定义块。Model Composer转换您的算法使用自动优化并利用高级Vitis HLS的合成工艺。使用Vivado Design将这些打包的IP添加到设计中套件或使用IP集成商将IP集成到平台中(例如,具有AMD Zynq™ 设备、DDR3 DRAM和运行o的软件堆栈

使用系统生成器源

AMD DSP系统生成器是一个结合RTL源文件、Simulink和MATLAB软件模型,并将DSP系统的C/C++组件集成到单个仿真和实施环境。有关使用System Generator的更多信息,请参阅Vitis Model Composer用户指南(UG1483)。系统生成器设计通常是包含在更大的HDL设计中的子设计。推荐的流程是将DSP模块封装为Vivado Design Suite中的IP核心,添加到AMD IP目录中,并作为子模块集成到设计层次结构的任何级别,如“使用IP源”中所述,或导入到设计的顶层。这让Vivado IDE管理FPGA设计的项目,同时将DSP模块处理为在System Generator中开发和管理的IP源。有关更多信息,请参阅《Vitis Model Composer用户指南》(UG1483)中的IP目录汇编。

编辑源文件

Vivado IDE提供了一个文本编辑器,用于创建或修改RTL、XDC、Tcl和其他文本来源。编辑Verilog、VHDL、XDC和Tcl文件时,文本编辑器是上下文敏感的,并且使用颜色编码来区分关键字和结构。它是一个可配置的集成文本编辑器,支持语法高亮显示和动态检查,帮助处理错误和警告、代码折叠、代码完成和文件比较。请参见中的使用文本编辑器Vivado Design Suite用户指南:使用Vivado IDE(UG893)获取特定信息文本编辑器中的命令。您可以同时打开多个文件,并单击每个打开文件的选项卡以在文件夹。在打开文件的选项卡中,Vivado IDE在的文件名后面附加一个星号(*)需要保存的已修改文件。要保存文件,请使用以下方法之一:

•选择“文件”>“文本编辑器”>“保存文件”。

•在Vivado IDE文本编辑器中,从右键菜单中选择“保存文件”。

•在Vivado IDE文本编辑器中,使用“保存文件”工具栏按钮。

注意:如果您试图关闭包含未保存更改的文件,Vivado IDE会提示您保存变化。

提示:使用“另存为”命令将源文件保存到新位置。使用“在文件中查找/替换”命令编辑设计源文件时,可能需要查找特定的对象或对象实例。您可以使用“查找”或“在文件中查找”在开源文件或选定的源文件集,或在文件中替换以查找和替换文本字符串。你可以执行以下操作:

•输入任何文本字符串,包括通配符(*、?、#、+)或正则表达式作为搜索条件。

•使用筛选选项搜索源文件、约束文件和报告文件。

使用HDL语言模板

Vivado IDE为包括AMD在内的许多Verilog、VHDL和XDC结构提供模板参数化宏(XPM)和库基元。要查看模板,请执行以下操作:

1.在Vivado IDE文本编辑器中,选择“语言模板”工具栏按钮。

2.选择工具 → 语言模板。出现语言模板窗口,其中包含Verilog、VHDL、SystemVerilog、,

XDC和调试。

选择模板后,可以使用中弹出菜单中的“插入模板”命令文本编辑器。选择此命令会将当前选定的模板文本复制到文件中在光标的当前位置。或者,您可以高亮显示,然后复制并从“语言模板”窗口粘贴所需的文本。有关支持的命令,请参阅Vivado Design Suite用户指南中的此链接:使用Vivado IDE(UG893)。

使用Xilinx参数化宏

XPM是针对HDL流中常见用例(如RAM或ROM、时钟域交叉和FIFO。XPM是与一起交付的SystemVerilog HDL代码Vivado Design Suite,可以在中找到/软件的data/ip/xpm文件夹安装它们可以被认为是参数化的IP,参数的默认值为可以更改以满足设计要求。

XPM的类型包括:

•具有各种RAM和ROM存储结构的XPM_MEMORY

•具有各种安全时钟域交叉(CDC)逻辑实现的XPM_CDC

•用于同步和异步FIFO结构的XPM_FIFO启用Xilinx参数化宏使用项目模式时,Vivado工具将解析添加到项目中的文件,并将自动识别XPM。但是,当在非项目模式下使用XPM时在读取或导入源文件之前,必须发出auto_detect_xmm命令。

使用XPM

您可以在设计中使用任何XPM语言模板。特定的可用参数XPM在语言模板窗口中显示的实例化模板中进行了解释。选择并复制实例化模板的内容,并将其粘贴到您自己的源文件中,或者使用文本编辑器弹出菜单中的“插入模板”命令。你不需要将实例化模板的注释复制到设计源文件中。

您可以根据需要更改实例名称和接线端口,以将XPM实例适合您的根据作为注释提供的文档设计和修改参数/泛型在语言模板中。

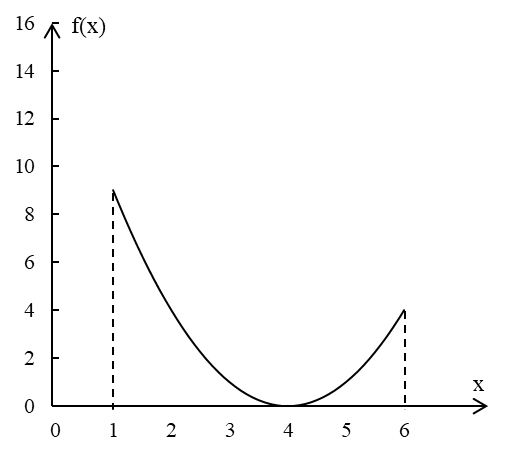

重要!确保阅读并遵守XPM语言模板中的所有代码注释正确使用XPM。下图显示了XPM_CDC实例的示例。

一些XPM提供的约束是在中的Tcl文件中定义的/数据/ip/xpm/特定xpm的<xpm>/tcl文件夹。约束在合成过程中应用,并出现在合成日志文件以及所处理的其他约束。约束可以具有依赖于存在于连接到XPM的网络上的时钟对象。这是因为一些XPM查询时钟的周期属性以设置约束。如果时钟对象是如果不存在,则生成严重警告。重要!使用report_compile_order命令时,中XPM的Tcl约束文件除非您打开了详细的、综合的或实现的设计,否则设计不会显示出来。有关各种XPM及其参数化选项的详细信息,请参阅UltraScale中的此链接体系结构库指南(UG974),或Vivado Design Suite 7系列FPGA和Zynq-7000 SoC图书馆指南(UG953)。