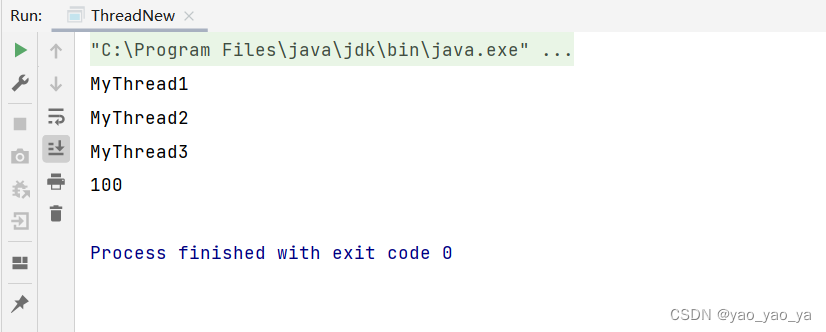

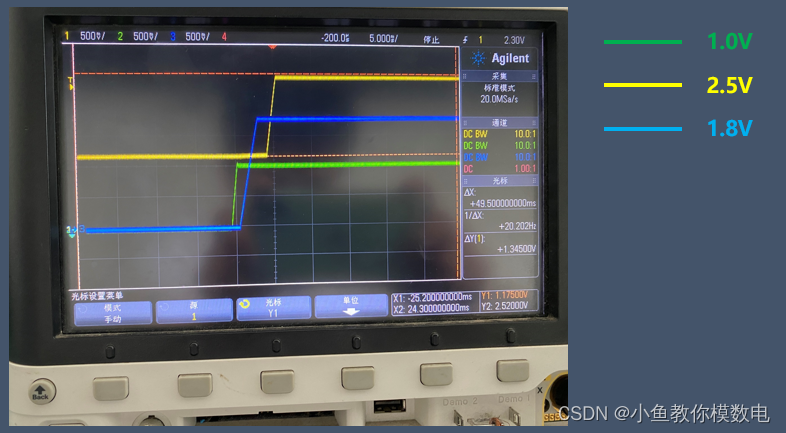

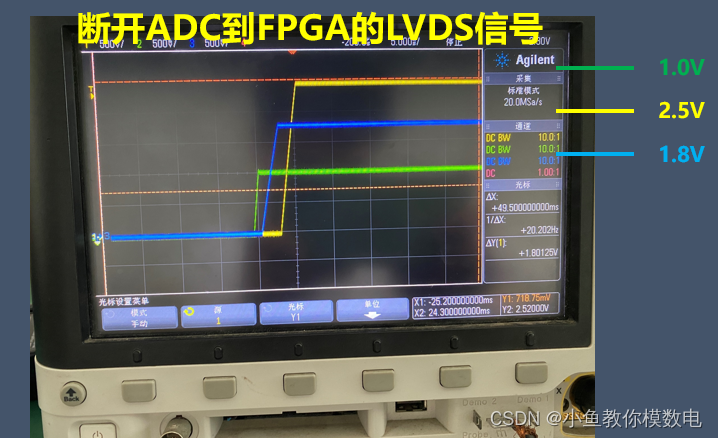

大家可以看下,这张图片是测试XILINX 的FPGA 325T的上电时序图,其中绿色的线是FPGA 核心电源VCCINT 1.0V的波形,黄色的是BANK的电源2.5V的波形,蓝色的是辅助电源1.8V 的波形

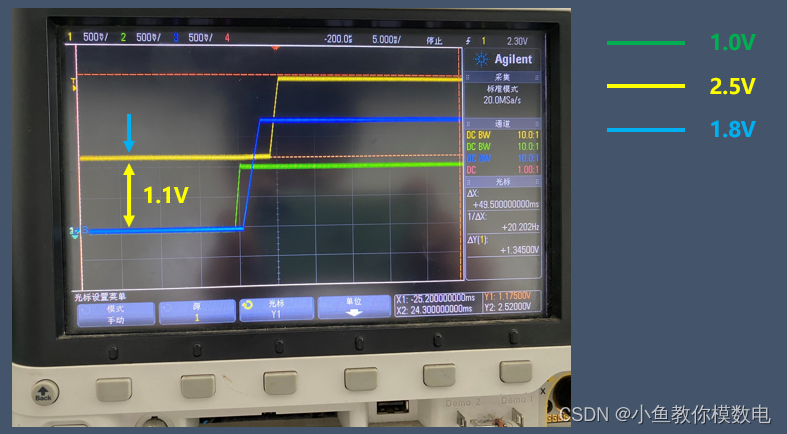

大家有没有发现这个时序图中黄色的波形,也就是2.5V的电压,上电的时候不是从0V开始上电的,而是从1.1V左右开始上电的。今天就来分享下产生这个现象的原因。

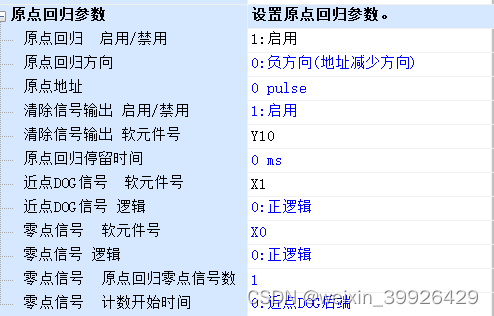

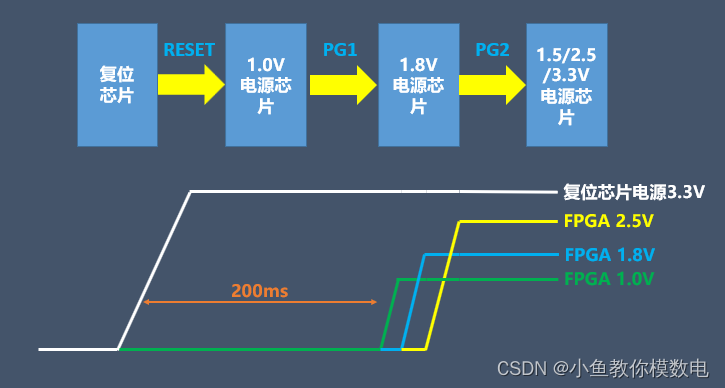

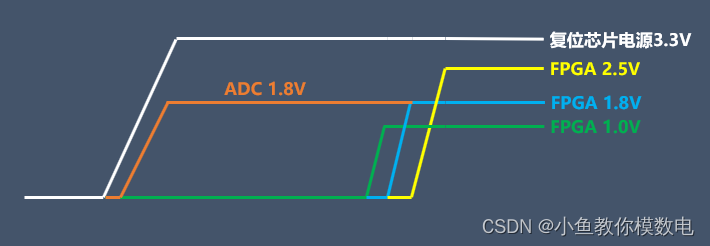

FPGA的上电时序在设计时是这样的,首先是一个复位芯片的电源3.3V先上电,复位信号低电平时间大概200毫秒,

然后复位信号控制FPGA的核心电压1.0V上电,

1.0V电源芯片的POWER GOOD信号控制辅助电源1.8V上电,

最后1.8V电源芯片的POWER GOOD信号控制 FPGA 的BANK电压1.5,2.5,3.3V上电。

理论上FPGA的上电波形应该像这个示意图所示,

我们对照前面的实测图片,FPGA的上电时序应该是没问题,唯一的问题就是2.5V上电时不是从0V开始的。

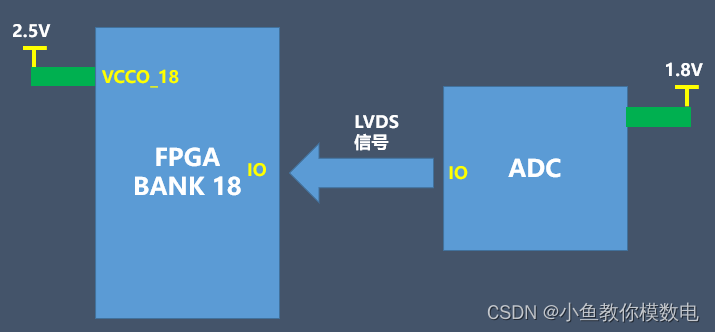

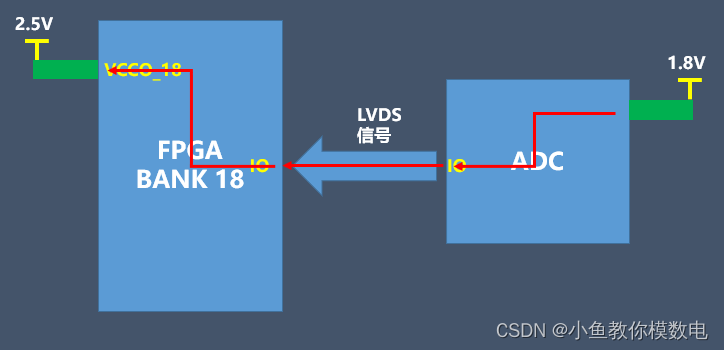

于是找到FPGA 2.5V供电的BANK,只有BANK 18是2.5V供电的,BANK18接的是ADC 的LVDS信号,ADC芯片供电电压是1.8V,

这个1.8V电压上电后就有,不受前面的FPGA时序控制,一上电后就会有。

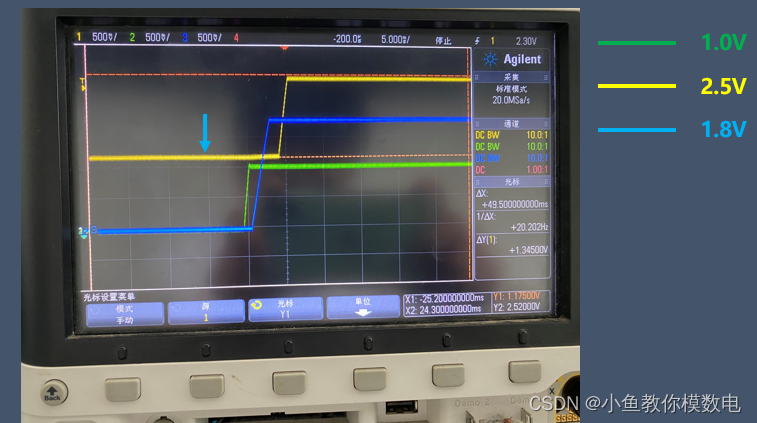

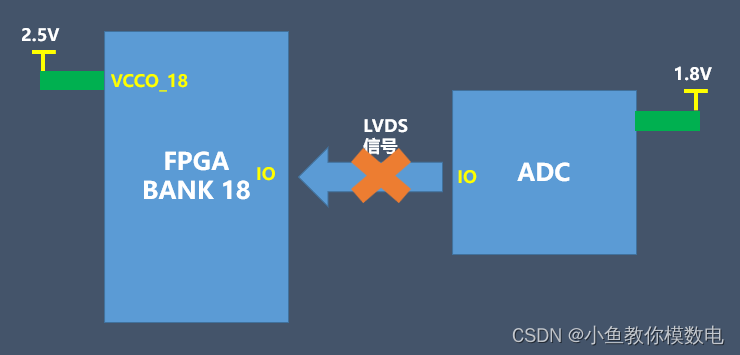

尝试断开ADC芯片到FPGA的LVDS信号,然后上电,

测试FPGA的上电时序,测试波形大家可以看一下,这个波形就比较正常了,1.0V先上电,然后1.8V,最后2.5V,并且2.5V是从0V开始上电的。

所以2.5V电源在上电之前的1.1V左右的电压应该是由ADC的LVDS信号通过FPGA的IO口串到BANK18的电源上的,也就是串到2.5V电源平面上的,这样就会导致2.5V上电前会有个1.1V左右的电压。

实测一下2.5V上电时,ADC LVDS信号的波形,可以看到,在2,5V上电前ADC LVDS信号一直是一个恒定电压,电压值也是接近1.1V.

如果想消除2,5V上电的这种问题,我们只需要把ADC 1.8V电源的上电时序移到2.5V上电之后就可以啦。

在电路设计的时候尽量让主芯片先上电,然后再让外围的芯片上电

今天的分享就到这里,谢谢大家