所有现代FPGA的配置分为两类:基于SRAM的和基于非易失性的。其中,前者使用外部存储器来配置FPGA内的SRAM;后者只配置一次。

Lattice和Actel的FPGA使用称为反熔丝的非易失性配置技术,其主要优点是系统设计更加简单、不需要外部存储器和配置控制器、功耗低、成本低和FPGA配置时间更快。最大的缺点在于配置是固定的。

大多数现代FPGA都是基于SRAM,包括Xilinx Spartan和Virtex系列。每个FPGA上电后或在后续的FPGA配置期间,从外部非易失性存储器中读取比特流,由配置控制器处理,并加载到内部配置SRAM中。SRAM保持了配置逻辑、IO、嵌入式存储器、布线、时钟、收发器和其他FPGA原语等所有的设计信息。

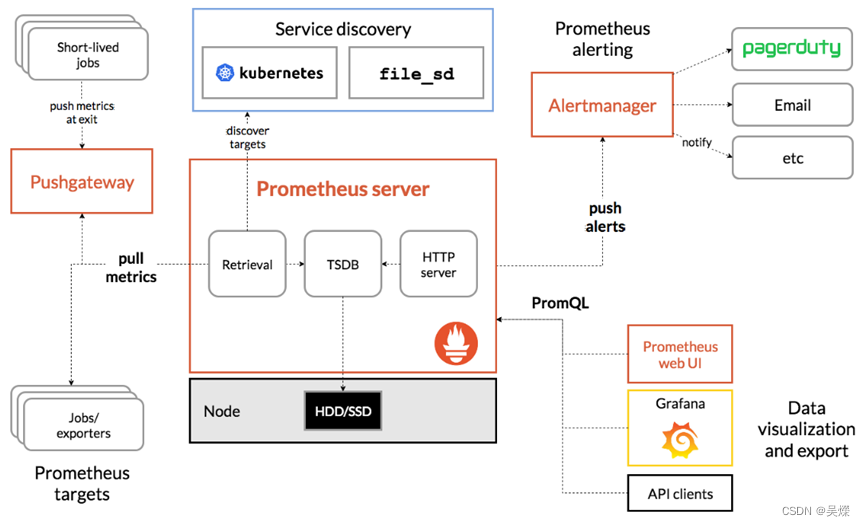

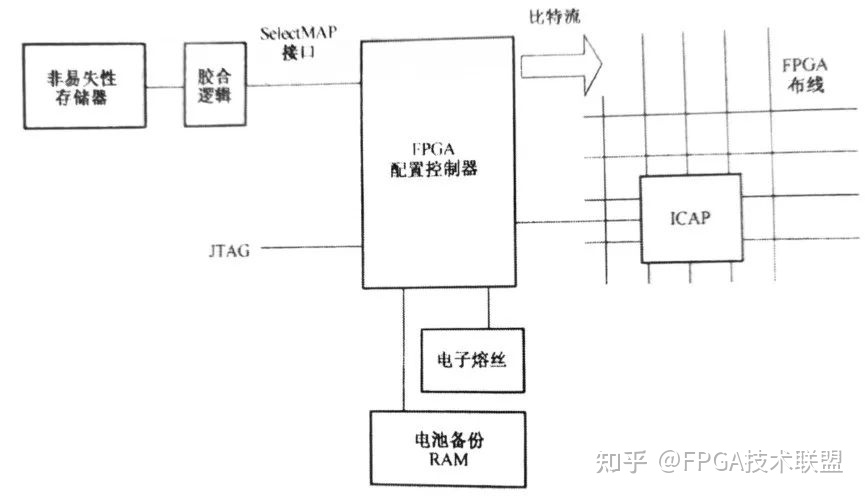

图1是Xilinx Virtex-6 的配置结构。

配置是由FPGA内部的配置控制器执行。比特流存储在外部非易失性存储器(如Flash)中。外部存储器通过使用SelectMAP接口连接到配置控制器,这是Xilinx特有的。额外的胶合逻辑可能需要架起SelectMAP和外部存储器接口之间的桥梁。此外,比特流可以通过JTAG或ICAP加载到配置控制器中。比特流可以选择加密,以提高安全性。内部电池备份RAM( BBR)和eFuse保存用于比特流解密的加密密钥。

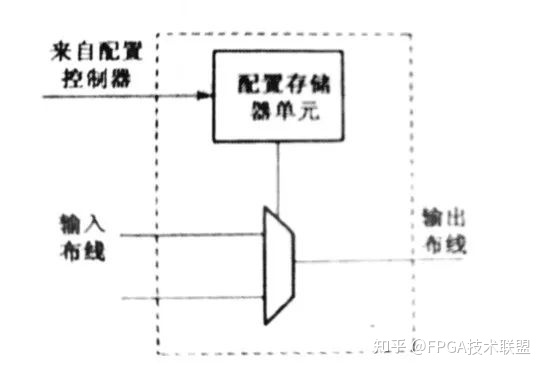

FPGA配置存储器也称为配置存储器单元,它的每一位与比特流中的对应位一起初始化。每个存储器单元的输出连接到可配置的功能块上,如LUT、寄存器、BRAM、IO、布线等。下图是配置存储器单元连接到多路复用器,以设置FPGA架构中元件之间的特定布线路径。在FPGA配置阶段,逻辑状态被置位为1或0。

Xilinx的FPGA配置模式

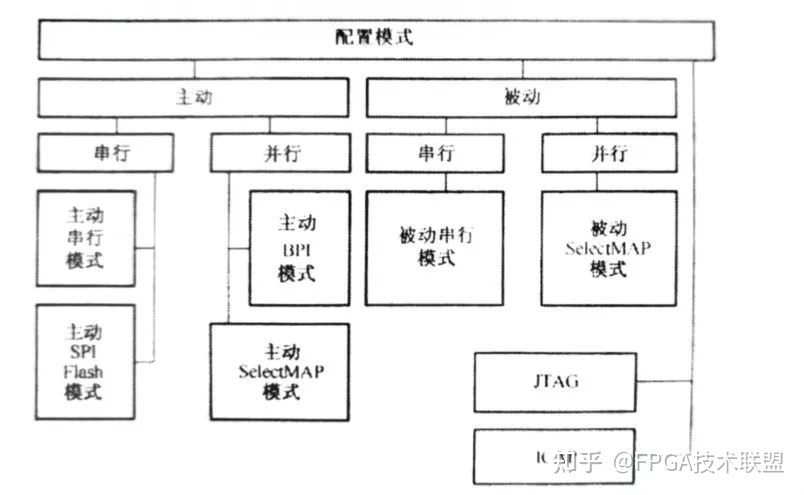

多种FPGA配置模式可满足不同的使用模式。图3是Xilinx FPGA配置模式的分类。

配置模式分为两类:主动( master)模式和被动(slave)模式。在主动配置模式下,FPGA控制配置过程。在被动模式下,由外部设备(如单片机、CPLD或其他FPGA)控制FPGA的配置过程。此外,还有两个特殊的配置模式,即使用JTAG和内部配置访问端口(ICAP)。有4种数据宽度支持不同的外部存储器: 32位、16位、8位、1位(串行)。下面是配置模式的简要介绍。

JTAG

JTAG接口主要在调试期间使用。为了与Xilinx ChipScope 和iMPACT软件应用程序接口,特殊的适配器连接到专用FPGA引脚上。

ICAP

专用的ICAP原语用于与用户逻辑的接口,在FPGA架构内进行配置。

主动串行模式

在主动串行模式中,FPGA控制Xilinx Platform Flash,以提供配置数据。Xilinx Platform Flash是一种特殊的非易失性存储器,旨在通过使用SelectMAP接口直接与Xilinx FPGA接口。

主动SPI Flash模式

在主动SPI Flash 模式中,FPGA控制串行SPI闪存,以提供配置数据。

主动SelectMAP模式

在主动SelectMAP模式中,FPGA控制Xilinx Plaform Flash,以提供8位或16位的配置数据。

主动BPI模式

在主动BPI模式中,FPGA控制并行NOR Flash, 以提供8位或16位的配置数据。

被动串行和SelectMAP模式

在被动串行模式下,外部设备(如单片机、CPLD或其他FPGA)控制FPGA的配置过程。

设计FPGA配置方案

对于特定设计来说,有一些设计考虑用于选择最合适的 FPGA配置方案。主要的选择标准是:

选择是否通过外部设备(被动模式)或由FPGA本身(主动模式)控制配置过程。从系统复杂性角度来看,主动模式最简单,但未必适合所有设计。被动模式接口作为简单的串行接口,直接连接到处理器的IO引脚,读取比特流数据进入配置控制器。

●选择外部非易失性存储器的类型和大小,用于存储一个或多个FPGA比特流。尽管与FPGA的成本相比,外部存储器的成本相对较低,但仍然是不可忽略的。设计者可以在SPI Flash、并行NOR Flash、或Xilinx Platform Flash 之间进行选择。在某些设计中,FPGA可以使用连接到被动模式下的FPGA配置控制器直接配置。

●数据宽度的选择---串行、 8位、16位或32位----影响配置速度和FPGA中用于设计的I0数目。

●现场升级配置比特流可以是一个重要的需求。配置方案必须解决当比特流正在编程进入非易失性存储器时发生损坏的情况。

●Xilinx FPGA提供了一个选项,用来加密在更高设计安全要求情况下的比特流。解密密钥可以存储在内部的BBR或者eFuse中。BBR存储器是易失性的,需要外部电池。使用BBR与使用非易失性eFuse相比,重新编程相对容易。

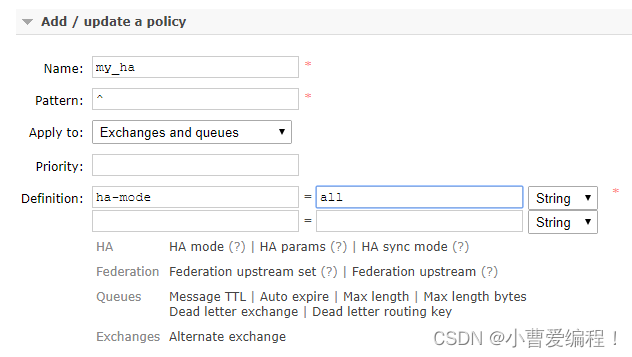

●配置模式的选择如图所示,以Spartan-6为例,配置模式选择如下图所示:

●不同配置模式的硬件设计如下图所示:

计算配置时间

在许多应用中,FPGA配置时间很关键,要准确估计配置方案选择过程中的时间是很重要的。配置时间取决于比特流大小、时钟频率和配置接口的数据宽度,按下列公式定义:

配置时间=比特流大小x时钟频率x数据宽度

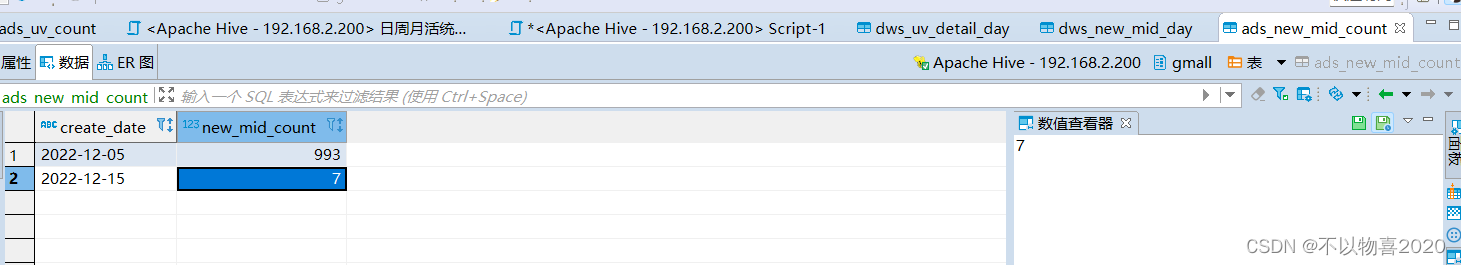

表1提供了配置接口在不同数据宽度下,对于使用50 MHz时钟的最小和最大Xlinx Virtex-6 FPGA的预期配置时间。

Xilinx配置相关的原语

表2提供了Xilinx Virtex-6 FPGA支持的与配置相关的原语列表。

参考文献

[1] Configuration for Xilinx Virtex-6 FPGAhttp://www.xilinx.com/products/design_resources/config_ sol/v6/config_v6.htm

更多有趣的话题请看链接:

FPGA知识汇集-FPGA项目开发包含那些任务?

FPGA知识汇集--FPGA结构(1)

FPGA的应用

FPGA知识汇集-在命令行模式下使用Xilinx工具

FPGA知识汇集-ISE的这些有用的工具您知道吗?

FPGA知识汇集-FPGA设计开发需要熟悉哪些EDA工具呢?

FPGA知识汇集-值得收藏的FPGA代码命名规范?

FPGA 知识汇集--Linux下ISE的环境变量设置

FPGA知识汇集-值得收藏的Verilog代码风格1

FPGA知识汇集-值得收藏的Verilog代码风格2

FPGA知识汇集-编写可综合代码(RTL)需要注意的规则总结

FPGA知识汇集-Verilog和VHDL的混合使用

FPGA知识汇集-关于Xilinx 工具报告

FPGA知识汇集-例化与推译

硬件仿真加速器与原型验证平台

FPGA知识汇集-ASIC向FPGA的移植

FPGA知识汇集-时钟系统的移植

FPGA知识汇集-FPGA的低功耗设计方法总结

FPGA知识汇集-了解FPGA比特流结构