02. 源同步时序系统

针对普通时钟系统存在着限制时钟频率的弊端,人们设计了一种新的时序系统,称之为源同步时序系统。它最大的优点就是大大提升了总线的速度,在理论上信号的传送可以不受传输延迟的影响。下面我们来看看这种源同步时钟系统的结构。

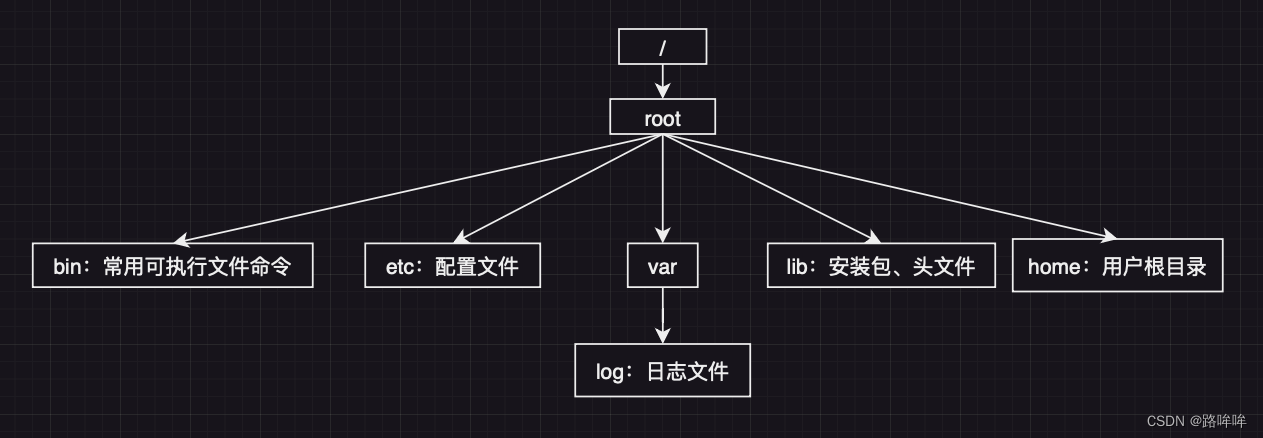

1.源同步系统的基本结构

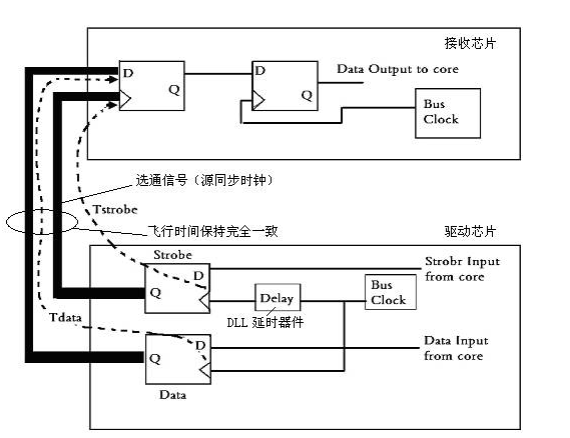

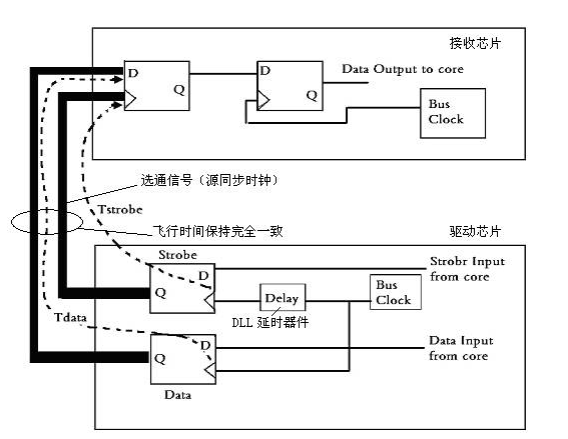

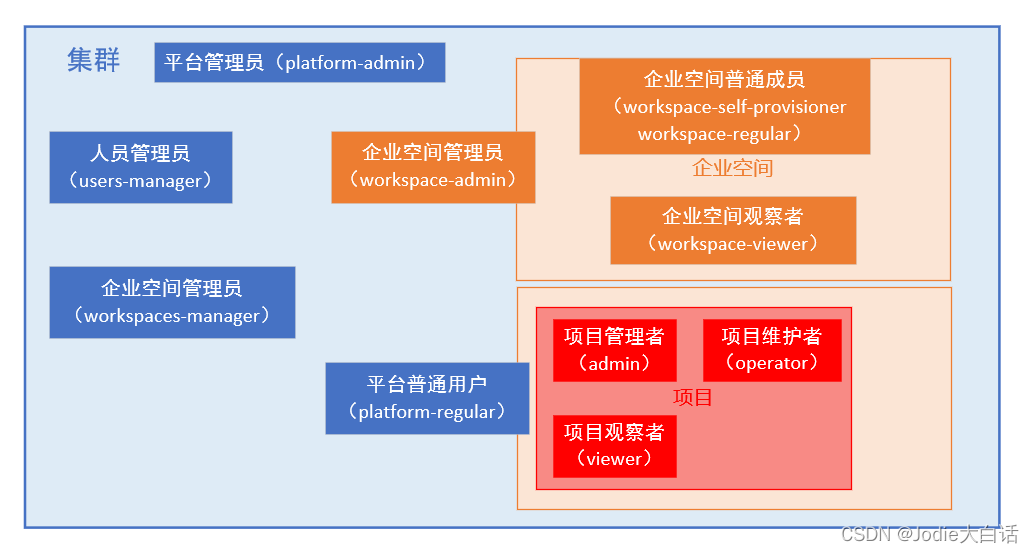

上图是一个基本的源同步时钟系统的结构示意图。可以看到,驱动芯片在发送数据信号的同时也产生了选通信号(Strobe),而接收端的触发器由该选通信号脉冲控制数据的读取,因此,这个选通信号也可以称为源同步时钟信号。

源同步时钟系统中,数据和源同步时钟信号是同步传输的,我们保证这两个信号的飞行时间完全一致,这样只要在发送端的时序是正确的,那么在接收端也能得到完全正确的时序。整个系统在时序上的稳定性完全体现在数据和选通信号的匹配程度上,包括传输延迟的匹配,器件性能的匹配等等,只要两者条件完全相同,那么我们就可以保证系统的时序绝对正确,而对系统的最高时钟频率没有任何限制。

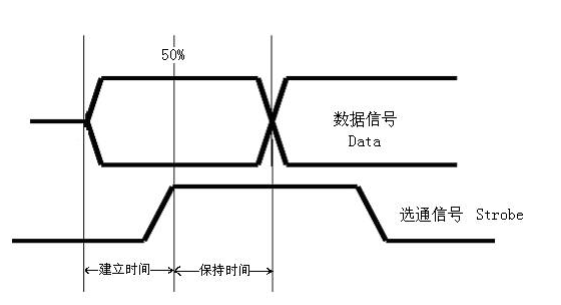

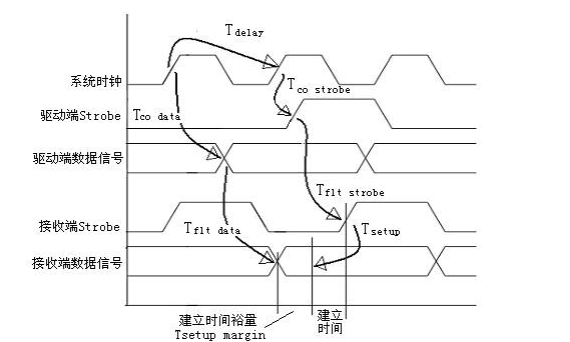

当然,对于任何数据接收来说,一定的建立和保持时间都是必须满足的,源同步时钟系统也同样如此,主要体现在数据信号和选通信号之间的时序要求上。最理想的情况就是选通信号能在数据信号的中央部分读取,如图下图所示,这样才能保证最充分的建立和保持时间。

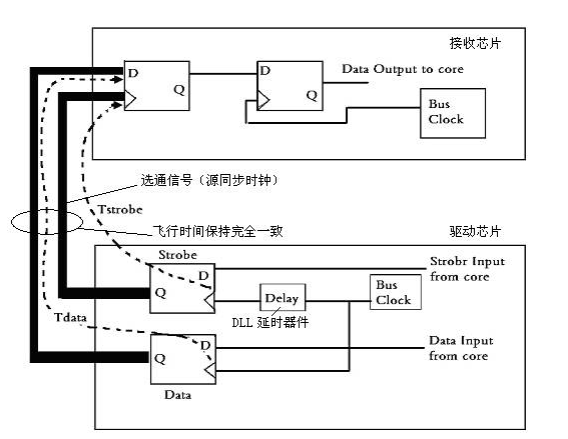

为了保证选通信号和数据信号相对保持正确的时序,在源同步时钟系统中是通过驱动芯片内部的数字延时器件DLL来实现(见下图),而不是通过PCB走线来控制,因为相比较而言,DLL器件能做到更为精确的延时,同时还可以受芯片电路控制,调节起来更为方便。

2.源同步时序要求

前面已经提到源同步时钟系统设计中最重要的一点就是保证data和strobe信号之间的偏移(Skew)最小,引起这些误差的最主要的因素就是实际系统中各器件的时序参数Tco的不同,此外还有布线上引起的差异,为了更好地说明这些Skew对时序的具体影响,下面我们还是通过时序图分析的方法来计算一下源同步时钟系统中信号的建立时间裕量和保持时间裕量。

首先考虑建立时间裕量:

和普通时序分析的方法一下,我们也是从建立时间环的角度考虑,参考下面的结构图,我们可以作出驱动端和接收端的时序示意图(下图)。

Tdata = Tco_data +Tflt_data

Tstrobe = Tco strobe + Tflt strobe + Tdelay

其中,Tco和Tflt分别代表数据/选通信号在器件的内部延迟和信号传输的飞行时间,Tdelay是指数据信号和选通信号之间的延迟,由系统内DLL延时器件决定,图中假设为一个时钟周期。

将上式带入建立时间裕量的计算公式:Tsetup margin = Tclk – Tdata– Tsetup可以得到:

Tsetup margin =(Tco strobe + Tflt strobe + Tdelay)- (Tco data+ Tflt data) – Tsetup

如果我们将数据和Strobe信号在器件内的延时差异定义为Tvb;将PCB走线引起的延时差异定义为Tpcb skew:

Tvb = Tco data– (Tco strobe + Tdelay)

Tpcb skew = Tflt data – Tflt strobe

这样可以得到一个简单的建立时间裕量方程:

Tsetup margin = - Tvb – Tsetup – Tpcb skew (1.6.5)

注意:公式1.6.5中Tvb是一个负值,从公式中可以看出,如果数据和选通信号的Tco相同的话,其大小就是- Tdelay ,也就说明数据信号必须提前于选通信号发送。

再考虑保持时间裕量,如下图所示,同样分析可以得到:

再考虑保持时间裕量,如图1-6-12,同样分析可以得到:

Thold margin = (Tco data + Tflt data + Tdelay) – (Tco strobe +Tflt strobe) – Thold

如果定义:Tva = Tco data – Tco strobe + Tdelay 为正值;Tpcb skew定义不变。则保持时间裕量的计算公式为:

Thold margin = Tva – Thold – Tpcb skew (1.6.6)

在公式1.6.5和1.6.6中,两个重要的参数是Tvb和Tva,Tvb表示“Valid before”,即数据在选通脉冲前有效存在的时间;Tva表示“Valid after”,指选通信号脉冲之后数据仍然有效持续的时间。这两个时序参数一般都可以在器件的datasheet上会找到。

和普通时钟系统相比,源同步总线在PCB布线的设计上反而更为方便,设计者只需要严格保证线长的匹配就行了,而不用太多的考虑信号走线本身的长度。当然,尽管源同步数据传输在理论上突破了频率的限制,但随着频率的提高,在控制Skew上也变得越来越困难,尤其是一些信号完整性因素带来的影响也越发显得突出,而且目前的高速系统设计中,往往综合应用了普通时钟和源同步时钟技术,比如对于地址/控制信号采用普通时钟总线,而高速的数据传输则是采用源同步总线。这些对于高速PCB设计分析人员来说是一个非常严峻的挑战。

更多有趣的话题请看链接:

FPGA知识汇集-FPGA项目开发包含那些任务?

FPGA知识汇集--FPGA结构(1)

FPGA的应用

FPGA知识汇集-在命令行模式下使用Xilinx工具

FPGA知识汇集-ISE的这些有用的工具您知道吗?

FPGA知识汇集-FPGA设计开发需要熟悉哪些EDA工具呢?

FPGA知识汇集-值得收藏的FPGA代码命名规范?

FPGA 知识汇集--Linux下ISE的环境变量设置

FPGA知识汇集-值得收藏的Verilog代码风格1

FPGA知识汇集-值得收藏的Verilog代码风格2

FPGA知识汇集-编写可综合代码(RTL)需要注意的规则总结

FPGA知识汇集-Verilog和VHDL的混合使用

FPGA知识汇集-关于Xilinx 工具报告

FPGA知识汇集-例化与推译

硬件仿真加速器与原型验证平台

FPGA知识汇集-ASIC向FPGA的移植

FPGA知识汇集-时钟系统的移植

FPGA知识汇集-FPGA的低功耗设计方法总结

FPGA知识汇集-了解FPGA比特流结构

FPGA知识汇集-串行 RapidIO: 高性能嵌入式互连技术

FPGA知识汇集-FPGA时序基础理论

FPGA知识汇集-FPGA系统时序理论

![2022-12-29 [整理]flex弹性布局](https://img-blog.csdnimg.cn/8298c8d279fa4e6790f3693dc064d942.png#pic_center)

![[年终总结]满意但不满足](https://img-blog.csdnimg.cn/0197bbc7def241d9bf419e34f8402a3a.jpeg#pic_center)