P1 FPGA基本原理

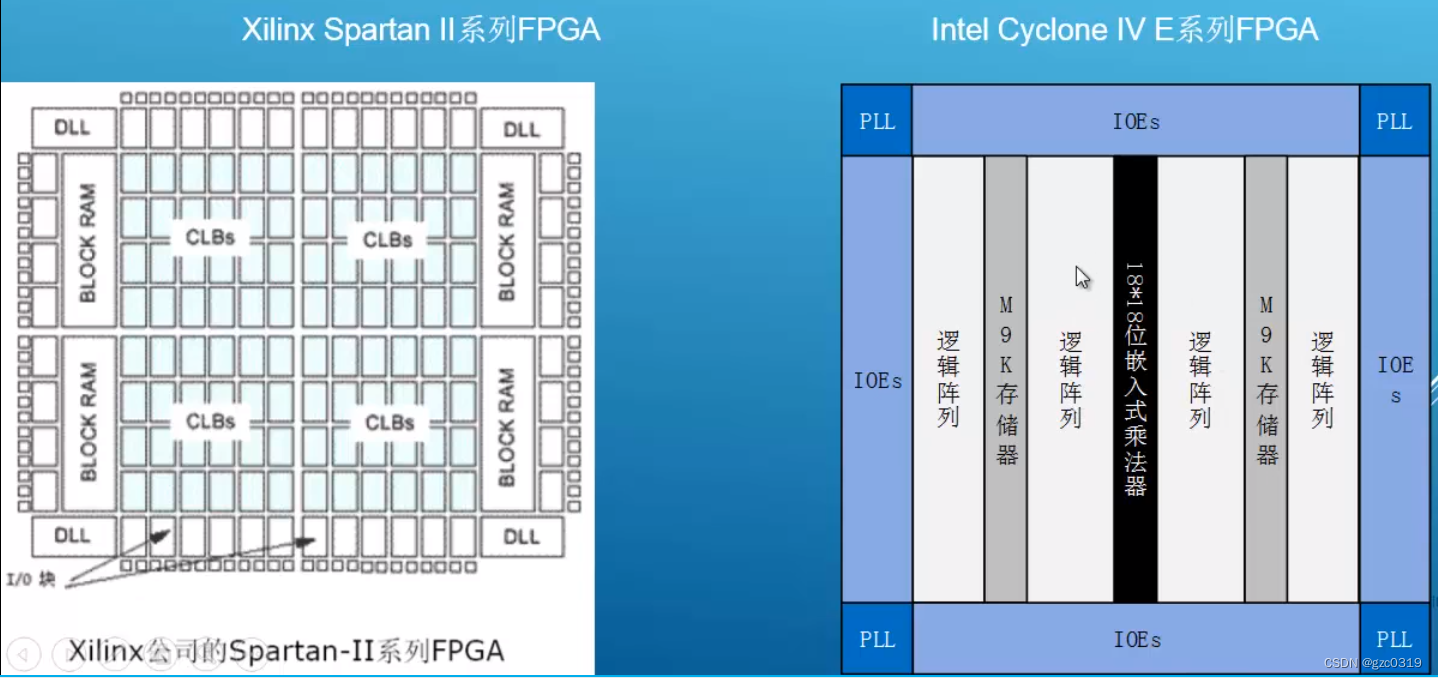

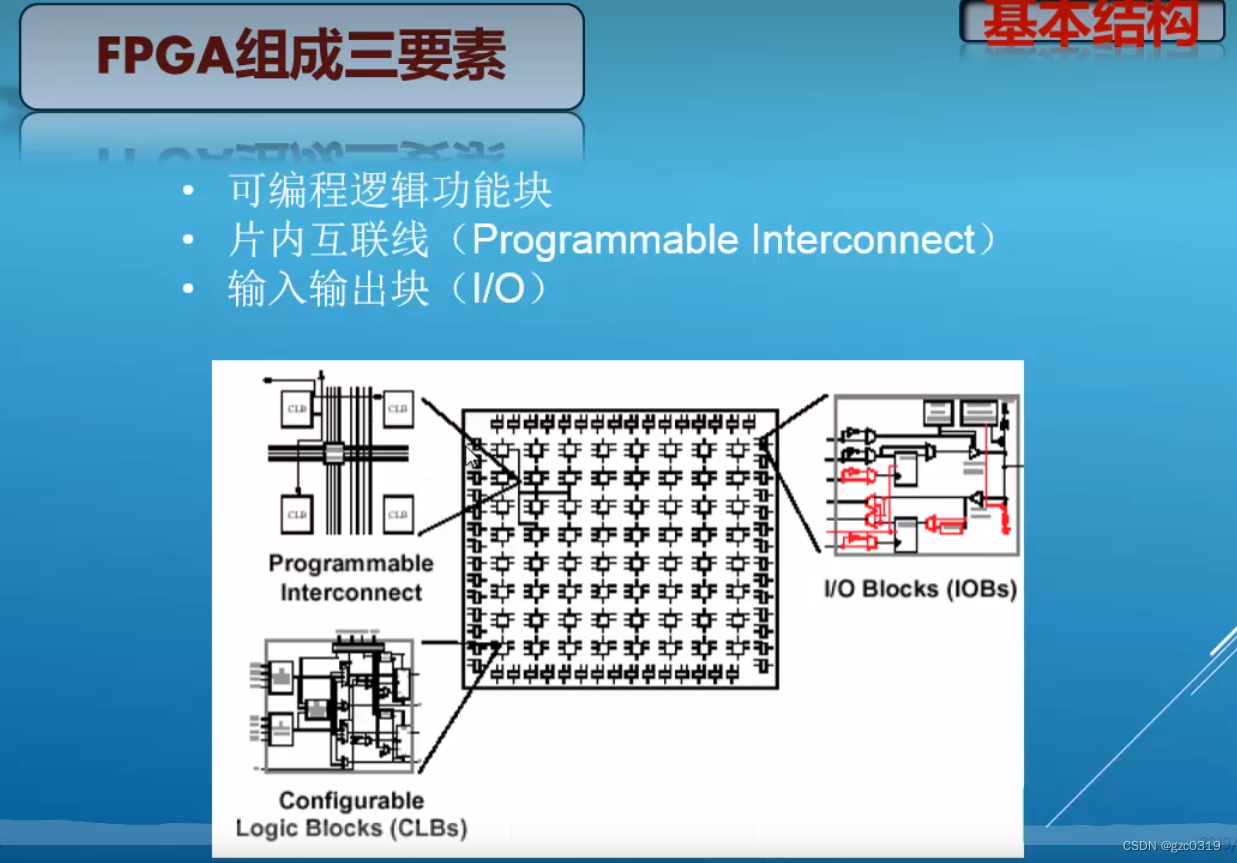

基本结构

三要素可类比电路板的器件、连线、对外端子

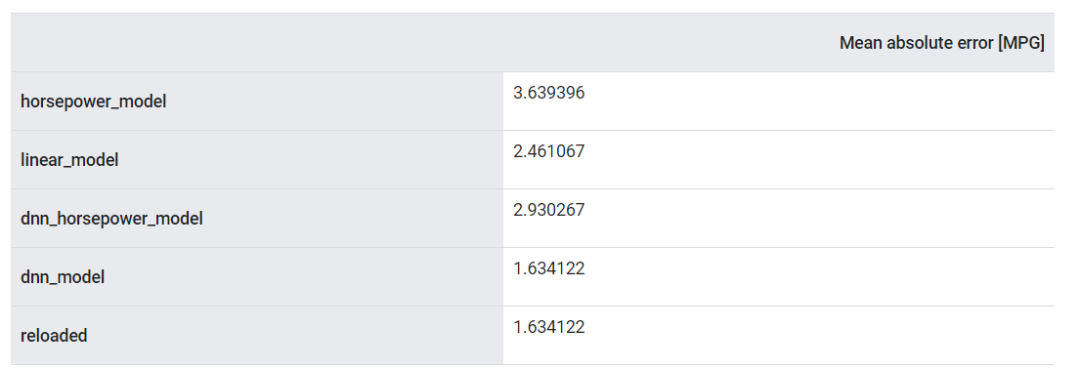

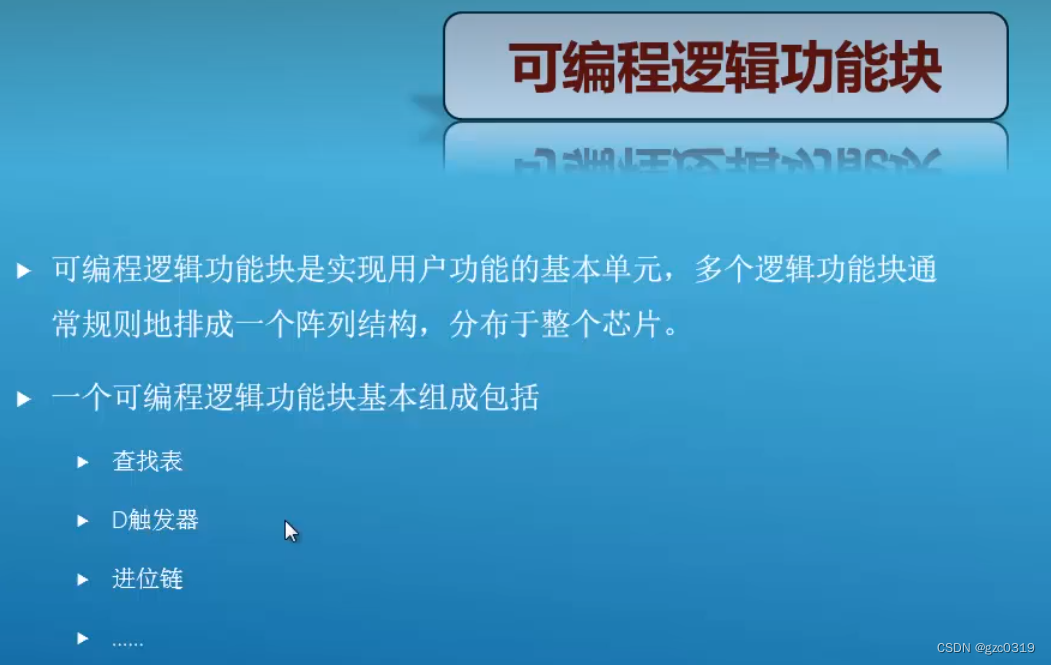

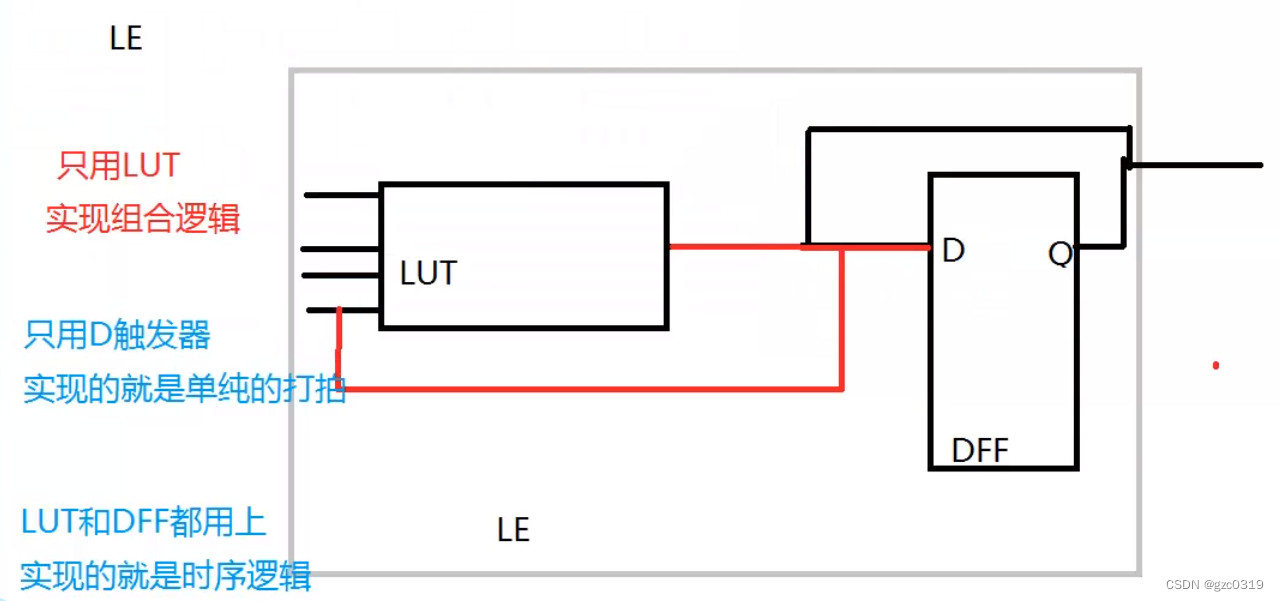

可编程逻辑功能块

触发器用于实现时序逻辑,进位链用于可编程逻辑块间通讯,使用较少。

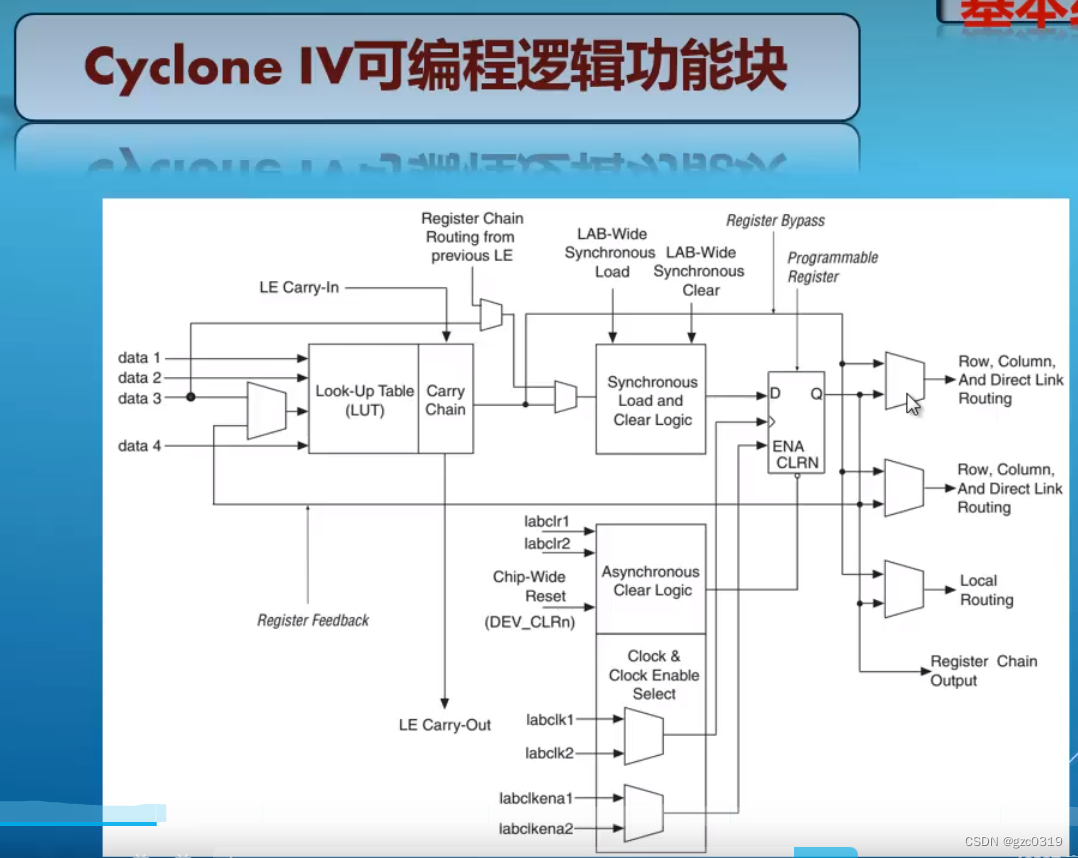

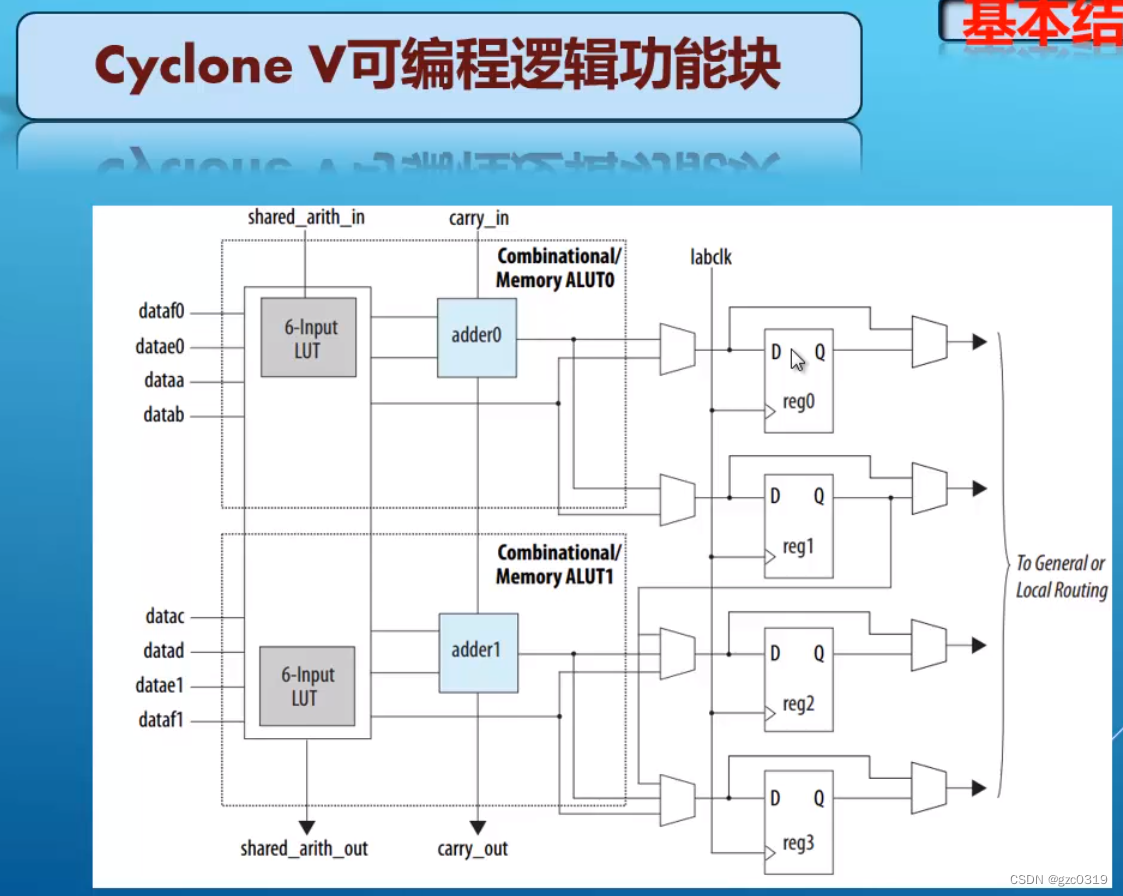

具体器件的可编程逻辑功能块结构。第5代将四输入查找表升级到六输入查找表

由上面两个图抽象得到下图,并给出三种使用方式。

【D触发器(data flip-flop或delay flip-flop)】 【LUT指显示查找表(Look-Up-Table)】

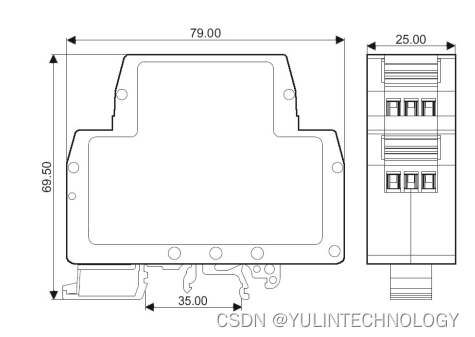

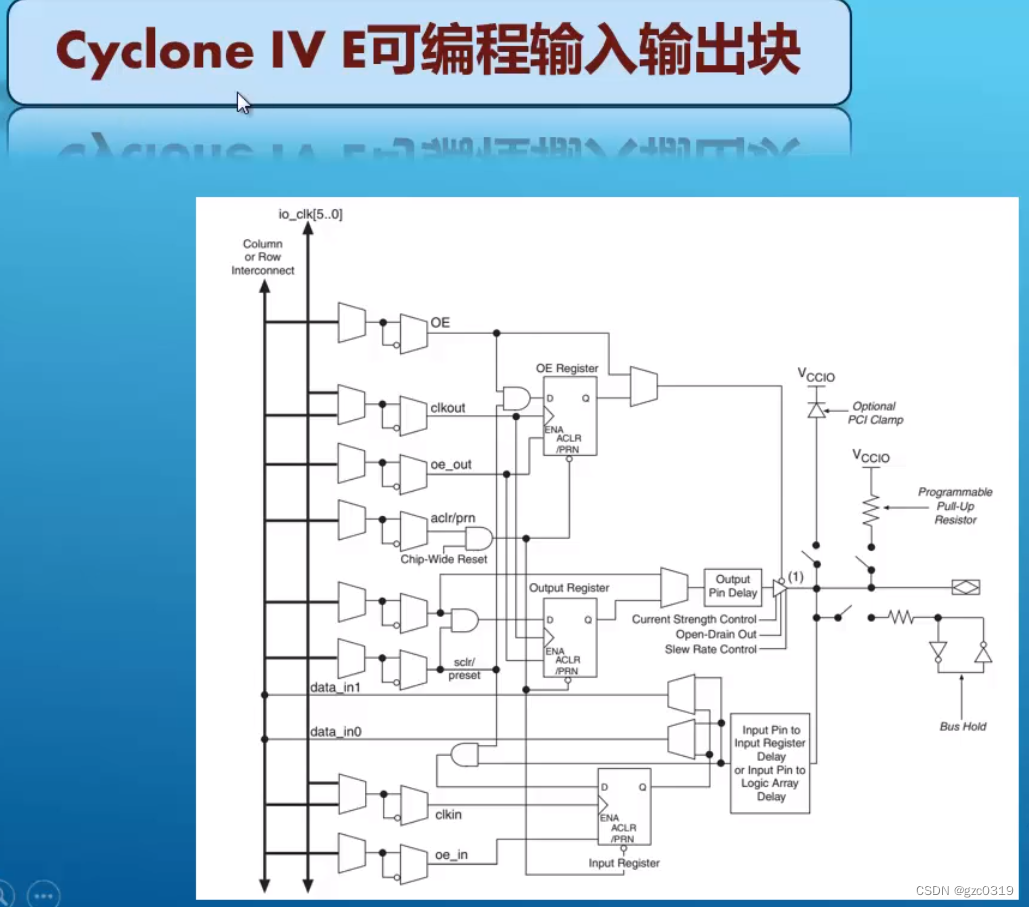

可编程输入输出块

输出寄存器 Output Register、输出延迟链 Output Pin Delay、输入延迟链 Input Pin to Input Register Delay、输入寄存器 Input Register、输出使能寄存器 OE Register、上拉电阻 Program Pull-Up Resistor

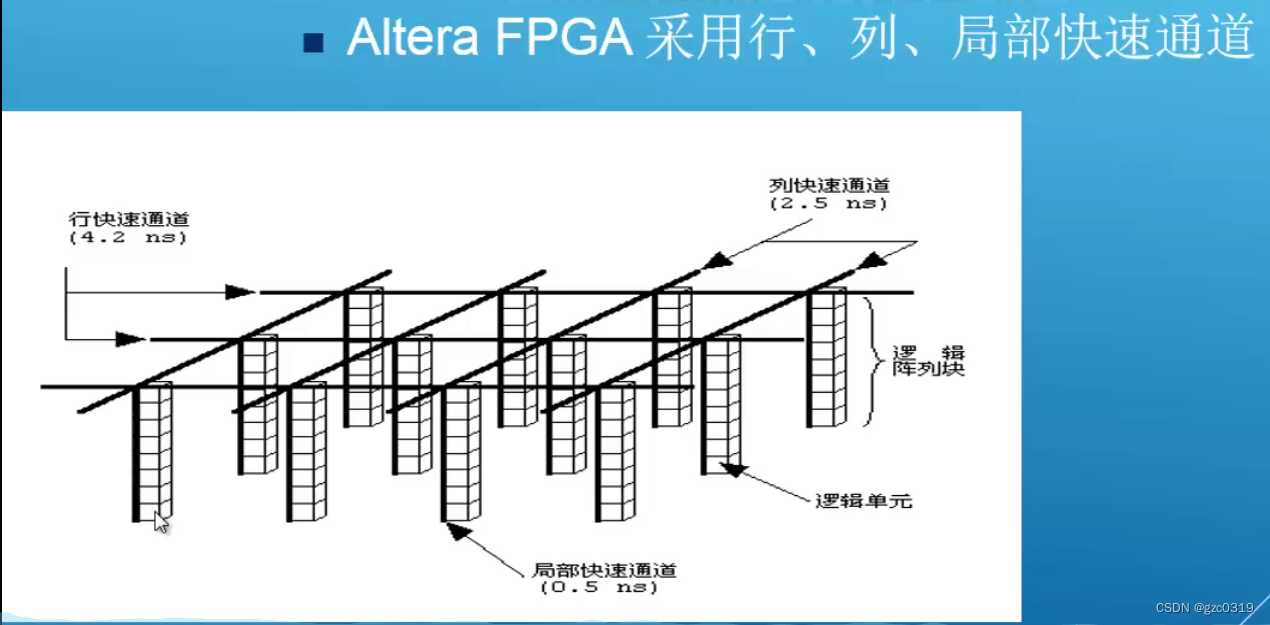

可编程内部互联资源

连接线和连接开关

局部快速通道【同一栋楼不同楼层间】、列快速通道【同一小区不同楼层间】、行快速通道【不同小区间】。添加时序约束后会尽量将高速信号布局在同一栋楼,信号太多则在同一小区。

FPGA可编程原理

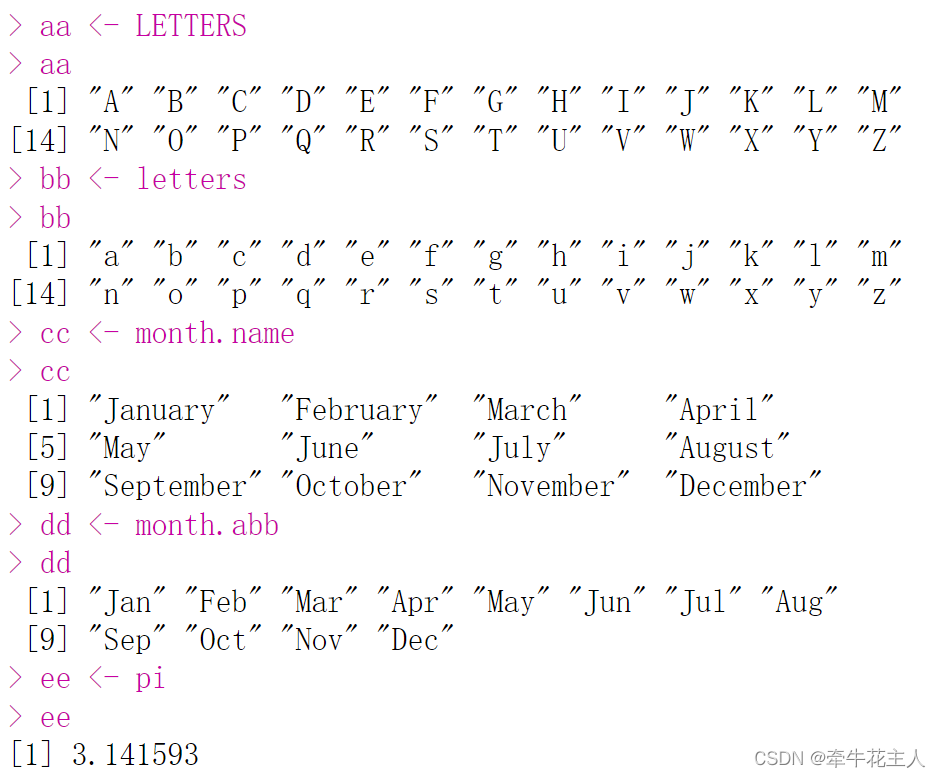

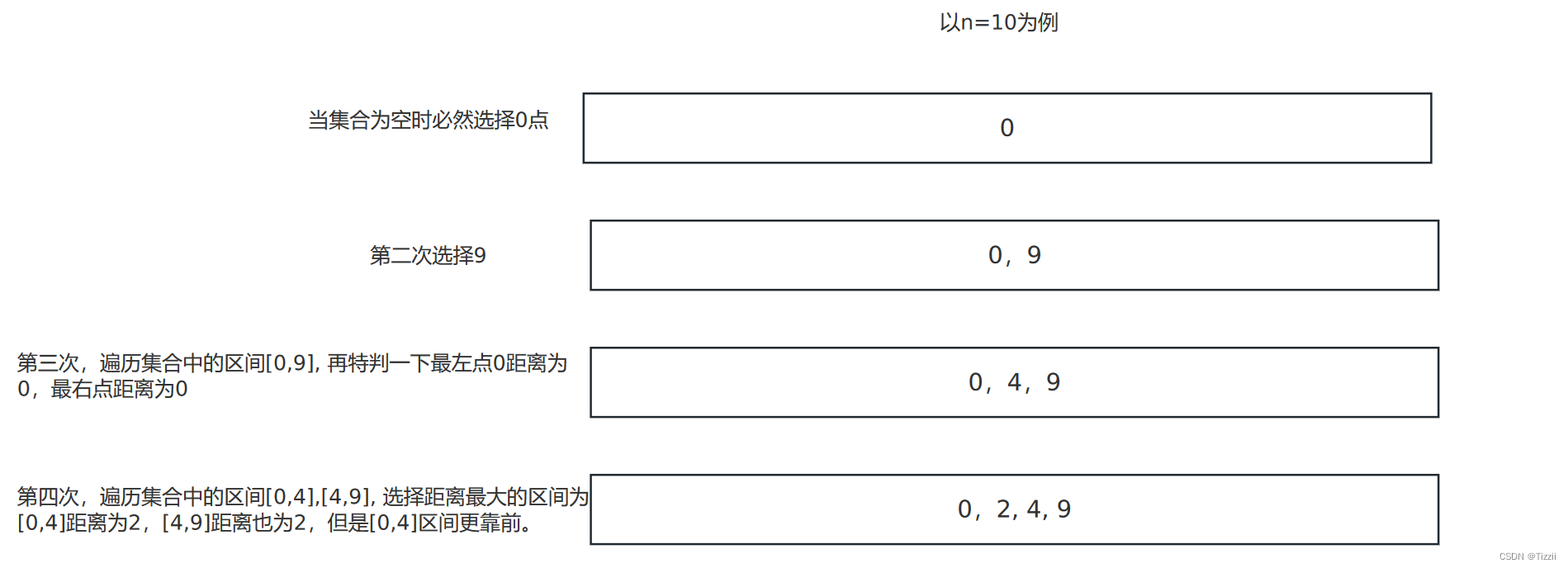

查找表实现任意可编程逻辑的方法:比如要实现A&B&C&D,就需要将RAM的前15个bit写0,最后一个bit写1【输入0选择上方通道,输入1选择下方通道】。

所谓可编程就是配置RAM不同bit具体数值

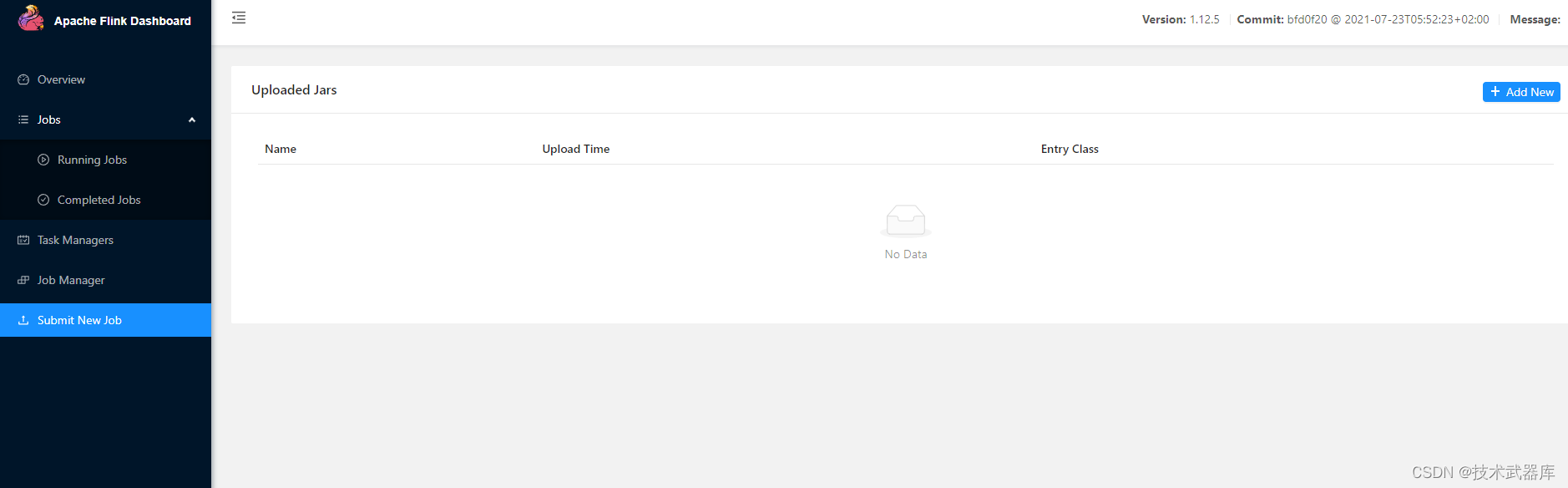

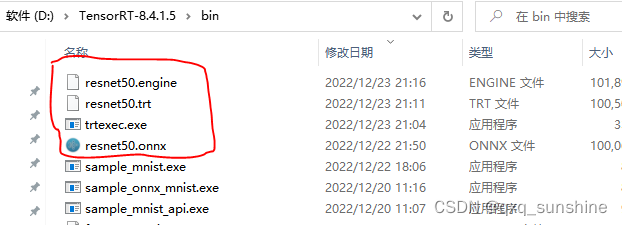

FPGA可选扩展资源

典型FPGA结构