1、设计

QoR

汇总

命令行选项

-qor_summary

可用于为流程中每个步骤生成

QoR

汇总信息。该选项只能从

Tcl

控制台使用。该选项可按两种格式生成:

基于文本的报告或

JSON

格式。

要生成基于文本的格式

,

请运行以下命令

:

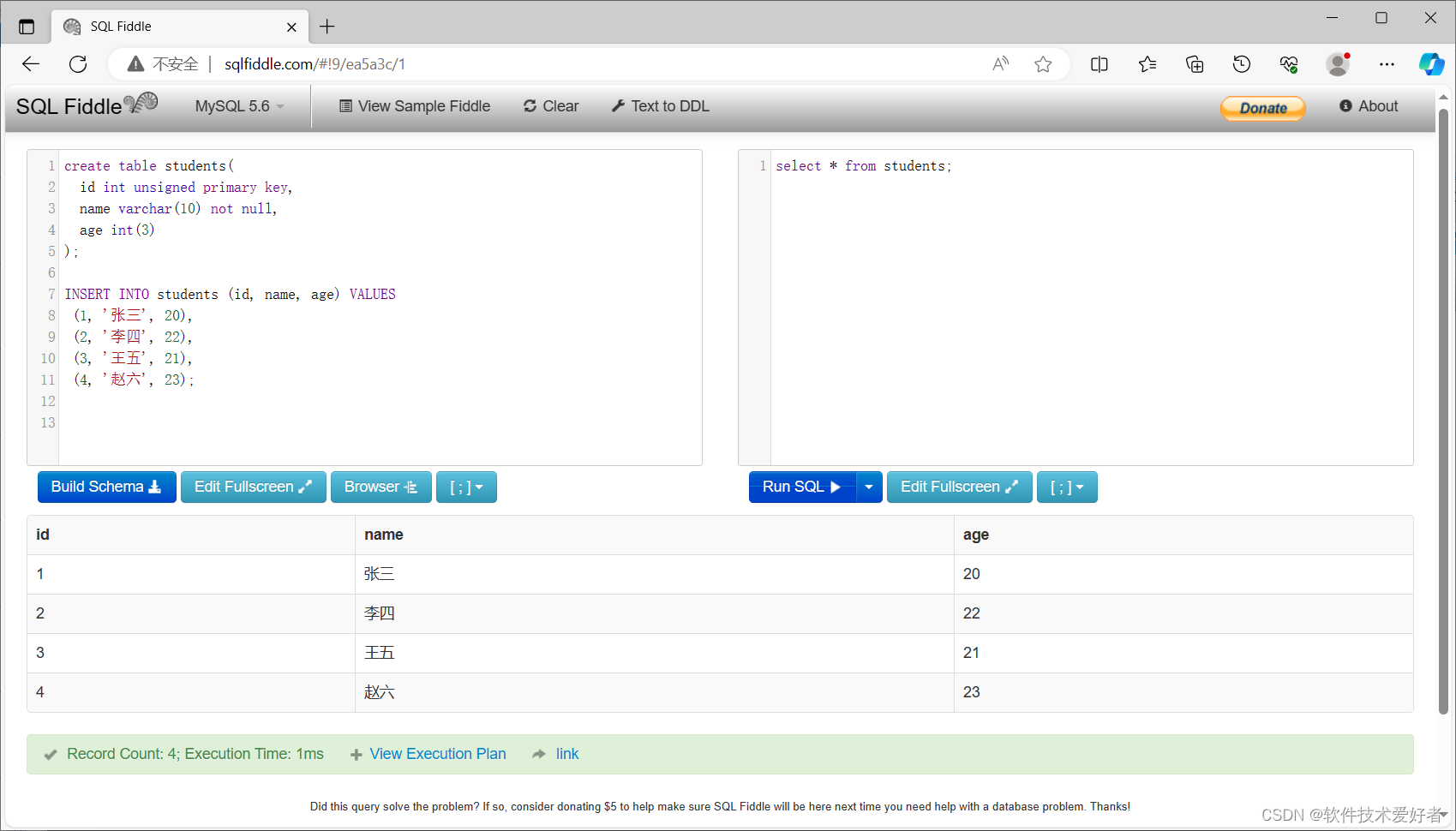

report_design_analysis -qor_summary

此汇总报告也可以

JSON

格式生成。采用

JSON

格式时

,

该表作为单个表格平铺展示

,

以便于解析。此报告中仅限这部分能按此格式输出,

但它更便于对部分关键设计指标进行解析。要以

JSON

格式生成汇总报告

,

请运行以下命令

:

report_design_analysis -qor_summary -json <json filename>

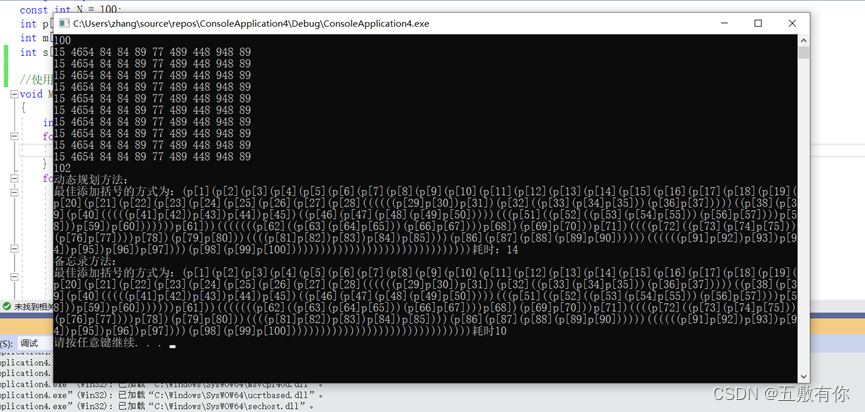

2、使用“

Report Design Analysis

”

常见

QoR

问题主要分为

2

类

:

•

时序违例

•

拥塞

时序违例

虽然分析和修复最差时序违例通常有助于提升总体

QoR

,

但您还必须复查其他关键路径

,

因为这些路径通常会增加时序收敛困难。您可使用以下命令来报告前 50

条最差的建立时序路径

:

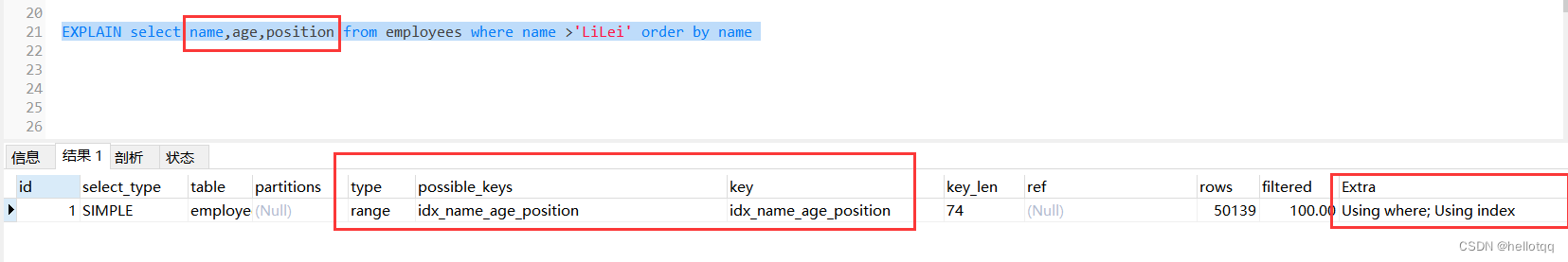

report_design_analysis -max_paths 50 -setup

在该表中

,

可明确识别导致每条路径产生时序违例的各项特性

:

• 逻辑延迟百分比过高

(

逻辑延迟

)

逻辑层次是否过多

?(

逻辑级数

)

是否存在阻碍逻辑最优化的任何约束或属性

?(

勿触

,

标记调试

)

路径是否包含具有高逻辑延迟的单元

,

例如

RAMB

或

DSP

等

?

当前路径拓扑结构的路径要求是否过于苛刻

?(

要求

)

• 高信号线延迟百分比

(

信号线延迟

)

在路径中是否有任何高扇出信号线

?(

高扇出

,

累积扇出

)

分配给多个

Pblock

的单元布局能否拉开距离

?

(Pblocks)

单元布局能否拉开距离

?(

边界框大小

,

时钟区域距离

)

对于

SSI

器件

,

是否存在跨

SLR

边界的信号线

?(

SLR

交汇

)

在布局看似正确的情况下

,

是否有

1

个或多个信号线延迟值远高于预期

?

•

RAMB

或

DSP

单元中缺少流水线寄存器

(

而路径中存在此寄存器

)

检查路径

,

确认针对

RAMB

或

DSP

单元是否已启用流水线寄存器

• 高偏差

(

建立

<-0.5 ns

,

保持

> 0.5 ns

)(

时钟偏差

)

此路径是时钟域交汇路径吗

?(

起点时钟

,

端点时钟

)

时钟是同步时钟还是异步时钟

?(

时钟关系

)

此路径是否跨多个

I/O

列

?(

IO

交汇

)

为了在

AMD Vivado

™

IDE

中直观显示时序路径及其布局

/

布线的详细信息

,

您必须使用以下命令

: report_timing -max_paths 50 -setup -input_pins -name worstSetupPaths

这些路径按裕量排序

,

并按“

Setup Path Characteristics

”表中的相同顺序

(

如上图所示

)

显示。

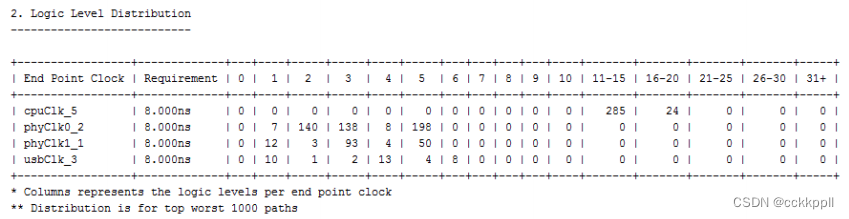

report_design_analysis

还可为最差的

1000

条路径生成“

Logic Level Distribution

”

(

逻辑层次分布

)

表

,

以供您用于识别设计中存在的长路径。通常最长的路径首先由布局器加以最优化以满足时序要求,

这可能导致较短的路径的布局质量劣化。您必须不断尝试消除较长的路径,

以提高整体

QoR

。下图显示了仅含

1

个时钟的设计的“

Logic Level Distribution”示例。

根据结果

,

可通过更改

RTL

或使用不同综合选项来改进网表

,

或者也可以修改时序约束和物理约束。

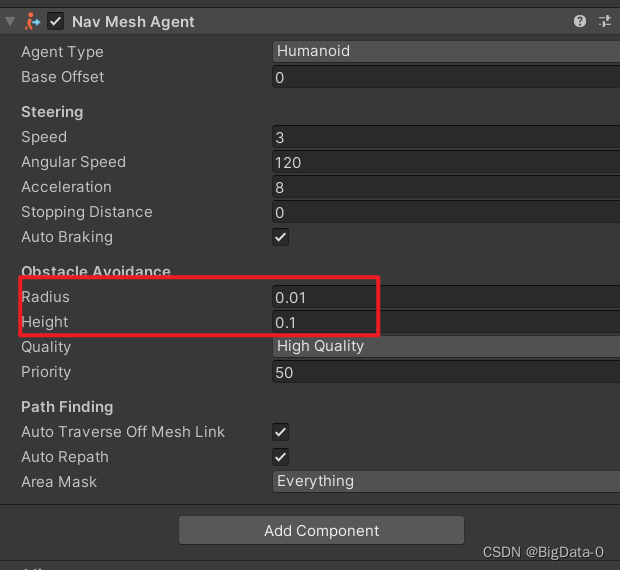

拥塞

report_design_analysis

命令用于报告多个拥塞表

,

其中显示布局器和布线器发现的拥塞区域。您可在运行布局器和布线器的 Vivado

工具会话内使用以下命令来生成这些表

:

report_design_analysis -congestion

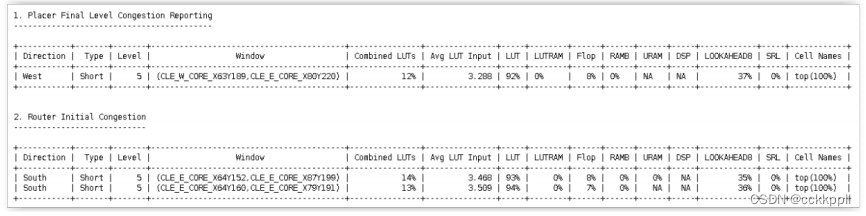

下图显示的拥塞表示例对应于布局器最终拥塞和布线器初始拥塞。

针对“

Module Names

”

(

模块名称

)

所提供的名称对应于每个报告的

tile

(

拼块

)

内存在的层级单元。您可使用以下命令来检索完整名称:

get_cells -hier <moduleName>

确认拥塞区域内存在的层级单元后

,

即可使用拥塞缓解技巧来尝试减少总体设计拥塞。