Quartus II 简易教程

- 一、概念回顾

- 二、创建设计工程

- 2.1 创建工程

- 2.2 新建HDL文件

- 三、编译工程

- 四、下载

一、概念回顾

- 什么是综合?什么是设计?

答:综合就是编译,设计就是布局布线。

二、创建设计工程

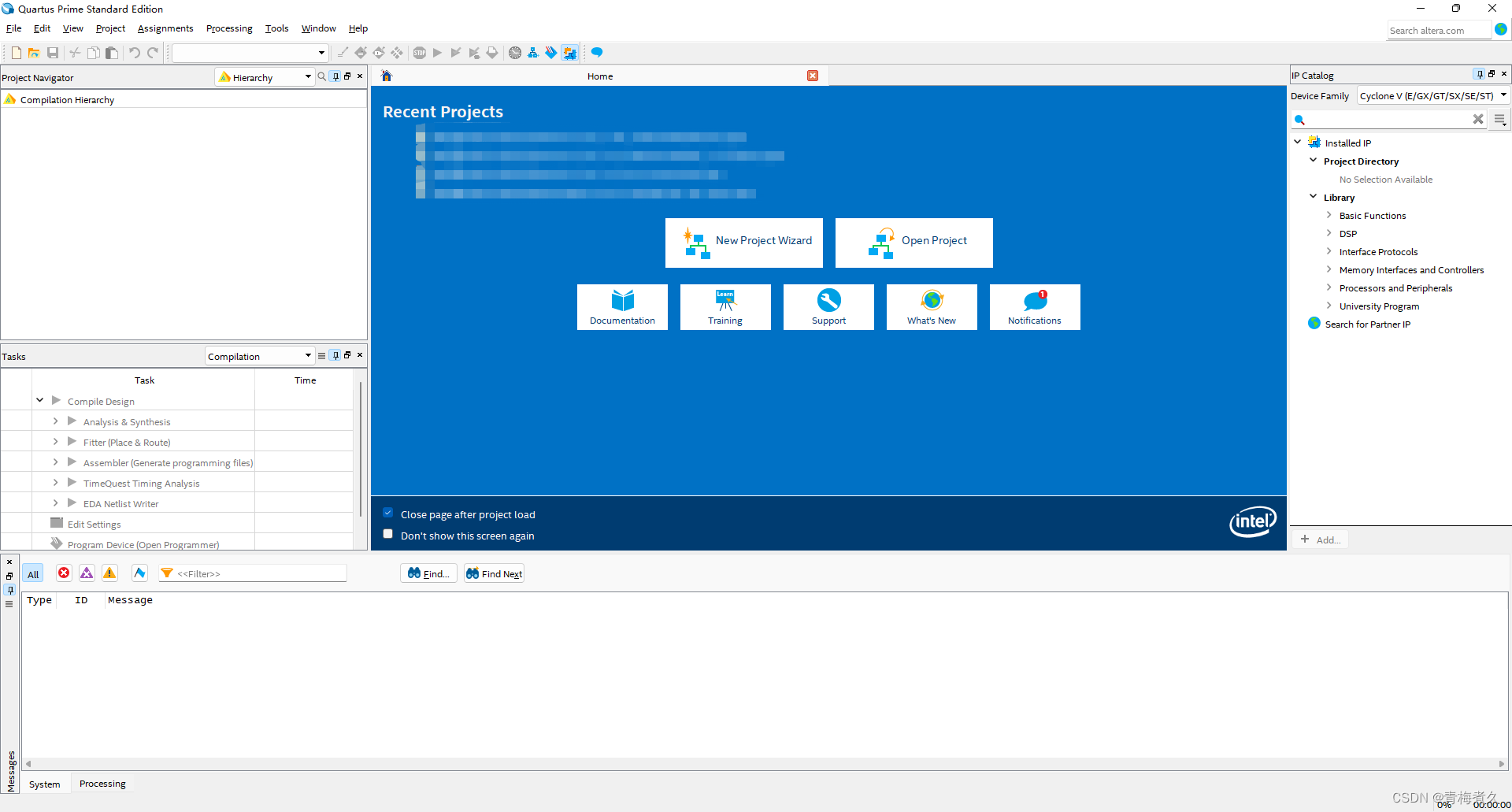

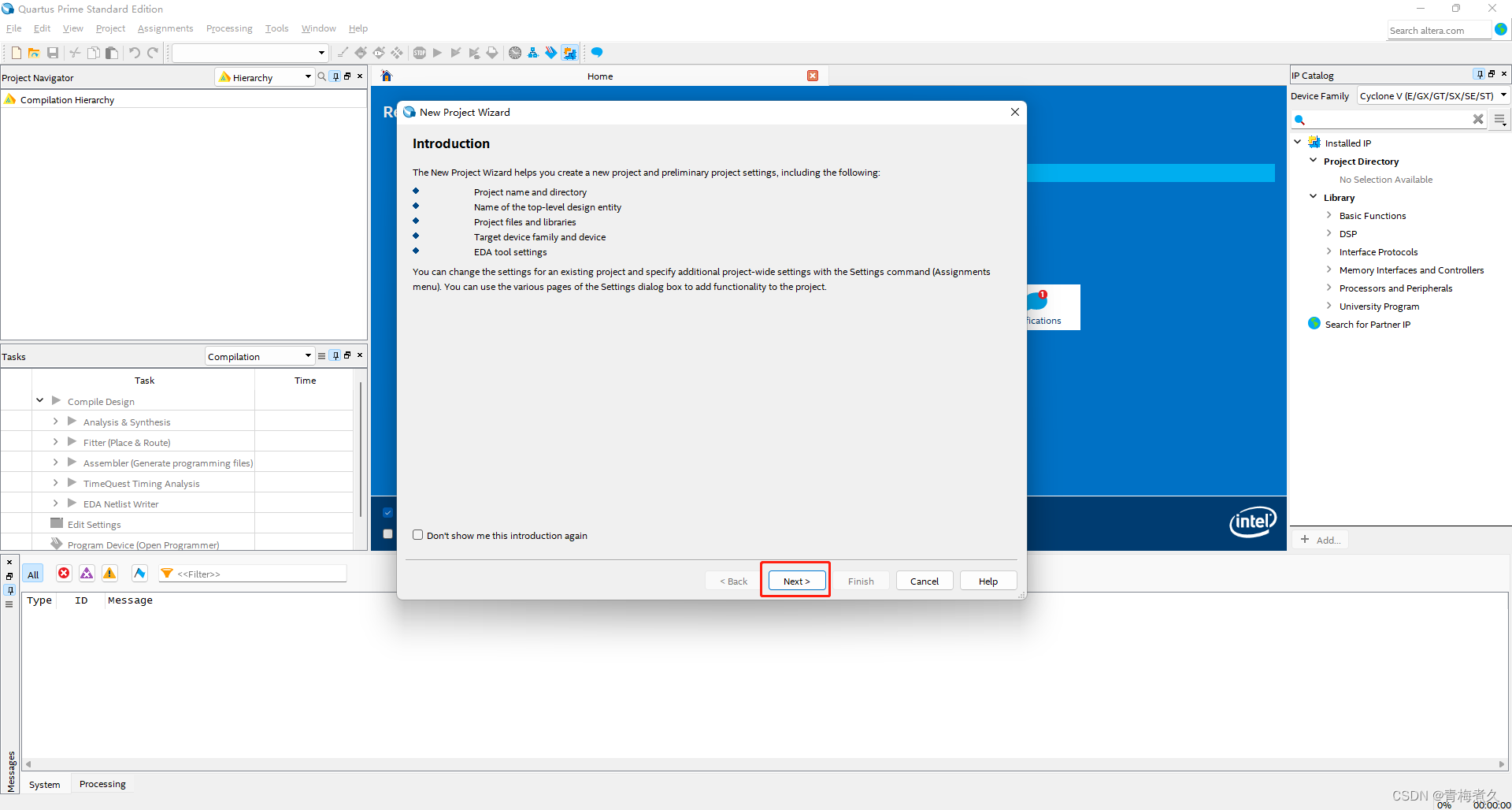

2.1 创建工程

- 打开Quartus II 软件。

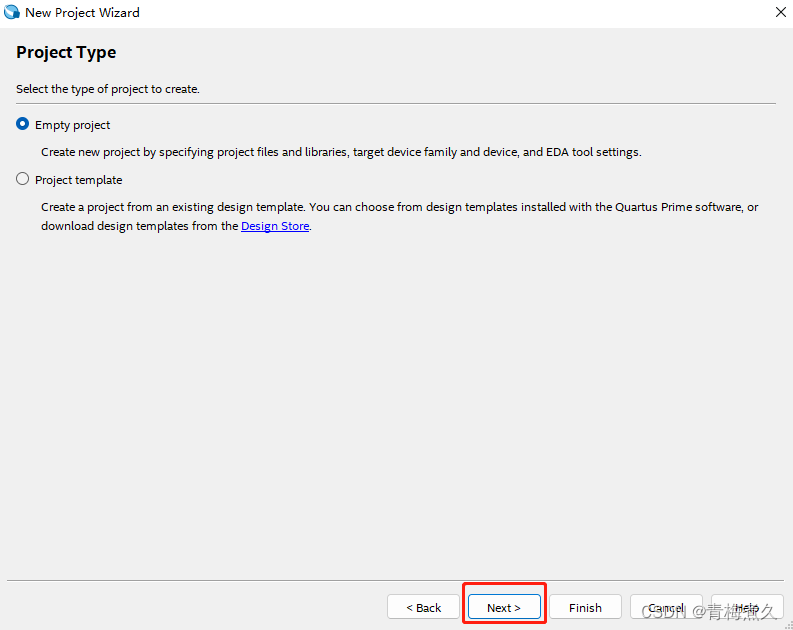

- 在Quartus II GUI中,选择File->New Project Wizard…,打开New Project Wizard对话框,单击Next进入下一页面,输入存储路径名,并输入工程名为demo_LED。

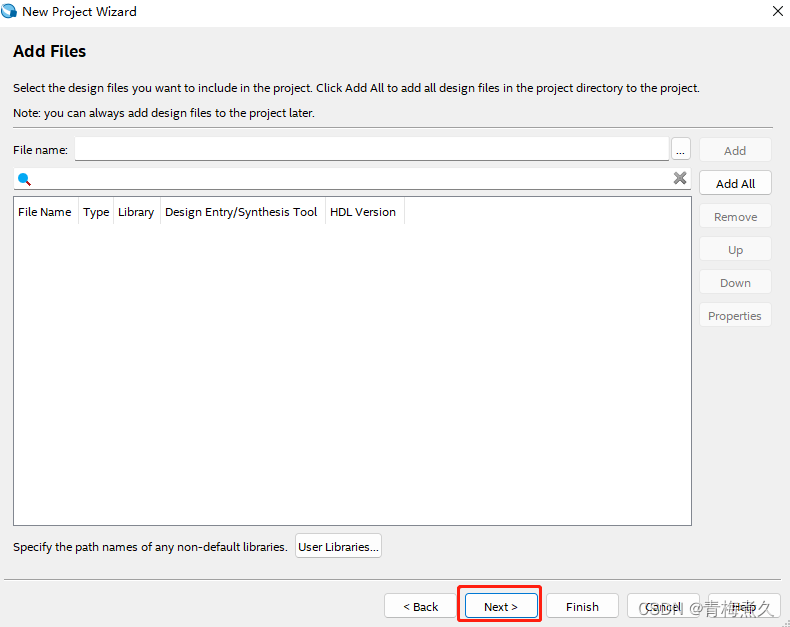

添加已有的源代码文件,没有的话,点Next(这里我没有代码)

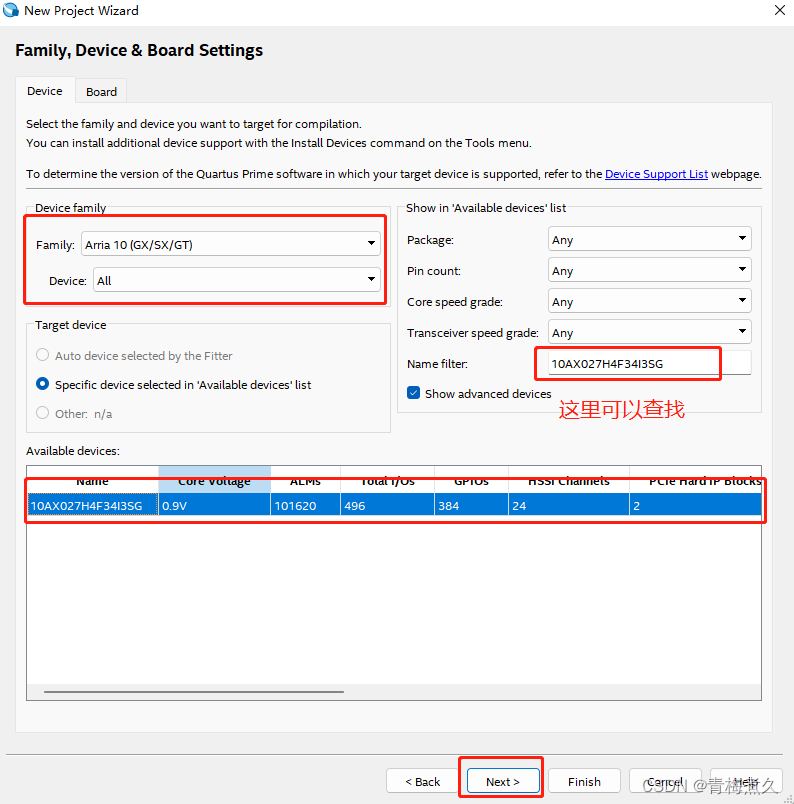

- 单击Next进入下一页面,选FPGA型号,根据你FPGA芯片上印刷的型号选择。

比如,我使用的芯片型号如下:

Family: Arria 10

Device:10AX027H4F34I3SG。

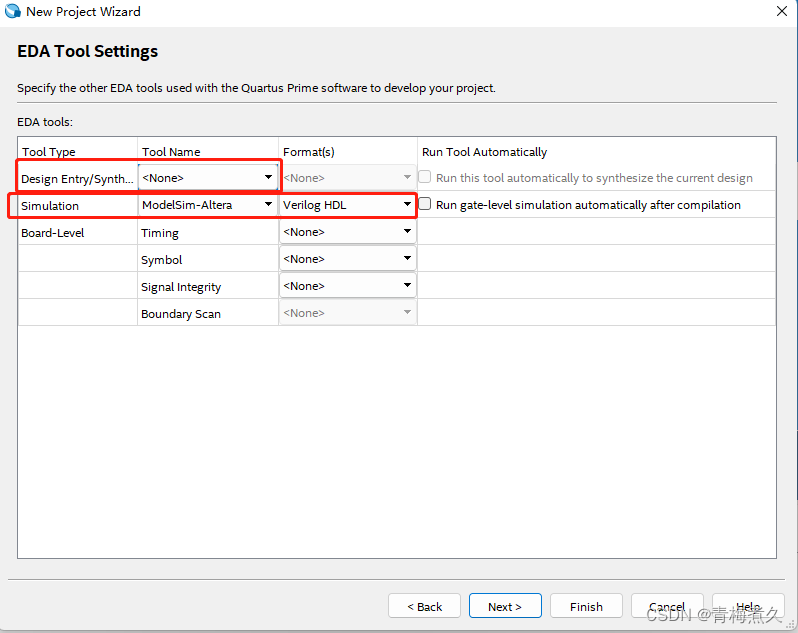

- 选择综合、仿真、时序分析工具. 此处如果全部选择None,表示用Quartus自带的工具。

我们综合用的自带的,仿真使用Modelsim,需要安装这个软件。

到此,创建完成。

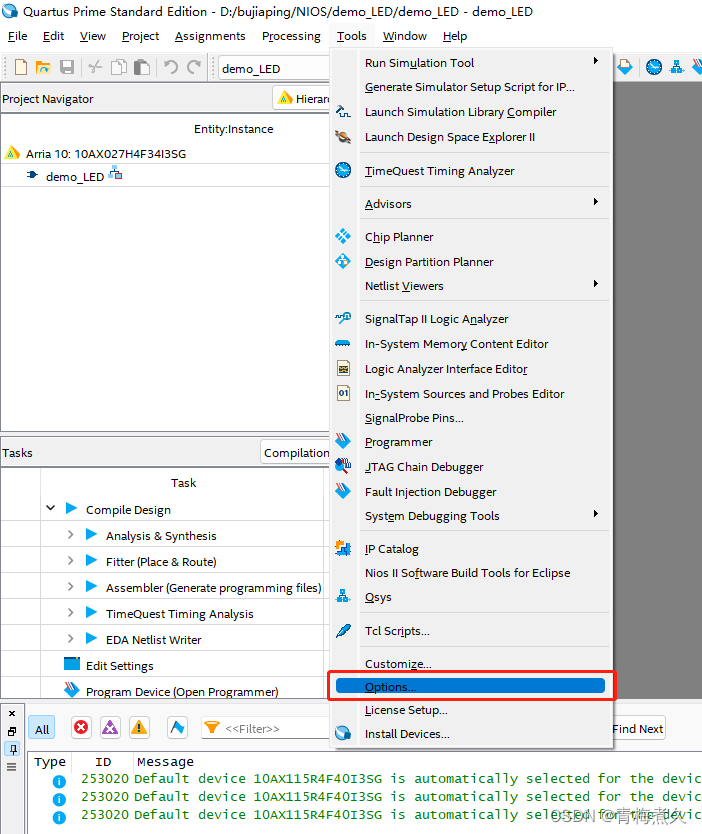

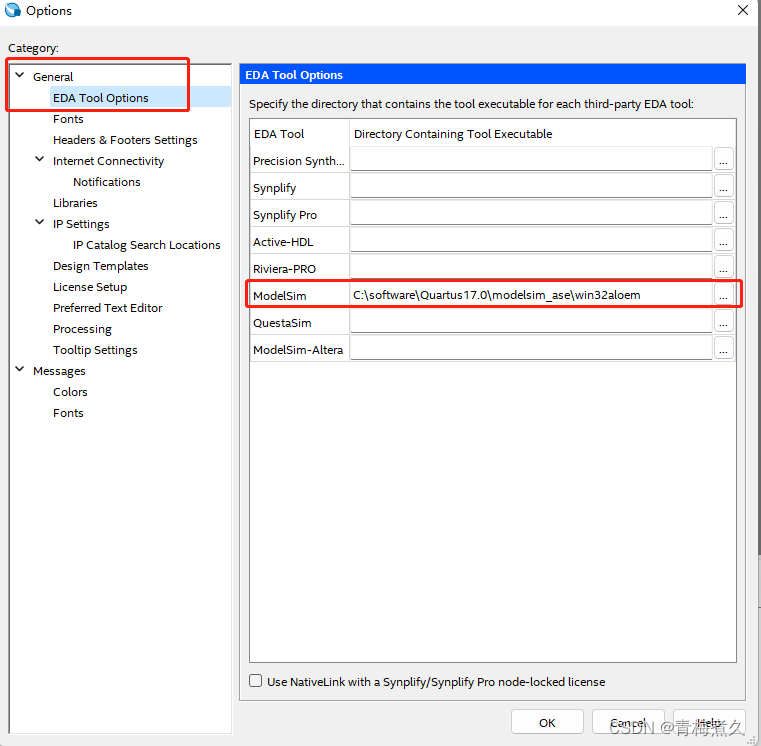

Modelsim查看如下:

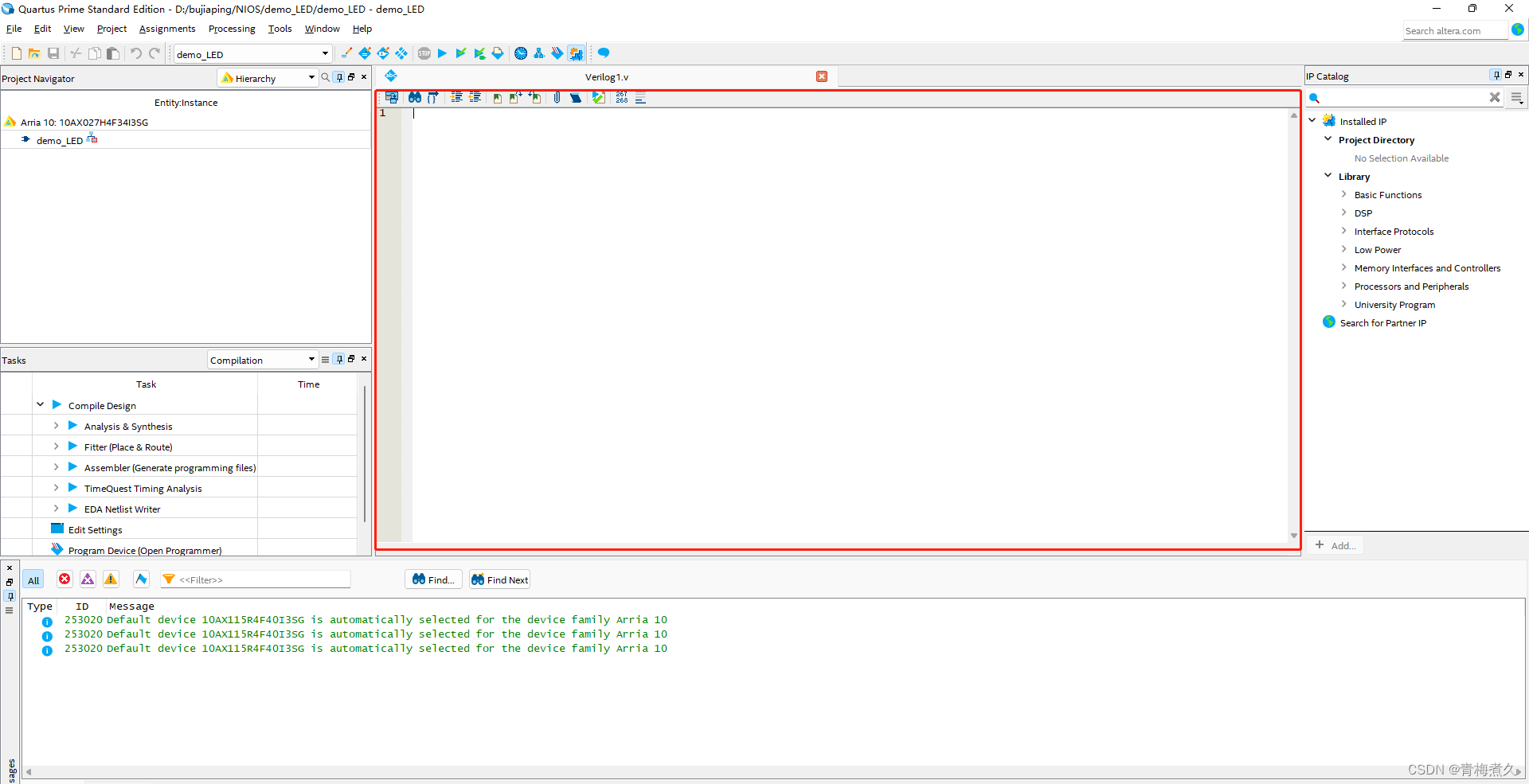

2.2 新建HDL文件

一个工程可能包含一个或多个HDL(硬件描述语言)文件。如果没有,则要新建源文件。

-

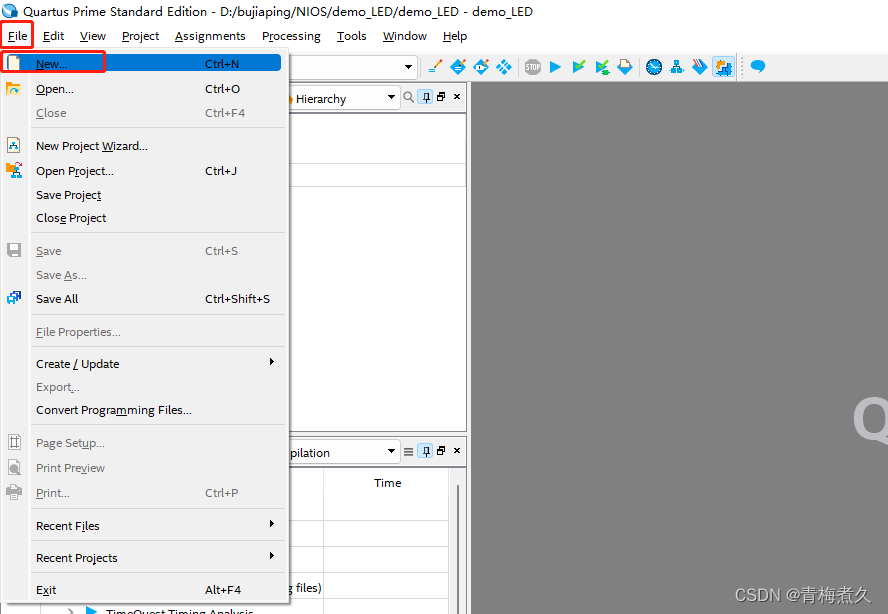

选择File->New,打开对话框。

-

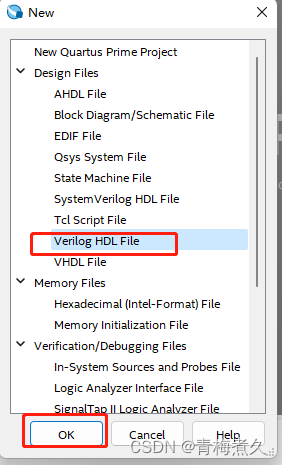

选择Verilog HDL file,单击OK。一个新的文本编辑器窗口就出现在工作区。

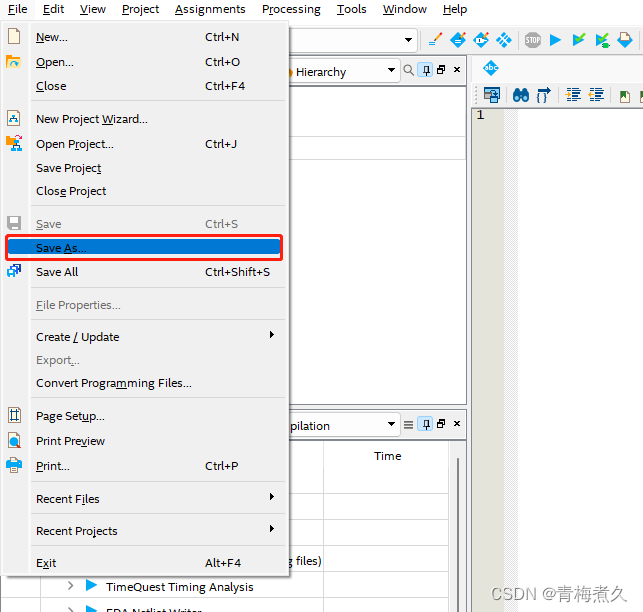

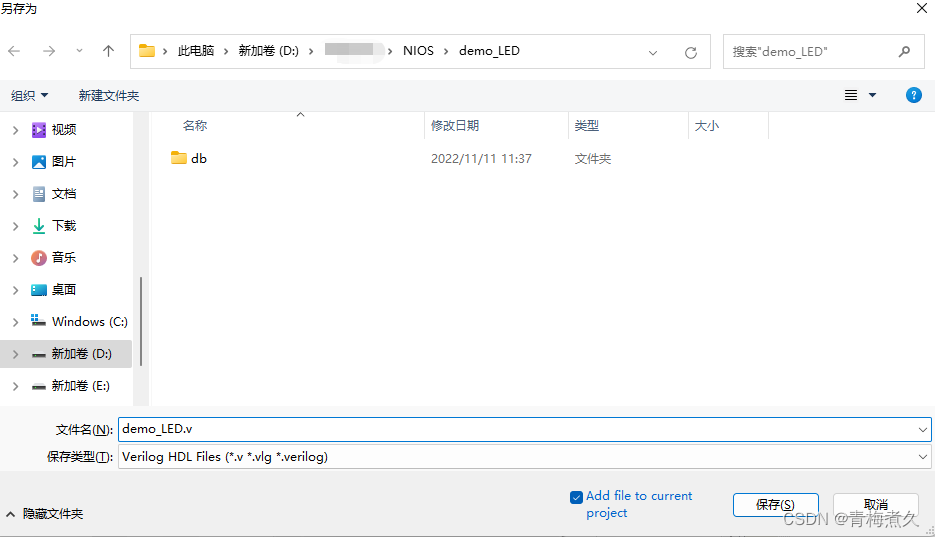

-

选择File->Save,打开Save as对话框,保存时,文件名要与module后面定义的实体名一致。即,保存demo_LED.v到你的工程文件夹内。

-

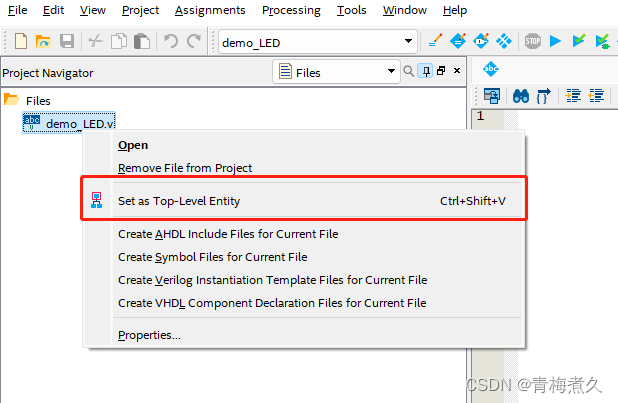

将该文件设置为顶层文件。

一个工程内,可以有多个源代码文件。但只有一个是顶层文件,代表最顶层设计,它可以引用工程目录内的其他源文件。 -

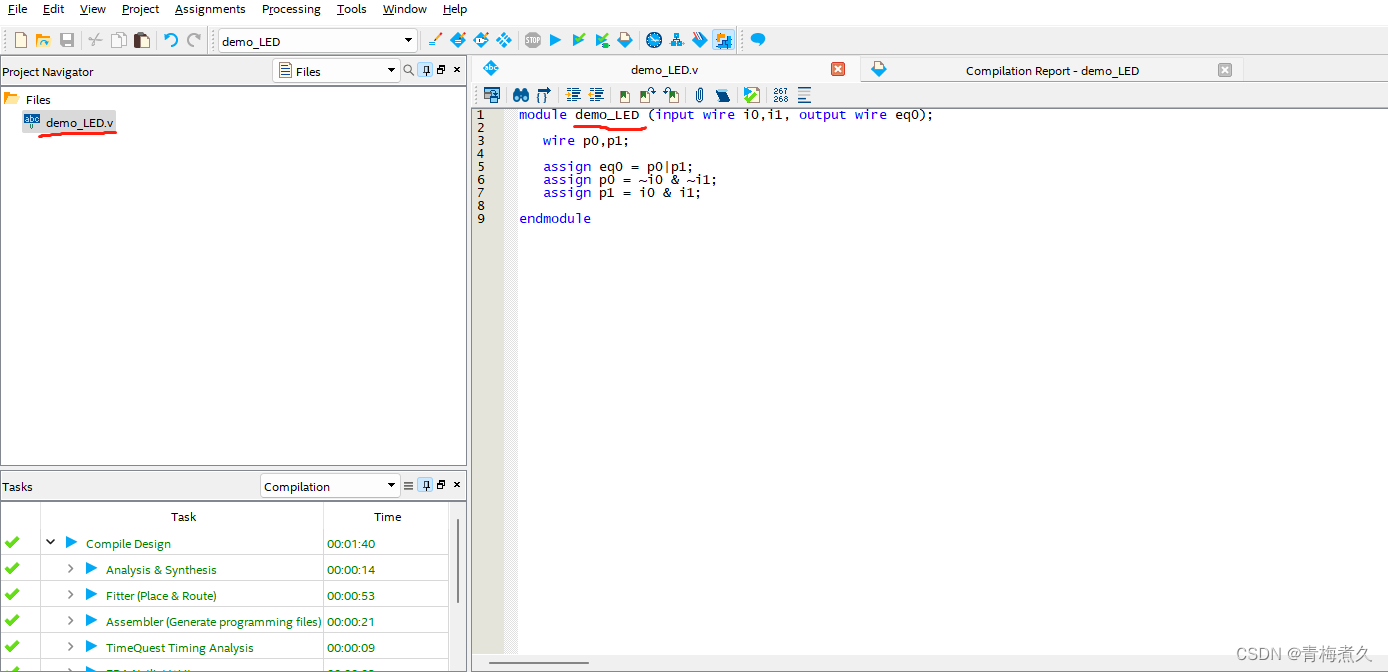

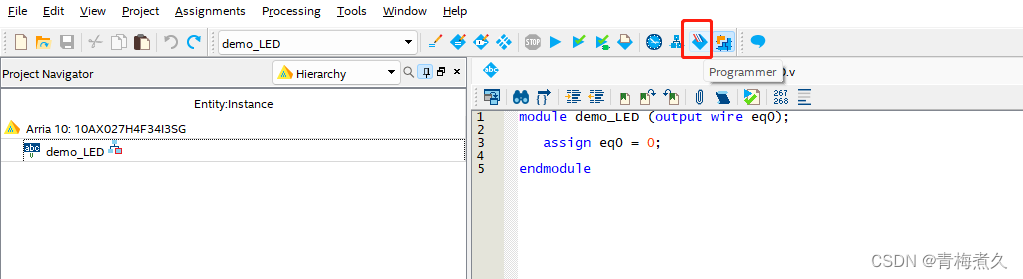

写代码,把灯点亮

module demo_LED (output wire eq0);

assign eq0 = 1;

endmodule

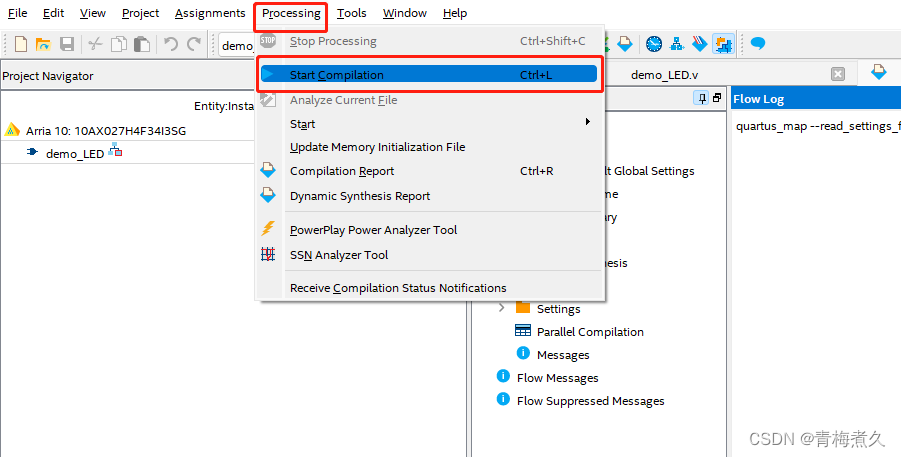

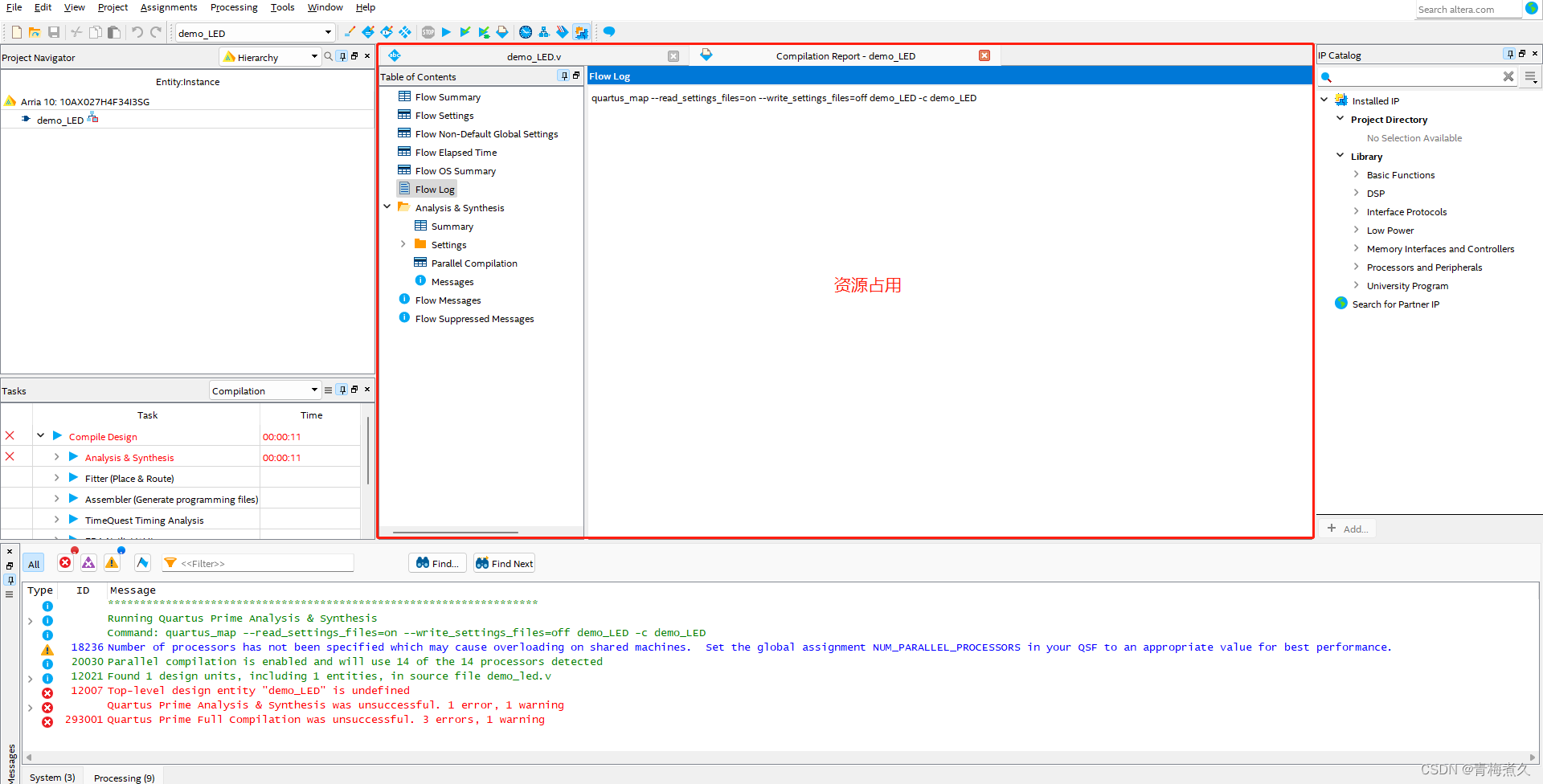

三、编译工程

编译:Processing–>Start Compilation

报错了,因为下图名字要一致。

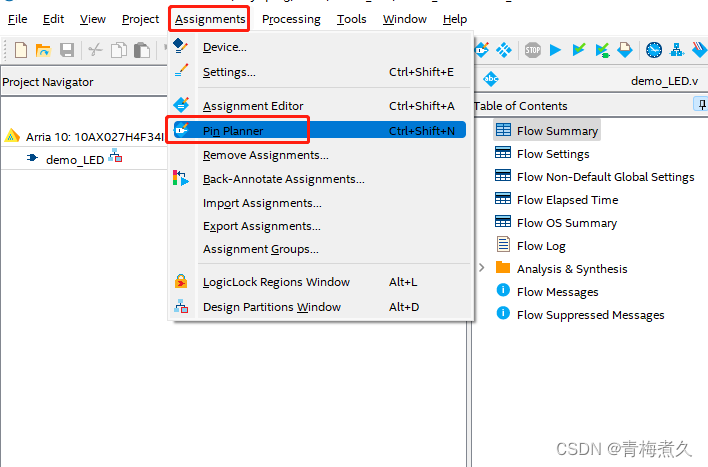

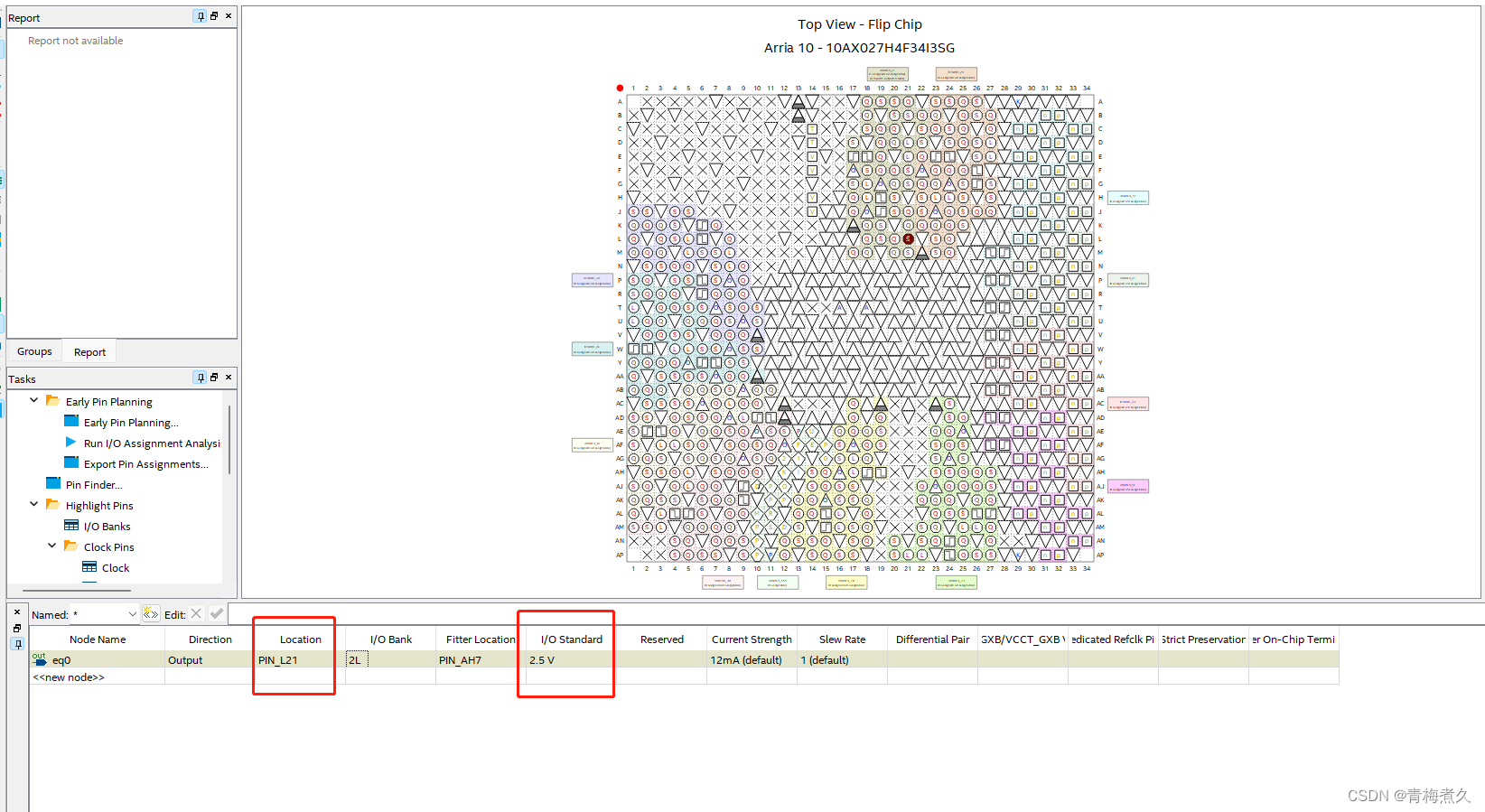

分配引脚操作:Assignment -> Pin Planner,如图。分配完引脚,关闭窗口,重新编译工程。

搞完后保存重新编译。

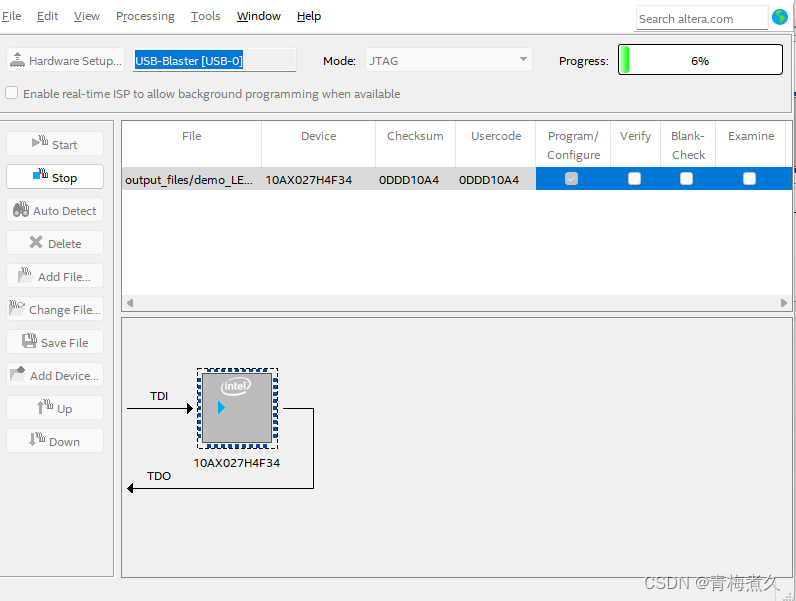

四、下载

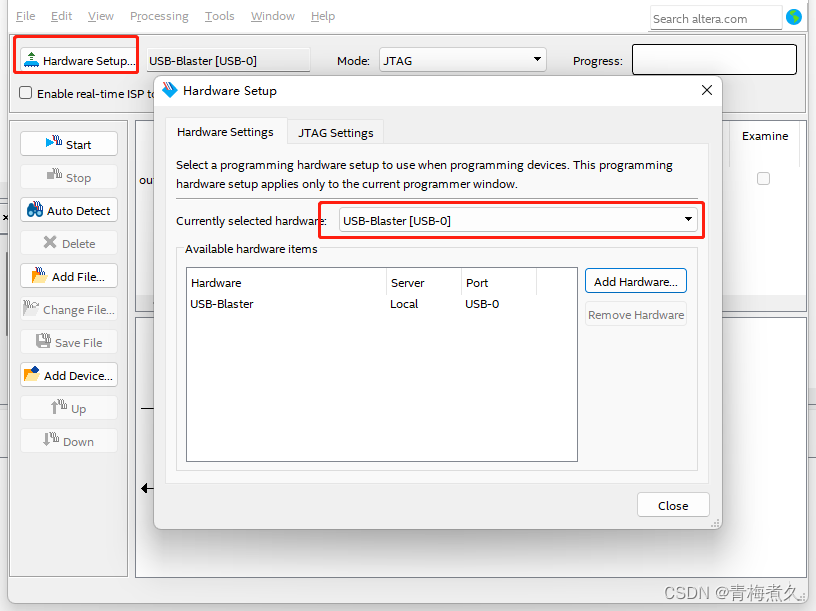

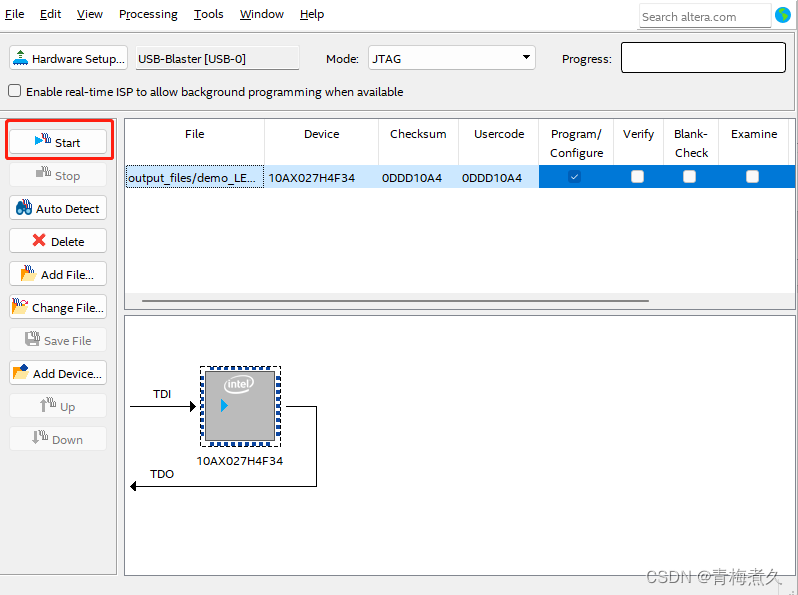

菜单Tools -> Programmer,如下图

• 由 青梅煮久 写于 2022 年 11 月 17 日

• 参考:

https://blog.csdn.net/Alexanderrr/article/details/51615254

![[附源码]java毕业设计静谧空间自习室预订系统](https://img-blog.csdnimg.cn/6cb003ccc2e8438a82deb1695780eee2.png)