专栏前言

本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网

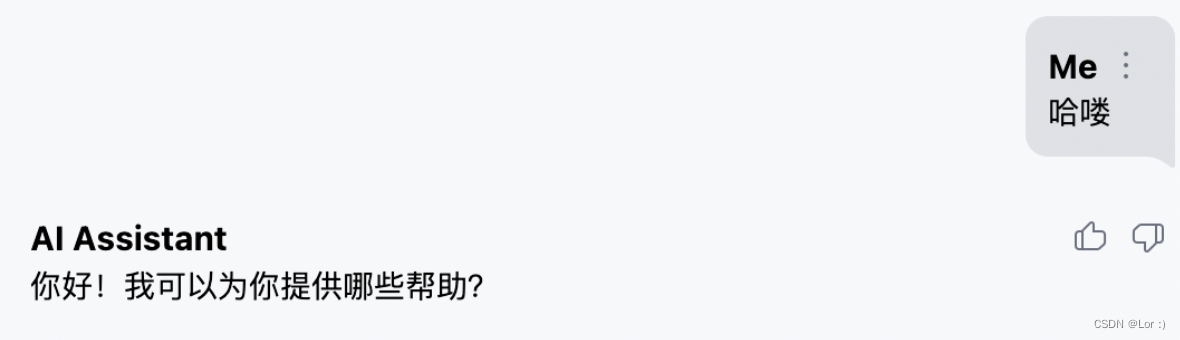

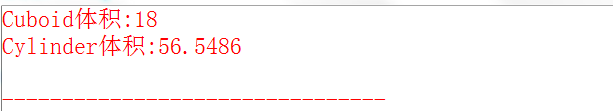

分析

要实现ROM,首先要声明数据的存储空间,例如:[3:0] rom [7:0];变量名称rom之前的[3:0]表示每个数据具有多少位,指位宽;变量名称rom之后的[7:0]表示需要多少个数据,指深度,注意这里深度为8,应该是使用[7:0],而不是[2:0]

声明存储变量之后,需要对rom进行初始化,写入数据,然后将输入地址作为rom的索引值,将索引值对应的数据输出。

`timescale 1ns/1ns

module rom(

input clk,

input rst_n,

input [7:0]addr,

output [3:0]data

);

reg [3:0] rom_data [7:0] ;

assign data = rom_data[addr] ;

always @ (posedge clk or negedge rst_n) begin

if (!rst_n) begin

rom_data[0] <= 4'd0 ;

rom_data[1] <= 4'd2 ;

rom_data[2] <= 4'd4 ;

rom_data[3] <= 4'd6 ;

rom_data[4] <= 4'd8 ;

rom_data[5] <= 4'd10 ;

rom_data[6] <= 4'd12 ;

rom_data[7] <= 4'd14 ;

end

else begin

rom_data[0] <= rom_data[0] ;

rom_data[1] <= rom_data[1] ;

rom_data[2] <= rom_data[2] ;

rom_data[3] <= rom_data[3] ;

rom_data[4] <= rom_data[4] ;

rom_data[5] <= rom_data[5] ;

rom_data[6] <= rom_data[6] ;

rom_data[7] <= rom_data[7] ;

end

end

endmodule

![2023年中国中端连锁酒店分类、市场规模及主要企业市占率[图]](https://img-blog.csdnimg.cn/img_convert/b42814840a4a5db09e41cdde844cda44.png)

![2023年中国地产SaaS分类、产业链及市场规模分析[图]](https://img-blog.csdnimg.cn/img_convert/348ffe3aaf12c6229b617458217ab32a.png)

![2023年中国稀土精密加工分类、市场规模及发展趋势分析[图]](https://img-blog.csdnimg.cn/img_convert/48050d3e4088fb3248d8a6b0a8fc559d.png)

![2023年中国全自动烘干机产业链、产能及发展趋势分析[图]](https://img-blog.csdnimg.cn/img_convert/33ebfbf423b6f30570d8c56283520003.png)