1、Report I/O

“

I/O Report

”

(

I/O

报告

)

用于替代

AMD ISE Design Suite PAD

文件。“

I/O Report

”可列出

:

• “

Pin Number

”

(

管脚编号

):

表示器件中的所有管脚

• “

Signal Name

”

(

信号名称

):

表示分配给管脚的用户

I/O

的名称

• “

Bank Type

”

(

bank

类型

):

表示

I/O

所在的

bank

类型

,

类型包括

:

“

High Range

”

(

高量程

)

、“

High Performance”

(

高性能

)

、“

Dedicated

”

(

专用

)

等

• “

Pin Name

”

(

管脚名称

):

表示管脚名称

• “

Use

”

(

用途

):

表示

I/O

使用类型

,

类型包括

:

“

Input

”

(

输入

)

、“

Output

”

(

输出

)

、“

Power/

Ground

”

(

功耗

/

接地

)

、“

Unconnected

”

(

未连接

)

等

• “

I/O Standard

”

(

I/O

标准

):

表示用户

I/O

的

I/O

标准 任意星号 (*)

均表示默认值。这不同于

Vivado IDE

的“

I/O Ports

”

(

I/O

端口

)

窗口。

• “

I/O Bank Number

”

(

I/O bank

编号

):

表示管脚所在的

I/O bank

• “

Drive (mA)

”

(

驱动

):

表示驱动强度

(

以毫安为单位

)

• “

Slew Rate

”

(

压摆率

):

表示缓冲器的压摆率配置

,

值为

Fast

或

Slow

• “

Termination

”

(

终端

):

表示片上

/

片外终端设置

• “

Voltage

”

(

电压

):

表示各管脚的值

,

包括

VCCO

、

VCCAUX

和相关管脚

• “

Constraint

”

(

约束

):

如果管脚已由用户约束

,

则显示为“

Fixed

”

• “

Signal Integrity

”

(

信号完整性

):

表示管脚的信号完整性

2、Report Clock Utilization

“

Clock Utilization

”

(

时钟使用率

)

报告可帮助您分析器件内时钟区域级别或时钟信号线级别的时钟原语和布线资源的使用率。它可用于调试时钟布局问题,

并识别布局约束

,

从而最大限度提升资源使用率。“

Clock Utilization

”报告提供如下相关信息:

• 可用和已用时钟原语的数量及其物理约束

• 与每条时钟信号线关联的时序时钟名称和周期

• 每个时钟区域的时钟设置和互连结构负载使用率

• 每个时钟区域内的每条时钟信号线的负载

此外

,

Vivado IDE

中的“

Clock Utilization

”

(

时钟使用率

)

报告支持选择网表和器件对象

,

以便高亮显示布局信息和创建板级原理图。

3、“

Clock Utilization

”报告表

此报告提供了时钟拓扑和布局信息

,

按类别组织

:

• 时钟原语使用率

• 全局时钟资源

• 全局时钟源详情

• 局部时钟资源

• 时钟区域使用率详情

• 全局时钟布局详情

由于典型设计中网表对象名称较长且时钟信号线和时钟原语数量庞大

,

因此对特定时钟资源分配短

ID

:

• 针对时钟缓冲器驱动的每条信号线分配唯一全局

ID

“

g<n>

”

• 针对时钟生成器

(

例如

,

MMCM

或输入缓冲器

)

分配唯一源

ID

“

src<n>

”。

• 对于不使用全局时钟资源布线的时钟信号分配唯一局部

ID

“

<n>

”。

“

Global Source ID

”

(

全局源

ID

)

和“

Local ID

”

(

局部

ID

)

可简化整个报告中特定时钟信号线的搜索操作。在每个表的最后 2

列

(

如果适用

)

中提供了原始网表对象名称。

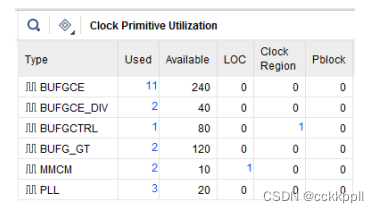

4、“

Clock Primitive Utilization

”表

“

Clock Primitive Utilization

”

(

时钟原语使用率

)

表可显示每种时钟原语类型及其物理约束的使用率汇总信息。

“

Global Clock Resources

”

(

全局时钟资源

)

表仅显示每个时钟信号线的汇总信息

(

包括重要的约束和布局信息

),

“

Global Clock Source Details

”

(

全局时钟源详情

)

表显示了每个时钟生成器输出的全局时钟连接和时序时钟信息。

5、Local Clock Details

”表

仅当设计中发现局部时钟时

,

才会报告“

Local Clock Details

”

(

局部时钟详情

)

表。局部时钟表示以常规互连结构布线资源而不是全局时钟资源进行布线的时钟信号线。通常当时钟信号线不受时钟缓冲器驱动时会发生这种情况。

“

Clock Regions

”

(

时钟区域

)

部分仅适用于

UltraScale

器件系列

,

其中包含的几张表提供了每个时钟区域的原语和布线资源使用率。

“

Clock Regions

”表包括

:

• “

Clock Primitives

”

(

时钟原语

):

每个时钟区域内的每种时钟原语类型的使用率。

• “

Load Primitives

”

(

负载原语

):

每个时钟区域内非时钟时序原语的使用率。

对于“

Clock Primitives

”和“

Load Primitives

”表

,

“

Global Clock

”

(

全局时钟

)

列可显示水平分布层上布线的全局时钟信号线的数量,

包括所报告的时钟区域内含负载和不含负载的信号线。如果时钟信号线在垂直分布层上已布线

,

但未分叉到所报告的时钟区域内的水平层,

则不纳入计数范围。布线层上已布线的时钟信号线不纳入计数范围。

6、“

Key Resource Utilization

”表

“

Key Resource Utilization

”

(

关键资源使用率

)

表仅适用于

7

系列器件

,

它等同于对应

UltraScale

器件的所有“Clock Regions

”

(

时钟区域

)

表的组合。“

Global Clock Summary

”

(

全局时钟汇总

)

表同样只能以文本报告方式显示。

7、“

Global Clocks

”表

“

Global Clocks

”

(

全局时钟

)

表用于报告每个全局时钟信号线的每个时钟区域中的负载类型

,

以及用于完成时钟信号线布线的时序时钟信息和时钟轨道 ID

。在

Vivado IDE

中按“

Global ID

”

(

全局

ID

)

进行排序时

,

只需选中表中对应的行即可轻松识别并高亮显示器件中的时钟区域,

在这些区域中可对每条全局时钟信号线进行布线。