【LittleXi】C程序预处理、编译、汇编、链接步骤

C程序

#include<stdio.h>

int main(){

int x=1,y=1;

printf("x+y=%d",x+y);

}

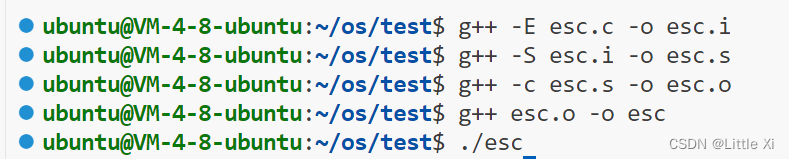

1、预处理

将头文件引入进来、除去注释、宏定义下放

执行指令

g++ -E esc.c -o esc.i

2、编译

将处理好的代码编译为汇编代码.s

执行指令

g++ -S esc.i -o esc.s

3、汇编

将编译好的.s文件转为机器码.o

执行指令

g++ -c esc.s -o esc

4、链接

- 链接是将多个目标文件和库文件组合成最终的可执行文件的过程。

- 链接器(如GNU链接器,通常称为

ld)执行这一过程,解决了不同目标文件之间的符号引用关系,将它们连接在一起。 - 主要任务包括解析符号引用、符号解析、符号重定位、生成可执行文件。

- 如果使用了外部库(如标准C库),链接器还会将所需的库文件与程序一起链接,以满足程序的依赖性。

执行指令

g++ esc.o -o esc

5、补充,也可以自己写Makefile文件,示例如下

文件main.c

// main.c

#include <stdio.h>

#include "library.h"

int main() {

int result = add(3, 5);

printf("Result: %d\n", result);

return 0;

}

文件library.h

// library.h

#ifndef LIBRARY_H

#define LIBRARY_H

int add(int a, int b);

#endif

文件library.c

// library.c

#include "library.h"

int add(int a, int b) {

return a + b;

}

Makefile文件

CC = g++

CFLAGS = -Wall -std=c++11

SRC = main.cpp library.cpp

OBJS = $(SRC:.cpp=.o)

TARGET = main

all: $(TARGET)

$(TARGET): $(OBJS)

$(CC) $(CFLAGS) $^ -o $@

%.o: %.cpp

$(CC) $(CFLAGS) -c $< -o $@

clean:

rm -f $(OBJS) $(TARGET)

.PHONY: all clean

解释

CC = g++:- 这一行定义了一个Makefile变量

CC,它指定了C++编译器的名称。在这个示例中,我们使用g++作为C++编译器。

- 这一行定义了一个Makefile变量

CFLAGS = -Wall -std=c++11:- 这一行定义了一个Makefile变量

CFLAGS,它包含了编译选项。-Wall表示启用所有警告,-std=c++11指定了C++11标准。

- 这一行定义了一个Makefile变量

SRC = main.cpp library.cpp:- 这一行定义了一个Makefile变量

SRC,包含了项目的所有源文件的名称。

- 这一行定义了一个Makefile变量

OBJS = $(SRC:.cpp=.o):- 这一行定义了一个Makefile变量

OBJS,它是SRC中所有源文件的目标文件的列表。.cpp文件扩展名被替换为.o文件扩展名。

- 这一行定义了一个Makefile变量

TARGET = main:- 这一行定义了一个Makefile变量

TARGET,表示最终的可执行程序的名称。

- 这一行定义了一个Makefile变量

all: $(TARGET):- 这是一个Makefile规则,表示

all是默认的目标。当你运行make命令时,它将构建$(TARGET)。

- 这是一个Makefile规则,表示

$(TARGET): $(OBJS):- 这是一个Makefile规则,定义了如何从目标文件构建可执行程序。

$(OBJS)表示依赖于目标文件列表。规则中的命令$(CC) $(CFLAGS) $^ -o $@使用g++编译器编译目标文件,并将其链接为可执行程序。

- 这是一个Makefile规则,定义了如何从目标文件构建可执行程序。

%.o: %.cpp:- 这是一个Makefile规则,定义了如何将每个源文件编译成对应的目标文件。

%.o表示所有的目标文件,%.cpp表示对应的源文件。规则中的命令$(CC) $(CFLAGS) -c $< -o $@编译每个源文件为对应的目标文件。

- 这是一个Makefile规则,定义了如何将每个源文件编译成对应的目标文件。

clean:- 这是一个Makefile规则,用于清理生成的目标文件和可执行程序。命令

rm -f $(OBJS) $(TARGET)删除目标文件和可执行程序。

- 这是一个Makefile规则,用于清理生成的目标文件和可执行程序。命令

.PHONY: all clean:- 这一行告诉Make工具,

all和clean是伪目标,不代表实际文件,因此不会检查它们的时间戳。这样可以确保make始终执行这两个目标,而不受文件时间戳的干扰。

- 这一行告诉Make工具,