文章目录

- cadence SPB17.4 - 从正常PCB文件反推原理图

- 概述

- 笔记

- 用SPB17.4 allegro 出报表

- 剩余的事情

- 最重要的一件事情 - 核对整理出的原理图是否和PCB原图网络一致

- 最后的事情

- 备注

- END

cadence SPB17.4 - 从正常PCB文件反推原理图

概述

和同学讨论问题, 他那有一个可以正常生产的立创格式的离线PCB工程文件(.json)和对应的固件工程的源码.

但是没有原理图, 我不方便问为啥没有原理图.

他要求我从这个立创格式的PCB将原理图反推出来. 因为我们要用这个原理图和硬件, 来看固件程序是否可以正常运行, 如果不正常, 需要去修正固件工程.

笔记

打开网页版立创标准版, 导入本地的立创jsonPCB文件.

导出AD格式的PCB文件到本地.

将AD格的PCB用AD22转成ascii格式的PCB文件.

用SPB17.4 allegro 引入AD格式的ascii PCB.

用SPB17.4 allegro 打开转好的PCB文件.

用SPB17.4 allegro 导出封装.

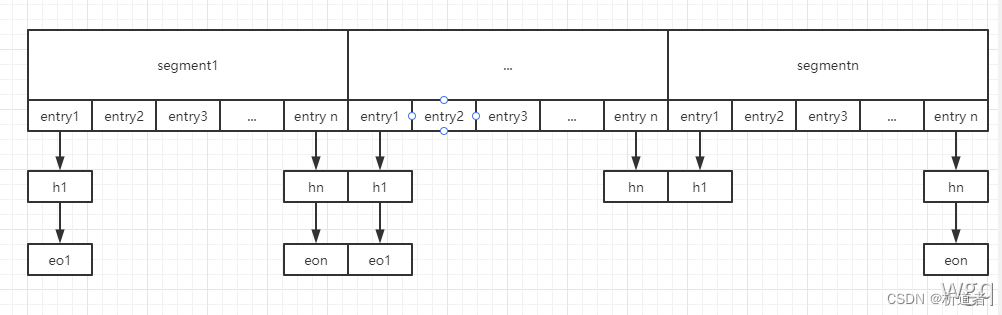

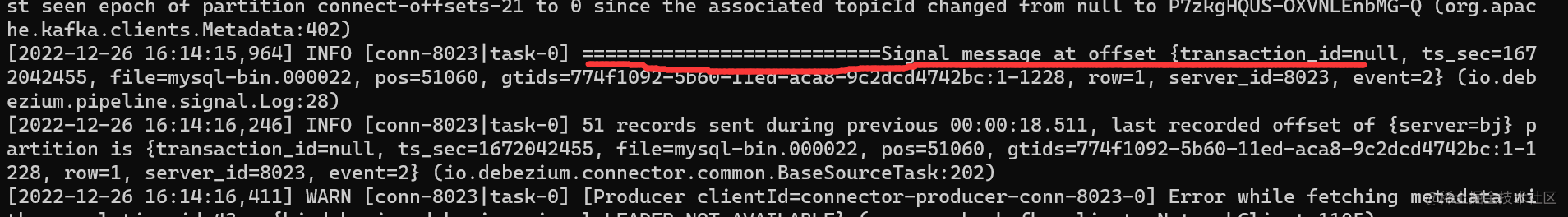

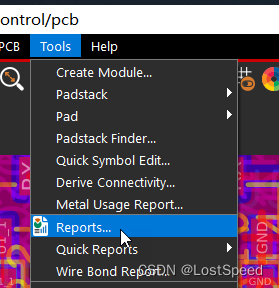

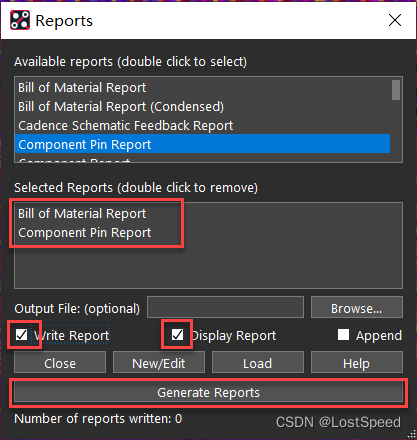

用SPB17.4 allegro 出报表

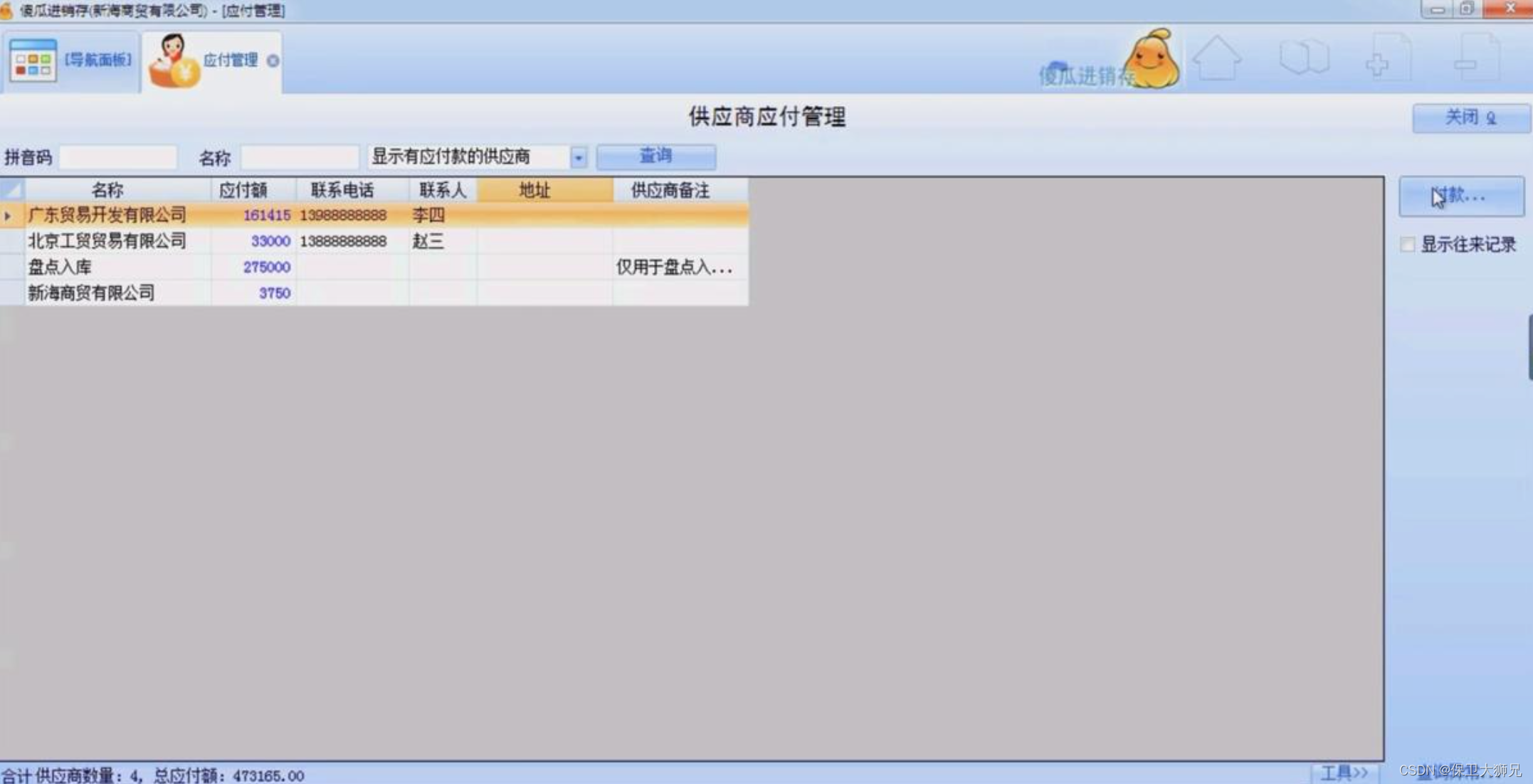

报表一共出2种:

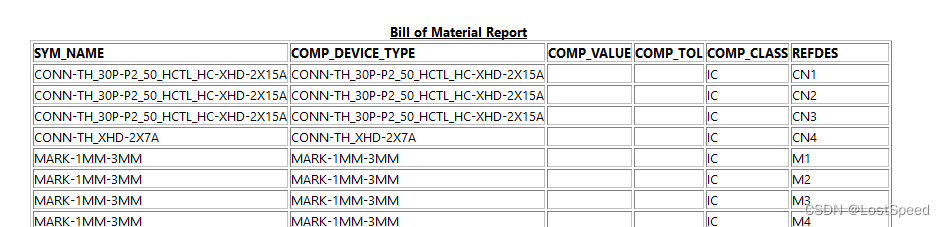

Bill of Material Report : BOM料单, 这样就可以根据导出的封装, 将封装库丢到全局封装目录; 将CIS库中的这个工程对应的原理图元件封装做好, CIS库表填好.

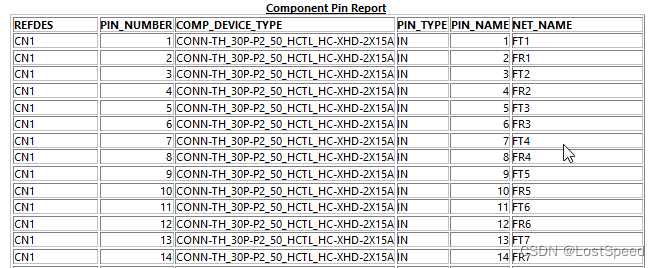

Component Pin Report : 元件管脚报告, 每个管脚网络名称都有.

到此, 就可以将所有元件都通过放置数据库元件(Z), 将板子所有的元件都摆好, 在每个元器件的管脚上都放上网络标号.

剩余的事情

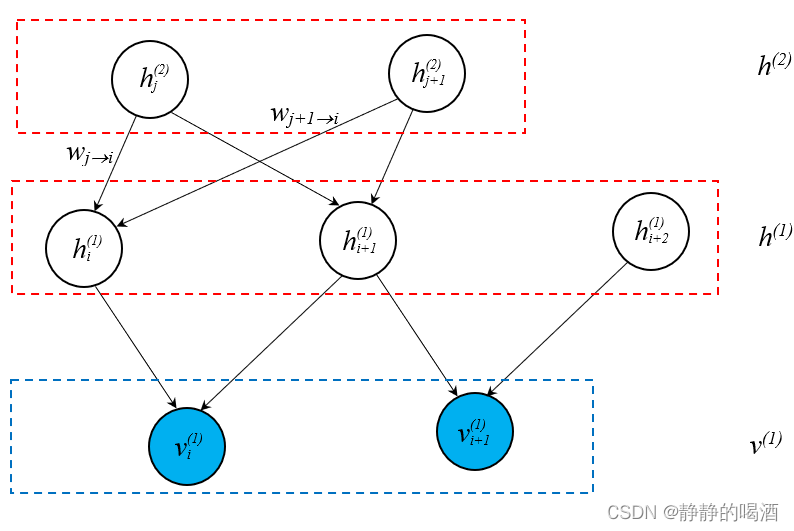

根据网络标号指明的逻辑关系, 将相同的网络标号拉到相近位置, 用电气连线, 将相同网络的管脚连接起来.

按照逻辑, 将每个元件都连接成子电路.

将子电路放入不同的子原理图.

将出现在多个子原理图中的网络标号, 用页面连接符号引出.

原理图DRC, 消除所有错误和警告.

参照典型电路图或者低版本原理图, 将每个元件的值确定下来并替换.

原理图DRC, 消除所有错误和警告.

最重要的一件事情 - 核对整理出的原理图是否和PCB原图网络一致

做这步的原因: 防止手误/看错网表连接关系, 弄这上千次的器件网络标注, 想保证100%正确是很难的.

等原理图画完, 导出的网表是没办法和从原图中提出的网表比对的, 差异太多, 不像是AD格式的那么容易看.

最好的方法是: 在原理图上出网表, 然后导入到新建的PCB.

当元件全部放完后, 不用布线. 此时再生成报表 : Component Pin Report

与原始PCB导入allegro后, 产生的第一份 Component Pin Report 报表进行人肉比对, 这时, 差别的可能就是自己做的封装名称不同, 关键信息(元件管脚 + 元件管脚对应的网络)人肉看的还是很清楚的. 此时, 写个小程序来自动判断2份Component Pin Report是否关键信息一致, 也是可行的.

最后的事情

出BOM.

备注

从正常PCB反推原理图, 其实工作量还是蛮大的, 感觉也不好(主要是很累). 和电路的复杂性无关(都是机械式的操作, 完全不用思考).

元件越多, 工作量越大. 因为每个元件的每个管脚上的网络, 都要自己去手工填写.

这个PCB元件共379个, 元件管脚总共1086个. 将每个管脚上都按照PCB的报告都填上网络, 这就搞了1000多次.

总共花了4个工作日, 心疼一下自己.