AD9371 系列快速入口

AD9371+ZCU102 移植到 ZCU106 : AD9371 官方例程构建及单音信号收发

采样率和各个时钟之间的关系 : AD9371 官方例程HDL详解之JESD204B TX侧时钟生成 (三)

参考资料:

UltraScale Architecture GTH Transceivers User Guide UG576

Generic JESD204B block designs

文章目录

- 前言

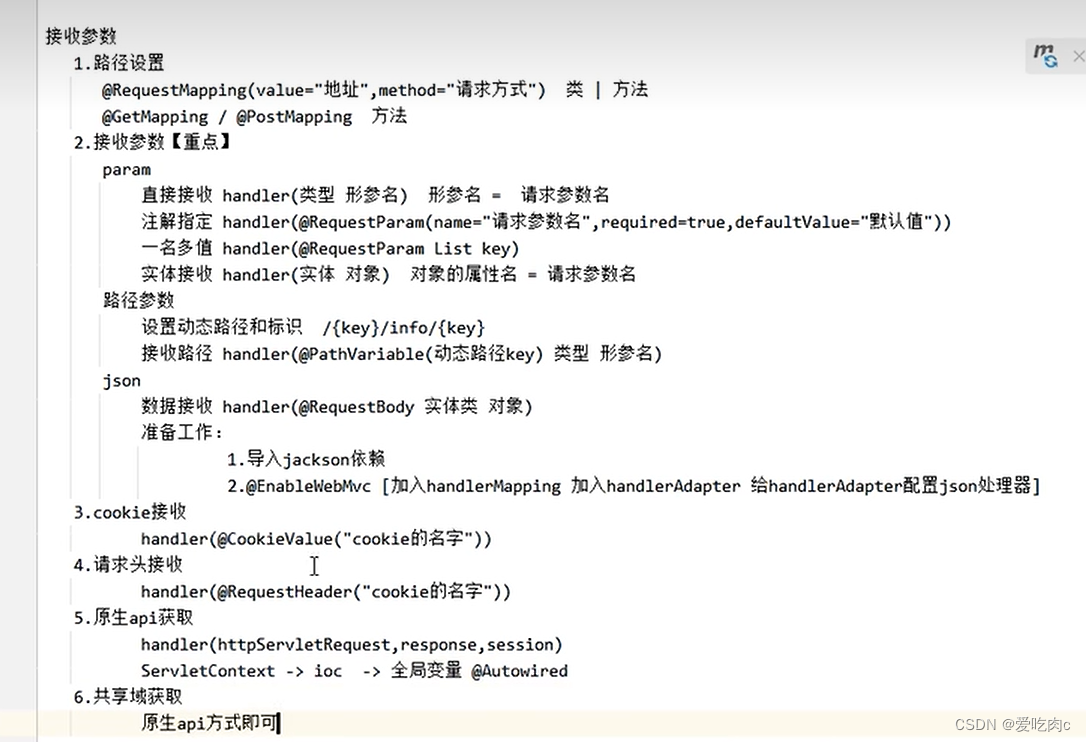

- 一、JESD204B传输层给应用层数据的格式配置

- 二、JESD204B链路数据配置

前言

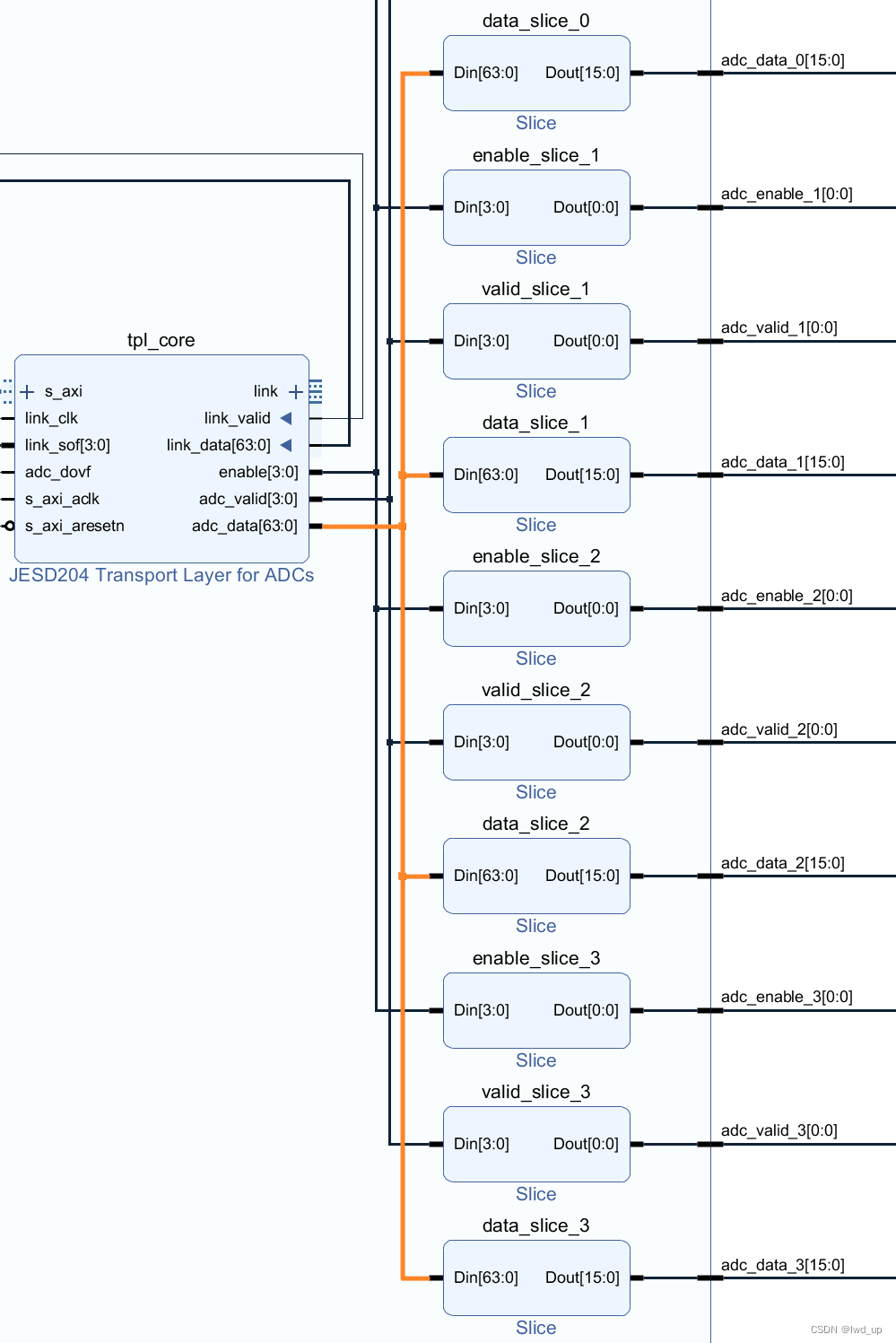

一、JESD204B传输层给应用层数据的格式配置

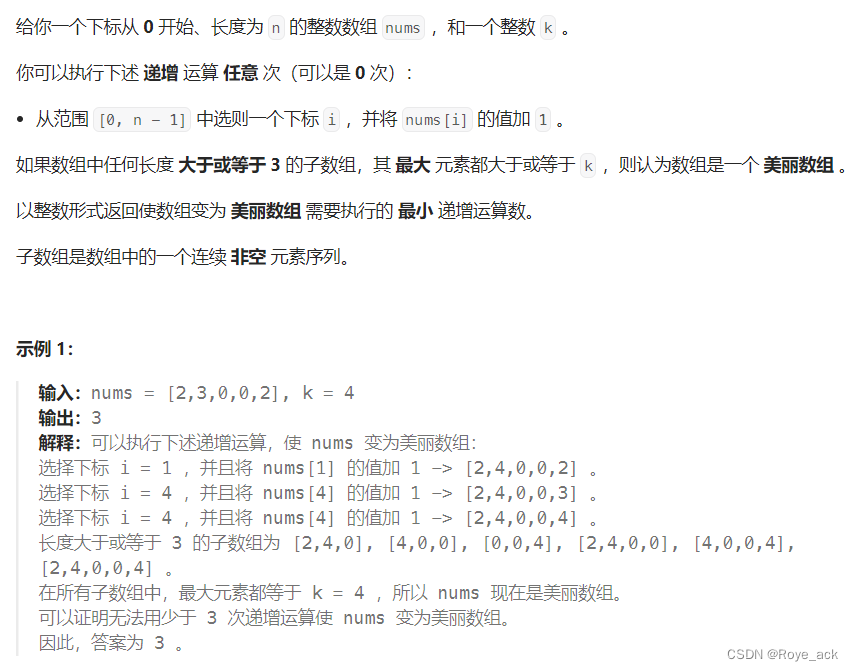

可知 AD9371 官方 demo 2T2R 中对于RX, M=4, L=2, IQ 采样率= LINK rate ,JESD204B 应用层 如何 接收传输层数据 ?

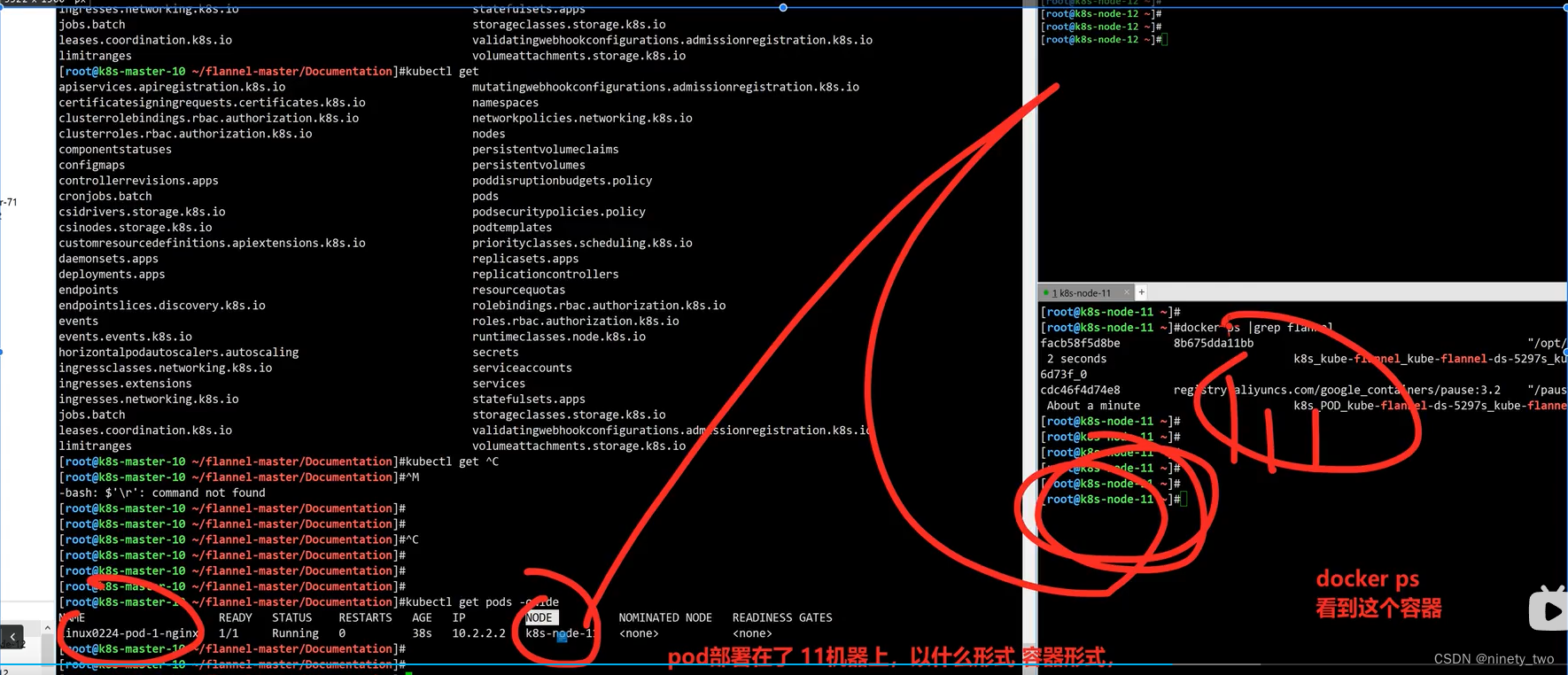

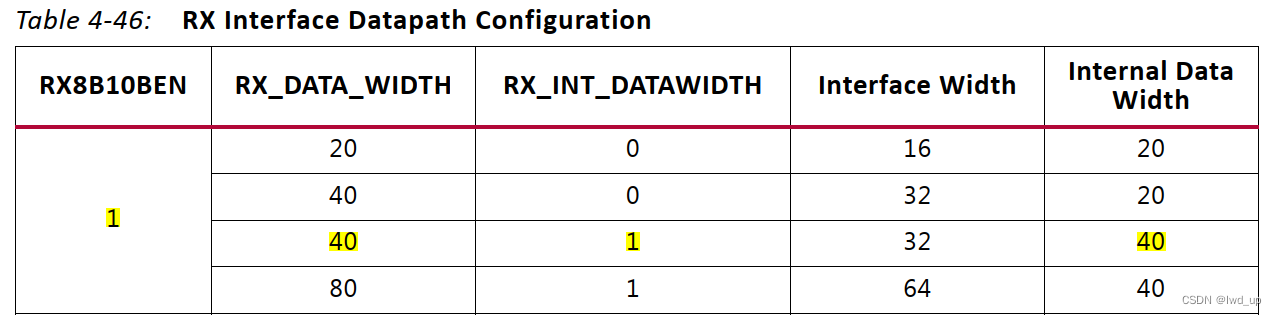

在物理层GTH收发器 配置为32bit模式,链路层每个LINK CLK 需要给物理层每个 LANE 32bit数据,对于RX和RX_OS 都是各自分配2个 lane ,即各自 64bit 数据

每个 LANE需要 32bit数据,下述约束必须满足

L

×

32

=

M

×

N

P

×

S

P

C

L \times 32=M \times N P \times S P C

L×32=M×NP×SPC

S

P

C

=

L

∗

32

/

(

M

∗

N

P

)

\mathrm{SPC}=\mathrm{L}^{*} 32 /(\mathrm{M} * \mathrm{NP})

SPC=L∗32/(M∗NP)2T2R demo 中 JESD RX参数配置为 L=2; M=4; S=1; F=4; NP=16; SPC=1

每个转换器提供 SPC=1个 16Bbit 采样数据, F=4 ,4* 8=32bit ,即每帧每个lane 32bit

1T1R demo 中 JESD RX参数配置为 L=2; M=2; S=1; F=2; NP=16; SPC=2,类似 TX 2T2R

对于RX_OS , JESD 参数配置为 L=2; M=2; S=1; F=2; NP=16; SPC=2,类似 TX 2T2R

每个转换器提供 SPC=2个 16Bbit 采样数据 Frame0 和 Frame1拼在一起 ,每帧 F=2 ,两帧凑成 2 * 2 * 8=32bit

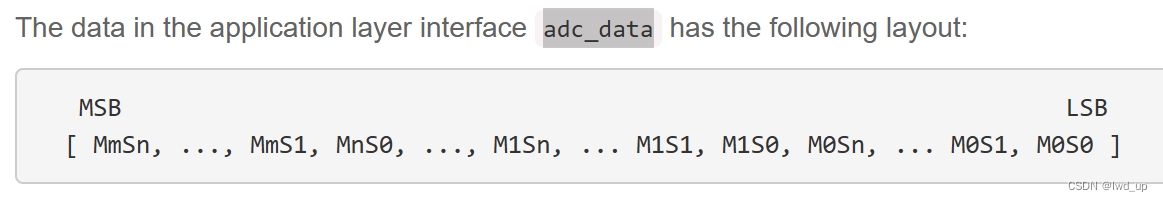

MmSn 表示 第m个转换器的第n个采样数据,

RX 2T2R L=2; M=4; S=1; F=4; NP=16; SPC=1 ;

[ M3S0, M2S0, M1S0, M0S0]

RX 1T1R L=2; M=2; S=1; F=2; NP=16; SPC=2 ;

[ M1S1, M1S0, M0S1, M0S0]

RX_OS L=2; M=2; S=1; F=2; NP=16; SPC=2 ;

[ M1S1, M1S0, M0S1, M0S0]

RX 1T1R 和 RX_OS 和TX 2T2R类似,不过多描述。RX 2T2R 如下图

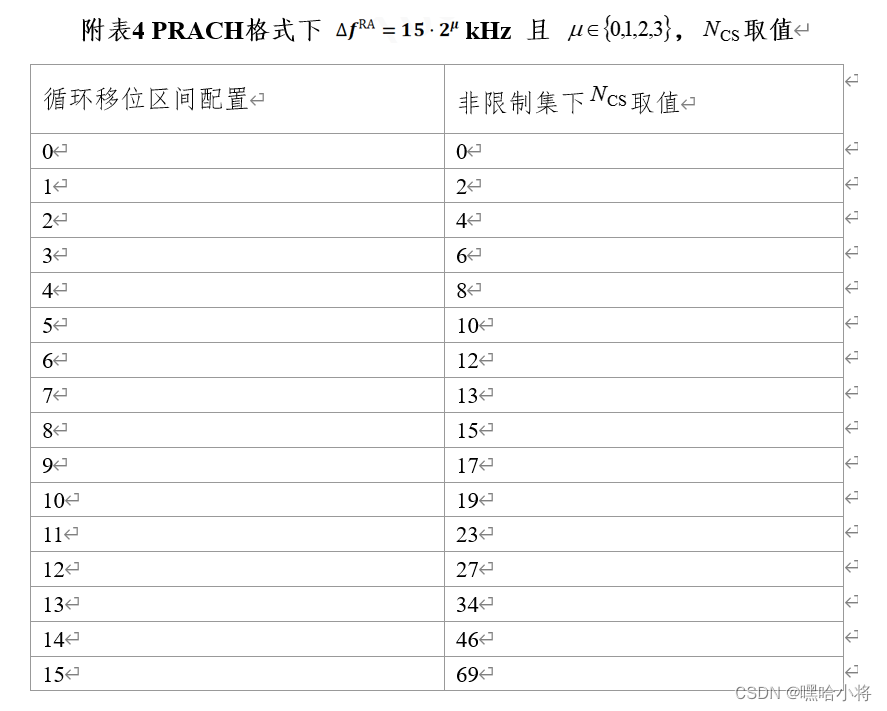

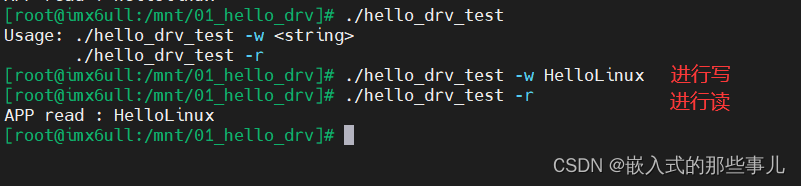

二、JESD204B链路数据配置

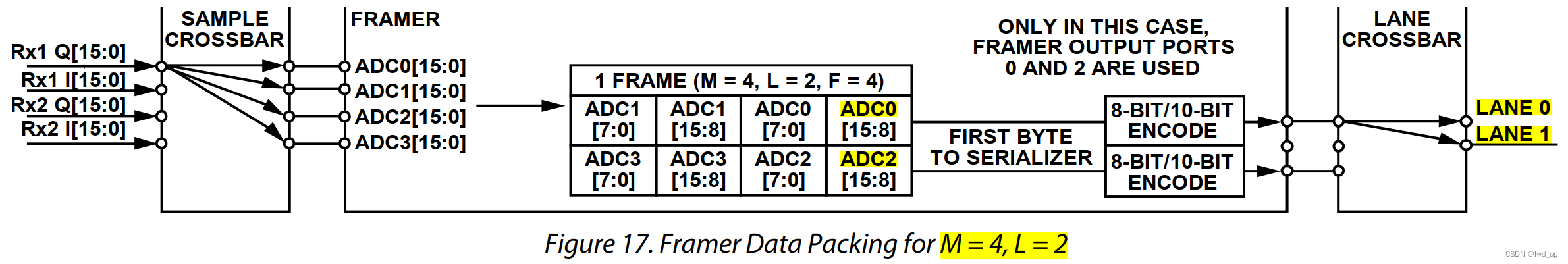

RX 2T2R ,M=4,L=2,F=4,S=1, IQ 采样率= LINK rate= line rate/40 ,SPC=1

AD9371 采样接收数据后, 按下图配置组帧,通过分配的2个lane,送给FPGA解帧

传输层送给应用层的64bit数据adc_data, 排布如下 [ M3S0, M2S0, M1S0, M0S0]

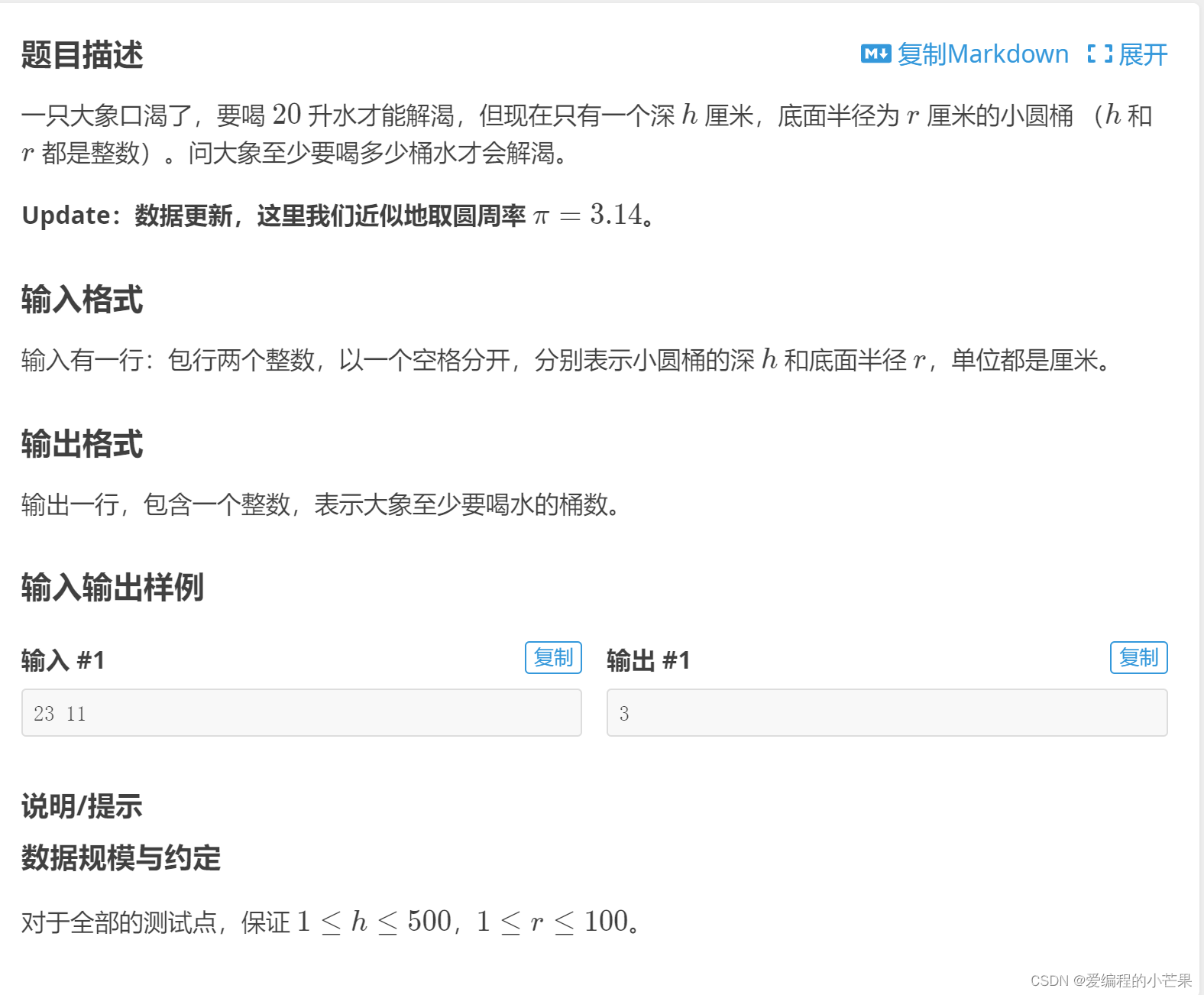

RX 1T1R 和 RX_OS ,M=2,L=2,F=2,S=2, IQ 采样率= 2* LINK rate= line rate/20 ,SPC=2

AD9371 采样接收数据后, 按下图配置组帧,通过分配的2个lane,送给FPGA解帧

注意 :

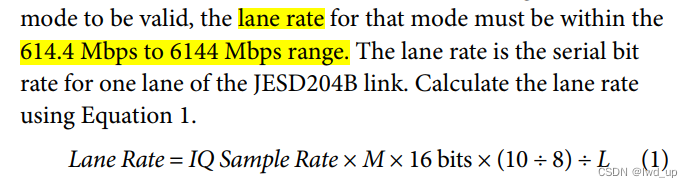

AD9371芯片 的 TX和RX lane rate 有速率限制(UG992),lane rate 都最低614.4MHz

当2T2R 时,M=4, L=2, IQ采样率 最低为15.36MHz,lane rate = 15.36 x 40= 614.4 MHz

当1T1R 时,M=2, L=2, IQ采样率 最低为30.72MHz,lane rate = 30.72x 20= 614.4 MHz

当RX_OS 时,M=2, L=2, IQ采样率 最低为30.72MHz,lane rate = 30.72 x 20= 614.4 MHz

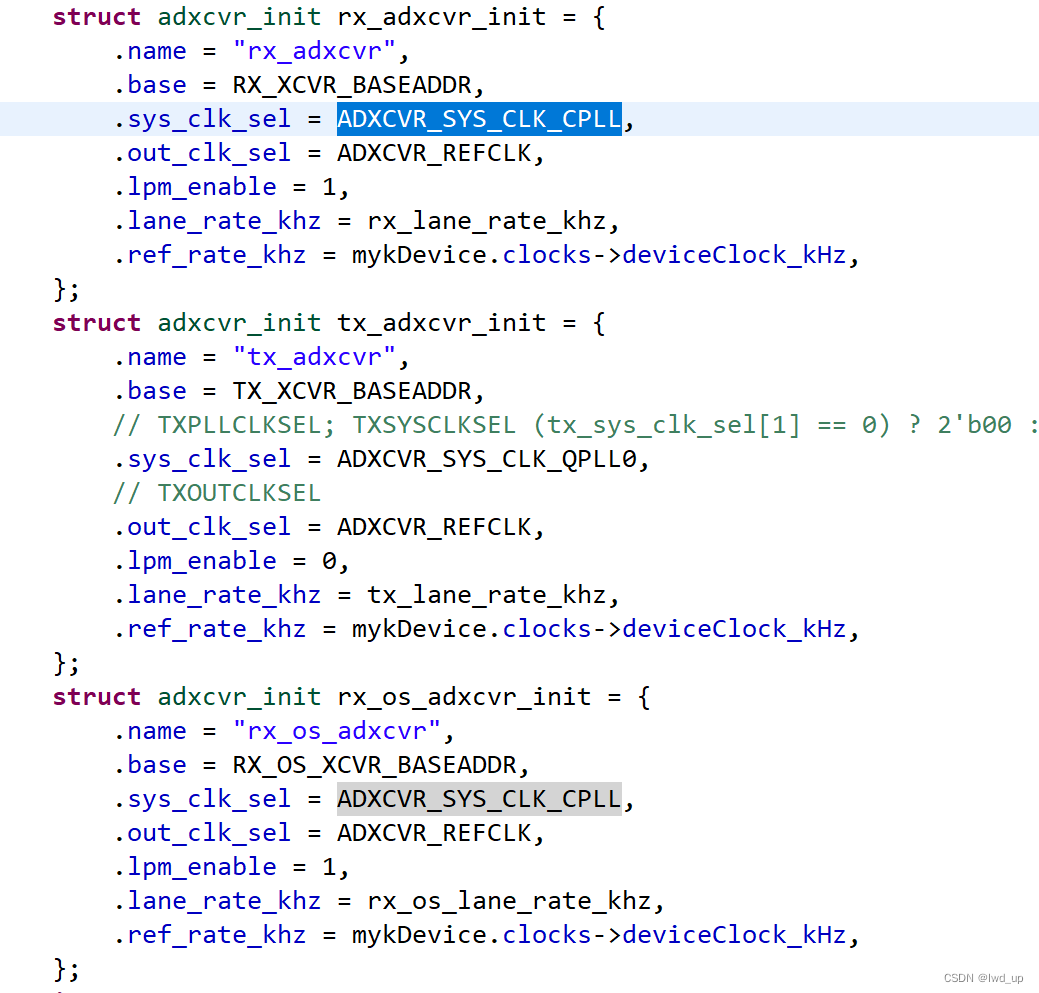

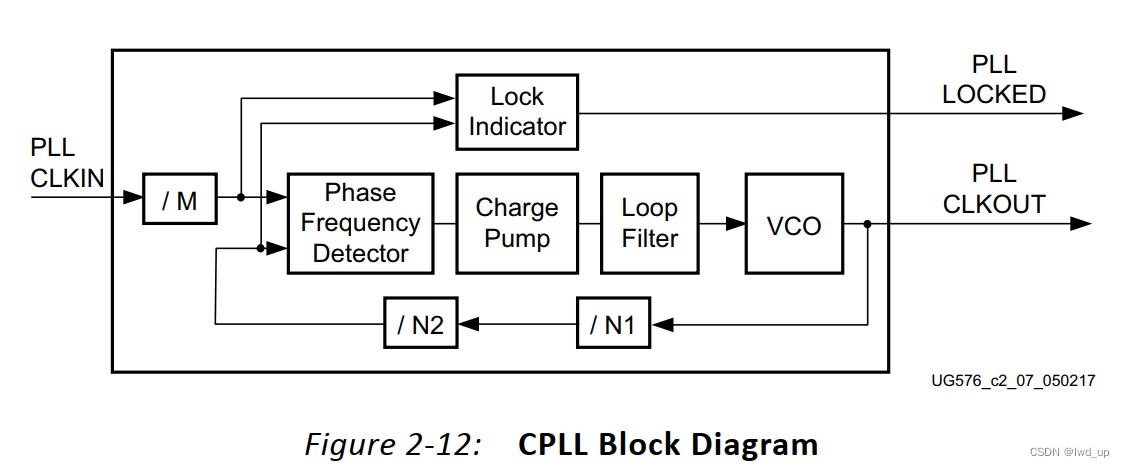

而 由于在FPGA的GTH中, CPLL的 VCO 对工作频率有要求,在当前官方例程中,RX 和 RX_OS都选择的CPLL,其频率为 2 G-6.25G ,求最低采样率?

当 CPLL VCO 锁定频率 2.4576G (尽可能小),CPLL输出过分频器D,D取最大 =8(CPLL不支持16)

line rate (尽可能小)=(2.4576G /8)*2(上升沿和下降沿采样)=614.4MHz

当2T2R 时,M=4, L=2, line rate = (IQ采样率 最低为15.36MHz x 40) =614.4MHz,

当1T1R 时,M=2, L=2, line rate = (IQ采样率 最低为30.72MHz x 20) =614.4MHz,

当RX_OS 时,M=2, L=2, line rate = (IQ采样率 最低为30.72MHz x 20) =614.4MHz

理论上 ,AD9371侧 和 FPGA ,2T2R时,对RX 信号都支持 15.36MHz