μCOS-Ⅲ中断管理,这样理解非常简单!

文章目录

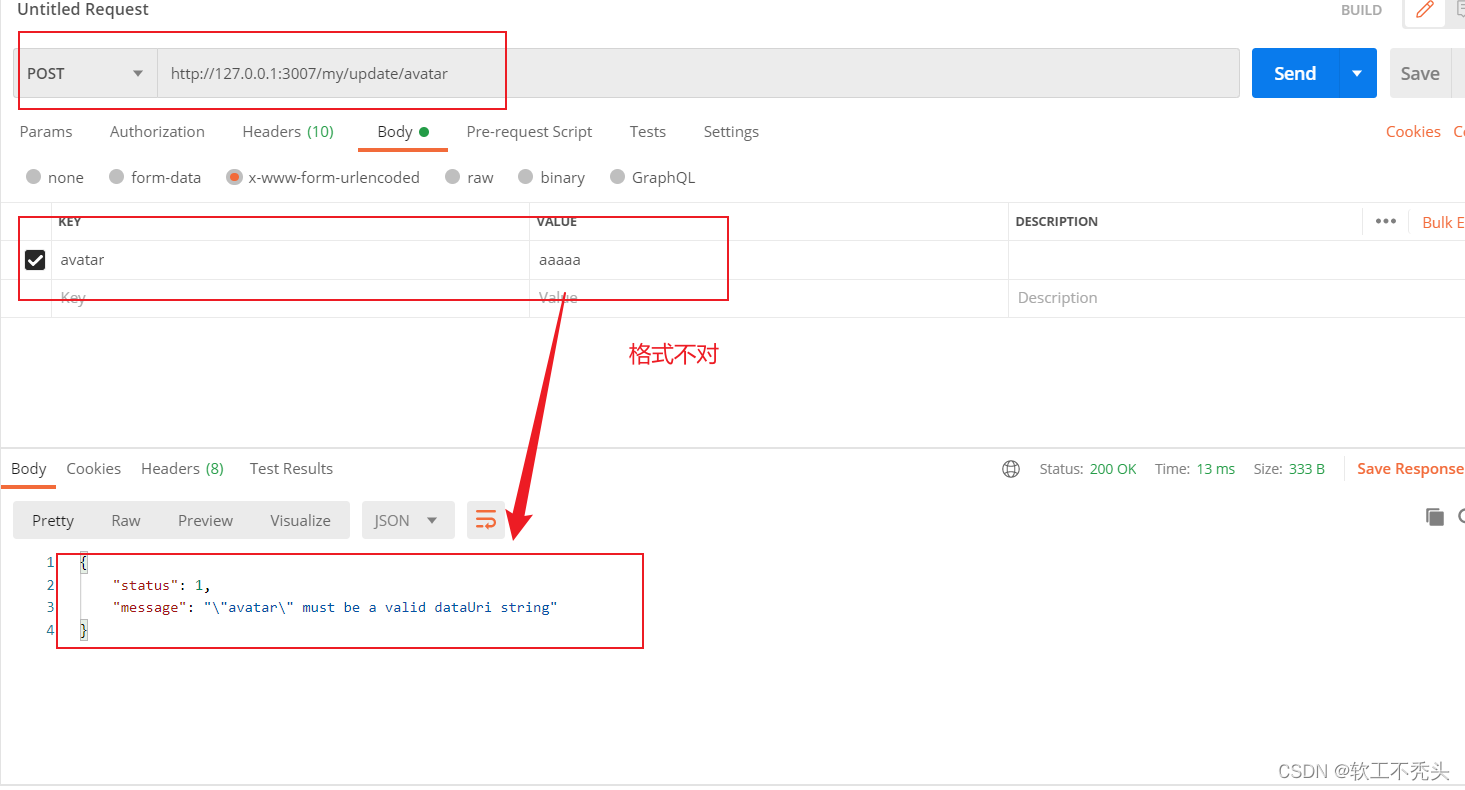

- μCOS-Ⅲ中断管理,这样理解非常简单!

- 前言

- 一、中断源与中断优先级

- 二、μCOS-Ⅲ的中断管理方式

- 三、中断屏蔽与中断控制

- 1、μCOS-Ⅲ中断开关

- 2、μCOS-Ⅲ中断屏蔽应用——临界区

- 4、μCOS-Ⅲ中断屏蔽应用之——任务调度锁

- 四、µC/OS-III 中断嵌套计数器

- 总结

前言

我们已经知道了STM32只使用了中断优先级配置寄存器的[7:4]位来配置中断优先级(共计16个中断优先级等级),并且知道其五个优先级分组的基本含义,(不知道的翻本专栏:μCOS-Ⅲ+GD32_SysTick与PendSV中断管理配置浅解),现在来聊一聊μCOS-Ⅲ的中断管理。

一、中断源与中断优先级

中断管理就必须先知道中断源与中断优先级,但经常有人弄不清楚这两个概念导致弄不清楚中断管理,我们把程序理解为正在写作业的你,中断源就是可以打断你写作业的事情,你妈妈叫你可以打断你写作业,着火也能打断你,隔壁猫叫都可以打断你,你要重新写作业(比作程序复位)或者拿错了作业(比作硬中断)也视为一种中断等…,我们把这些称为中断源。为了防止太乱,你必须做个规划那些事打断你你必须优先做,那些事打断你可以不优先做,所以你制定了一个规则,把事情分为重要事情和必须事情,这就是一个最简单优先级分组。然后你个每个事情做出编号,编号越小事情越优先,比如重新写作业优先级最高编号为,拿错了作业优先级其次,… …猫叫优先级为12,这就是中断优先级。记住:STM32拥有255个中断(编号为 1-15 的对应系统异常,大于等于 16 的则全是外部中断),有16个中断优先级。

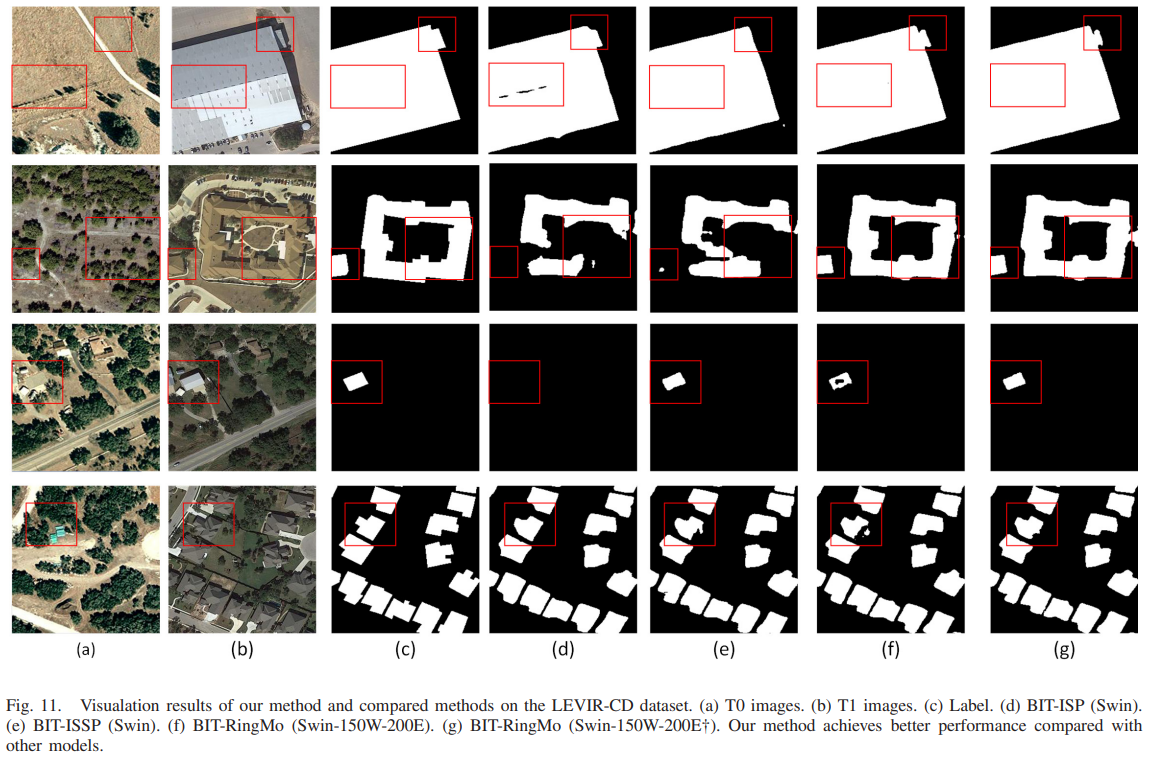

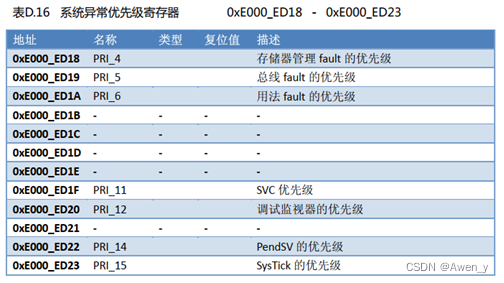

中断优先级有专门的优先级寄存器,前15个中断源(以下称系统异常)有独立的中断优先级配置寄存器,分别是:SHPR1、 SHPR2、 SHPR3

SHPR1寄存器:0xE000ED18

| 比特位 | 名称 | 功能 |

|---|---|---|

| [31:24] | PRI_7 | 保留 |

| [23:16] | PRI_6 | UsageFault 中断优先级 |

| [15:8] | PRI_5 | BusFault 中断优先级 |

| [7:0] | PRI_4 | MemManage 中断优先级 |

SHPR2寄存器:0xE000ED1C

| 比特位 | 名称 | 功能 |

|---|---|---|

| [31:24] | PRI_11 | SVCall 中断优先级 |

| [23:0] | — | 保留 |

SHPR3寄存器:0xE000ED20

| 比特位 | 名称 | 功能 |

|---|---|---|

| [31:24] | PRI_15 | SysTick 中断优先级 |

| [23:16] | PRI_14 | PendSV 中断优先级 |

| [15:0] | PRI_5 | 保留 |

µC/OS-III 在配置 PendSV 和 SysTick 中断优先级的时候,就使用到了 SHPR3 寄存器。

设置PendSV的优先级和SysTick的优先级

剩下的240个外部中断的中断优先级保存在中断优先级寄存器 NVIC_IPRx,用来配置外部中断的优先级,IPR 宽度为 8bit,原则上每个外部中断可配置的优先级为 0~255,数值越小,优先级越高。虽然IP是8位位宽,但CM3芯片精简设计,只有16个优先级,所以也只使用了其[7:4]高4bit 。

typedef struct

{

__IOM uint32_t ISER[8U] /* 中断使能寄存器 */

uint32_tRESERVED0[24U];

__IOM uint32_t ICER[8U]; /* 中断除能寄存器 */

uint32_tRSERVED1[24U];

__IOM uint32_t ISPR[8U]; /* 中断使能挂起寄存器 */

uint32_tRESERVED2[24U];

__IOM uint32_t ICPR[8U]; /* 中断除能挂起寄存器 */

uint32_tRESERVED3[24U];

__IOM uint32_t IABR[8U]; /* 中断有效位寄存器 */

uint32_tRESERVED4[56U];

__IOM uint8_t IP[240U]; /* 中断优先级寄存器 */

uint32_tRESERVED5[644U];

__OM uint32_t STIR; /* 软件触发中断寄存器 */

} NVIC_Type;

具体的设置方法会更具你的优先级分组来分,看是所有事情都重要或者所有事情都必须,或者一部分重要一部分必须。这就是为什么每个程序中只能存在一种优先级分组标准,否则会乱。

二、μCOS-Ⅲ的中断管理方式

你为了写作业快,你找了个AI机器人辅导你写作业,类似于加上μCOS-Ⅲ操作系统,这个系统就非常厉害,它不仅可以根据作业多少进行合理安排时间,高效辅导你写多门课程的作业,并且可以帮你准确判断是否有事情打断你写作业,当房子着火他会提醒你,妈妈叫你也会中断下来提醒你,猫叫也会提醒你,但是有几样它做不到:

1.你要重新写,它不会阻止你,它只会配合你重写(程序复位)

2.你拿错了作业,它判断不了你拿错了,只有你发现作业拿错了不能继续写了,它才会停下来。(硬件中断)

3.有特殊要求的中断,表示这些事不归他管。

如此类比,所以在μCOS-Ⅲ中断配置项中需要注意以下几点:

- 建议将所有优先级位指定为抢占优先级位,方便μC/OS-III管理HAL_NVIC_SetPriorityGrouping(NVIC_PRIORITYGROUP_4),为了保持事情分组正确好管理

- CPU_CFG_NVIC_PRIO_BITS,这个宏用于定义中断优先级配置寄存器的实际使用位数,对于STM32如果将宏定义为4,因为 STM32 的优16先级配置寄存器都只使用到了高四比特位;意思就是你准备定义16个优先级,

- 另外一个是宏CPU_CFG_KA_IPL_BOUNDARY用于定义受 µC/OS-III 管理的最高中断优先等级,中断优先级低于此宏定义值的中断受 µC/OS-III 管理。一般定义为4即中断优先级范围为4~15,意思就是AI机器人可以最高管理的优先级事情,比如重写作业或作业拿错了等特殊中断优先级太高不归他管,这个得你自己主观判断。

在中断服务函数中,如果调用μC/OS-III的API函数,那么该优先级必须在μC/OS-III所管理的范围内,这也就是SysTick的优先级为什么最高只能到4。

三、中断屏蔽与中断控制

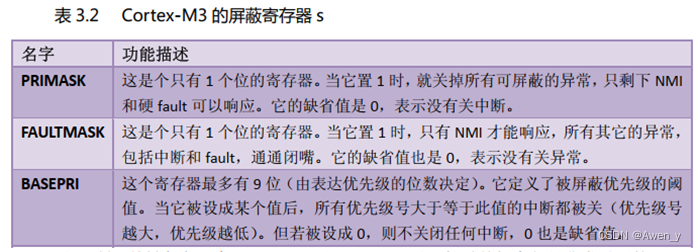

在某些时候需要将一些中断进行屏蔽,就要使用到中断屏蔽寄存器。

PRIMASK 寄存器:作用: PRIMASK 寄存器有 32bit,但只有 bit0 有效,是可读可写的,将 PRIMASK 寄存器设置为 1 用于屏蔽除 NMI 和 HardFault 外的所有异常和中断,将 PRIMASK 寄存器清 0 用于使能中断。

用法1

CPSIE I /* 清除 PRIMASK(使能中断) */

CPSID I /* 设置 PRIMASK(屏蔽中断) */

用法2

MRS R0, PRIMASK /* 读取 PRIMASK 值 */

MOV R0, #0

MSR PRIMASK, R0 /* 清除 PRIMASK(使能中断) */

MOV R0, #1

MSR PRIMASK, R0 /* 设置 PRIMASK(屏蔽中断) */

用法3

__get_PRIMASK(); /* 读取 PRIMASK 值 */

__set_PRIMASK(0U); /* 清除 PRIMASK(使能中断) */

__set_PRIMASK(1U); /* 设置 PRIMASK(屏蔽中断) */

FAULTMASK 寄存器:作用: FAULTMASK 寄存器有 32bit,但只有 bit0 有效,也是可读可写的,将 FAULTMASK寄存器设置为 1 用于屏蔽除 NMI 外的所有异常和中断,将 FAULTMASK 寄存器清零用于使能中断。

用法1

CPSIE F /* 清除 FAULTMASK(使能中断) */

CPSID F /* 设置 FAULTMASK(屏蔽中断) */

用法2

MRS R0, FAULTMASK /* 读取 FAULTMASK 值 */

MOV R0, #0

MSR FAULTMASK, R0 /* 清除 FAULTMASK(使能中断) */

MOV R0, #1

MSR FAULTMASK, R0 /* 设置 FAULTMASK(屏蔽中断) */

用法3

__get_FAULTMASK(); /* 读取 FAULTMASK 值 */

__set_FAULTMASK(0U); /* 清除 FAULTMASK(使能中断) */

__set_FAULTMASK(1U); /* 设置 FAULTMASK(屏蔽中断) */

BASEPRI 寄存器:作用: BASEPRI 有 32bit,但只有低 8 位[7:0]有效,也是可读可写的。 BASEPRI 寄存器比起 PRIMASK 和 FAULTMASK 寄存器直接屏蔽掉大部分中断的方式, BASEPRI 寄存器的功能显得更加细腻, BASEPRI 用于设置一个中断屏蔽的阈值,设置好 BASEPRI 后,中断优先级低于 BASEPRI 的中断就都会被屏蔽掉, µC/OS-III 就是使用 BASEPRI 寄存器来管理受 µC/OS-III管理的中断的,而不受 µC/OS-III 管理的中断,则不受 µC/OS-III 的影响。

用法1

MRS R0, BASEPRI /* 读取 BASEPRI 值 */

MOV R0, #0

MSR BASEPRI, R0 /* 清除 BASEMASK(使能中断) */

MOV R0, #0x60 /* 举例 */

MSR BASEPRI, R0 /* 设置 BASEMASK(屏蔽优先级低于 0x60 的中断) */

用法2

__get_BASEPRI(); /* 读取 BASEPRI 值 */

__set_BASEPRI(0); /* 清除 BASEPRI(使能中断) */

__set_BASEPRI(0x60); /* 设置 BASEPRI(屏蔽优先级小于 0x60 的中断) */

μC/OS-III主要用到BASEPRI和·PRIMASK,

中断管理主要利用BASEPRI这个寄存器,当需要关闭大部分中断则使用PRIMSASK这个寄存器

BASEPRI:屏蔽优先级低于某个阀值的中断,为0时则不关闭任何中断

比如:BASEPRI值为0x40(高四位有效)表示中断优先级在4~15内的均屏蔽,0-3的中断优先级正常执行,要关闭大部分中断则使用PRIMASK寄存器

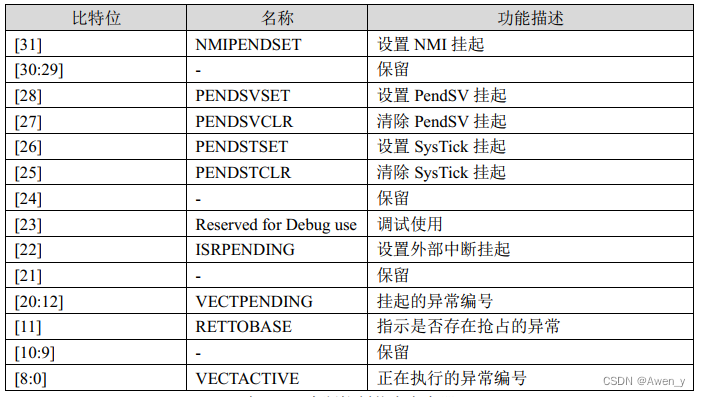

ICSR中断控制状态寄存器:0xE000ED04,作用:用于设置和清除异常的挂起状态,以及获取当前系统正在执行的异常编号,VECTACTIVE 段[8:0],读VECTACTIVE 段就能够判断当前执行的代码是否在中断中:

1、μCOS-Ⅲ中断开关

在文件 cpu_a.asm 中提供了两组同于开关中断的标号

1.OCPU_IntDis

OCPU_IntDis

CPSID I ; 关闭中断

BX LR ; 返回

2.CPU_IntEn

CPU_IntEn

CPSIE I ; 打开中断

BX LR ; 返回

以上是第一组:关于 CPU_IntDis和CPU_IntEn这两个关于中断的操作标号都是直接操作了 PRIMASK 寄存器,直接屏蔽所有的中断和打开所用中断。

3.CPU_SR_Save

CPU_SR_Save

CPSID I ; 关闭中断

PUSH {R1} ; 入栈 R1

MRS R1, BASEPRI ; R1 = BASEPRI

MSR BASEPRI, R0 ; BASEPRI = R0

DSB ; 数据同步

ISB ; 指令同步

MOV R0, R1 ; R0 = R1

POP {R1} ; 出栈 R1

CPSIE I ; 打开中断

BX LR ; 返回

4.CPU_SR_Restore

CPU_SR_Restore

CPSID I ; 关闭中断

MSR BASEPRI, R0 ; BASEPRI = R0

DSB ; 数据同步

ISB ; 指令同步

CPSIE I ; 打开中断

BX LR ; 返回

以上是第二组:

标号 CPU_SR_Save 的内容可简单分为如下三个步骤:

- 将 BASEPRI 寄存器的值读入到 R1 寄存器中,保存 BASEPRI 寄存器的原始值。

- 将 R0 寄存器的值写入 BASEPRI 寄存器, R0 寄存器中保存的值就是程序在调用标号CPU_SR_Save 时,传入的参数。

- 将 R1 寄存器中的值赋给 R0 寄存器,在程序中调用标号 CPU_SR_Save 时, CPU_SR_Save的返回值就保存在 R0 寄存器中。因此标号 CPU_SR_Save 所作的事情就是,根据入参设置 BASEPRI 寄存器,并返回在设置BASEPRI 寄存器前 BASEPRI 寄存器的值,以获取中断状态并关闭受 µC/OS-III 管理的中断。

而标号 CPU_SR_Restore的 就是用来给 BASEPRI 寄存器赋指定值的。 配个标号 CPU_SR_Save 使用就能够在需要进行中断保护(比如临界区) 的代码前后屏蔽并恢复受 µC/OS-III 管理的中断,以达到关键代码不受中断影响的目的。

μCOS-Ⅲ的中断屏蔽操作在以下两个地方使用比较多:

2、μCOS-Ⅲ中断屏蔽应用——临界区

什么是临界段:临界区,指必须完整运行,不能被中断或任务切换打断的代码中的一些关键部分。

使用场合:

1.需要严格按照时序初始化的外设:IIC、SPI等

2.系统自身需求

3.用户自己的代码需要不被打断、

API介绍

原理:在进入临界段代码时关闭中断,当处理完临界段代码以后再打开中断

1.CPU_CRITICAL_ENTER(); 进入临界段

#define CPU_CRITICAL_ENTER() \

do \

{ \

CPU_INT_DIS(); \

} while (0)

#define CPU_INT_DIS() \

do \

{ \

cpu_sr = CPU_SR_Save( CPU_CFG_KA_IPL_BOUNDARY << (8u - CPU_CFG_NVIC_PRIO_BITS)); \

} while (0)

CPU_CFG_KA_IPL_BOUNDARY << (8u – CPU_CFG_NVIC_PRIO_BITS),这个的结果就是屏蔽受 µC/OS-III 管理的中断优先级的中断,而不受 µC/OS-III 管理的中断,是不受影响的。

2.CPU_CRITICAL_EXIT(); 退出临界段

#define CPU_CRITICAL_EXIT() \

do \

{ \

CPU_INT_EN(); \

} while (0)

#define CPU_INT_EN() \

do \

{ \

CPU_SR_Restore(cpu_sr); \

} while (0)

将 BASEPRI 恢复到进入临界区之 前 的 状 态 ,函 数 CPU_CRITICAL_ENTER() 和 函 数CPU_CRITICAL_EXIT()配合使用的

代码演示:

{

uint32_t a;

uint32_t b;

CPU_SR_ALLOC(); /* 必须定义在所有局部变量之后 */

/* 非临界区代码 */

CPU_CRITICAL_ENTER(); /* 进入临界区 */

/* 临界区代码 */

CPU_CRITICAL_EXIT(); /* 退出临界区 */

/* 非临界区代码 */

}

特点:

1.成对使用,但不可以嵌套使用(注意和挂起任务、恢复任务特点进行对比)

2.尽量保持临界区耗时段较小

4、μCOS-Ⅲ中断屏蔽应用之——任务调度锁

什么是任务调度锁:用于任务调度器上锁和解锁,当任务调度器上锁则禁止任务调度,解锁则允许任务调度,其内部也是调用的的CPU_CRITICAL_ENTER();和 CPU_CRITICAL_EXIT();两个函数

使用OSSchedLock()进行上锁

使用OSSchedUnlock()进行解锁

特点:

1.成对使用,可嵌套,上锁次数和解锁次数必须一样(和挂起任务、恢复任务特点一致),进入和退出时都会有更新上锁层数

2.仅关闭调度器,不影响中断执行,只是不会执行任务切换,仅仅防止任务之间的资源争夺,中断照样执行

3.适用于临界区于任务与任务之间;既不用去延时中断,又做到临界区的安全

OS_ERR err;

/*非临界区*/

OSSchedLock(&err) //上锁

{

}

OSSchedUnlock(&err); //解锁

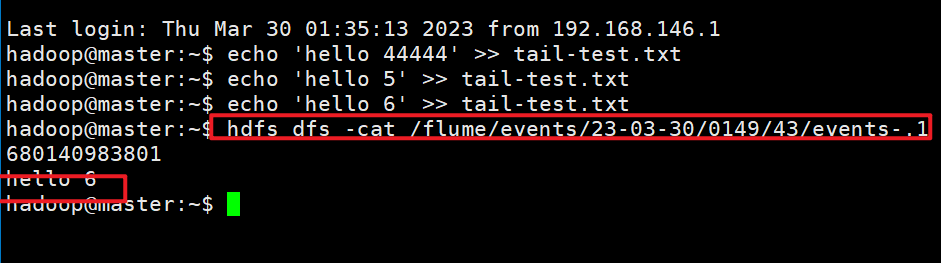

四、µC/OS-III 中断嵌套计数器

在 µC/OS-III 中,会通过全局变量 OSIntNestingCtr 记录中断嵌套的次数,方便 µC/OS-III 判断当前是否处于中断状态。当全局变量 OSIntNestingCtr 大于 0 的时候,就表示当前处于中断状态,当全局变量 OSIntNestingCtr 等于 0 的时候,就表示当前不是处于中断状态。

全局变量 OSIntNestingCtr 是在中断服务函数中更新的, 因此, µC/OS-III 提供了两个分别用于中断服务函数前后的函数,分别为 OSIntEnter()和函数 OSIntExit()。其中函数 OSIntEnter()只是简单地更新了全局变量 OSIntNestingCtr 的值, 而函数 OSIntExit()除了更新全局变量OSIntNestingCtr 的值,同时还会根据需要进行任务切换。下面以 µC/OS-III 提供了 SysTick 的中断服务函数为例,展示函数OSIntEnter()和函数OSIntExit()的使用:

void OS_CPU_SysTickHandler(void)

{

CPU_SR_ALLOC();

CPU_CRITICAL_ENTER();

/* 进入中断后,先调用函数 OSIntEnter() */

OSIntEnter();

CPU_CRITICAL_EXIT();

/* 中断服务函数的内容 */

OSTimeTick();

/* 中断返回前,调用函数 OSIntExit() */

OSIntExit();

}

总结

关于µC/OS-III 的中断管理就到这里,,整个OS的中断还是立足于M3内核之上的,如果对内核中断比较熟悉,那么理解OS中断管理就几乎是水到渠成的事。其中对SysTick与PendSV中断管理的部分是单独拿出来的,因为这两个中断可以说是作为µC/OS-III 最基础最核心内容之一,说它们是µC/OS-III 的命门所在也不为过。

有兴趣的可以参考:https://blog.csdn.net/Yin_w/article/details/132184044?spm=1001.2014.3001.5502本篇博客。

![[ACTF2020 新生赛]Exec](https://img-blog.csdnimg.cn/a09460c15b174237a791667e68e5a344.png)

![【蓝桥每日一题]-贪心(保姆级教程 篇1)#拼数 #合并果子 #凌乱yyy](https://img-blog.csdnimg.cn/54cd4018185545aead8ac23d50dcce77.png)