目录

- 1、前言

- 免责声明

- 2、我这里已有的 GT 高速接口解决方案

- 3、设计思路框架

- 设计框图

- OV5640摄像头配置及采集

- 视频数据封装

- 按键选择

- HSSTLP高速收发器详解

- HSSTLP基本了解

- HSSTLP之时钟

- HSSTLP之PCS

- HSSTLP之PMA

- HSSTLP之接口说明

- 硬件设计

- HSSTLP IP调用和配置

- SFP连接方案选择

- 视频数据对齐

- 视频数据解码

- 图像缓存架构详解

- 架构讲解

- 视频缓存请求

- AXI总线

- HMIC_H

- 图像缓存读写逻辑

- 输出视频时序

- sil9134配置

- 4、PDS工程详解

- 5、上板调试验证并演示

- 准备工作

- 静态演示

- 6、福利:工程源码获取

紫光同创FPGA实现HSSTLP高速接口视频传输,8b/10b编解码,OV5640采集,提供PDS工程源码和技术支持

1、前言

2019年初我刚出道时,还是Xilinx遥遥领先的时代(现在貌似也是),那时的国产FPGA还处于黑铁段位,国产FPGA仰望Xilinx情不自禁道:你以为躲在这里就找不到你吗?没用的,你那样拉轰的男人,无论在哪里,都像黑夜里的发光虫那样的鲜明、那样的出众,你那忧郁的眼神,稀嘘的胡渣子,神乎其技的刀法,还有那杯Dry martine,都深深的迷住了我。。。然而才短短4年,如今的国产FPGA属于百家争鸣、百花齐放、八仙过海、神仙打架、方兴未艾、得陇望蜀、友商都是XX的喜极而泣之局面,面对此情此景,不得不吟唱老人家的诗句:魏武挥鞭,东临碣石有遗篇,萧瑟秋风今又是,换了人间。。。

言归正传,目前对于国产FPGA的共识有以下几点:

1:性价比高,与同级别国外大厂芯片相比,价格相差几倍甚至十几倍;

2:自主可控,国产FPGA拥有完整自主知识产权的产业链,从芯片到相关EDA工具

3:响应迅速,FAE技术支持比较到位,及时解决开发过程中遇到的问题,毕竟中文数据手册。。

4:采购方便,产业链自主可控,采购便捷

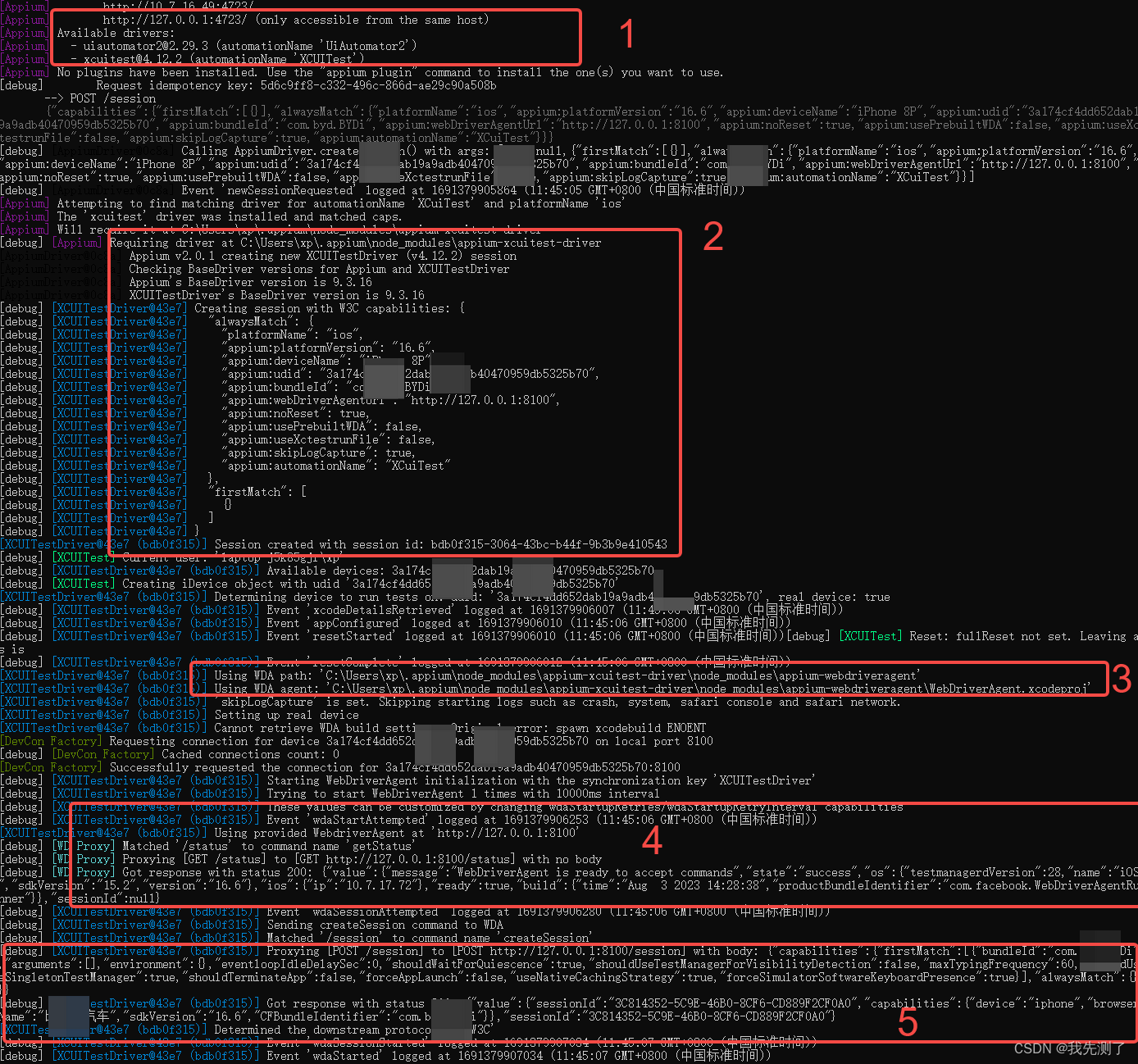

没玩过高速接口都不好意思说自己玩儿过FPGA,这是CSDN某大佬说过的一句话,鄙人深信不疑。。。本文使用紫光同创的PG2L100H-6FBG676 FPGA实现HSSTLP高速接口视频传输,输入视频采用双目的OV5640摄像头模组,同时有两路视频进入FPGA,通过板载的按键选择其中一路作为HSSTLP发送接口的视频输入;FPGA采集到OV5640视频后,进行视频数据封装,对视频加上帧头等控制信息,然后送入HSSTLP进行8b/10b编码、PCS、PMA等操作,最后输出高速串行的差分信号,然后通过板载的SFP光口发送出去;然后板载的SFP光口再接收数据,送入HSSTLP进行PMA、PCS、8b/10b解码,最后输出并行的数据,再给到数据对齐模块,利用K码的特性将数据对齐;再将数据给到解码模块,检测并去掉帧头等控制信息,相当于之前视频数据封装的逆过程,然后给到然后视频数据给到图像缓存架构,将视频数据缓存到DDR3中缓存后输出送入输出显示时序模块,然后将输出视频送入sil9134芯片进行HDMI编码输出,最后连接显示器,即可显示输出图像;提供紫光同创FPGA的HSSTLP IP核文件,将HSSTLP IP配置为8b/10b编解码协议,单线线速率配置为5G,你也可以配置为更高速率进行测试,然后生成默认的Example工程,并对Example工程总修改和用户接口的封装;提供两种SFP连接方案,一种是使用一个SFP光口做数据连接,即同一个SFP的TX连接RX,另一种是使用两个SFP光口做数据连接,即SFP1的TX连接SFP2的RX,在PDS工程代码中,通过define宏定义来选择其中一种方案;上电默认选择第一种方案;

本设计提供1套Pango Design Suite 2021.4版本的工程源码;提供HSSTLP IP核文件;

本博客详细描述了紫光同创FPGA实现HSSTLP高速接口视频传输的设计方案,工程代码可综合编译上板调试,可直接项目移植,适用于在校学生、研究生项目开发,也适用于在职工程师做学习提升,可应用于医疗、军工等行业的高速接口或图像处理领域;

提供完整的、跑通的工程源码和技术支持;

工程源码和技术支持的获取方式放在了文章末尾,请耐心看到最后;

免责声明

本工程及其源码即有自己写的一部分,也有网络公开渠道获取的一部分(包括CSDN、Xilinx官网、Altera官网等等),若大佬们觉得有所冒犯,请私信批评教育;基于此,本工程及其源码仅限于读者或粉丝个人学习和研究,禁止用于商业用途,若由于读者或粉丝自身原因用于商业用途所导致的法律问题,与本博客及博主无关,请谨慎使用。。。

2、我这里已有的 GT 高速接口解决方案

我的主页有FPGA GT 高速接口专栏,该专栏有 GTP 、 GTX 、 GTH 、 GTY 等GT 资源的视频传输例程和PCIE传输例程,其中 GTP基于A7系列FPGA开发板搭建,GTX基于K7或者ZYNQ系列FPGA开发板搭建,GTH基于KU或者V7系列FPGA开发板搭建,GTY基于KU+系列FPGA开发板搭建;以下是专栏地址:

点击直接前往

3、设计思路框架

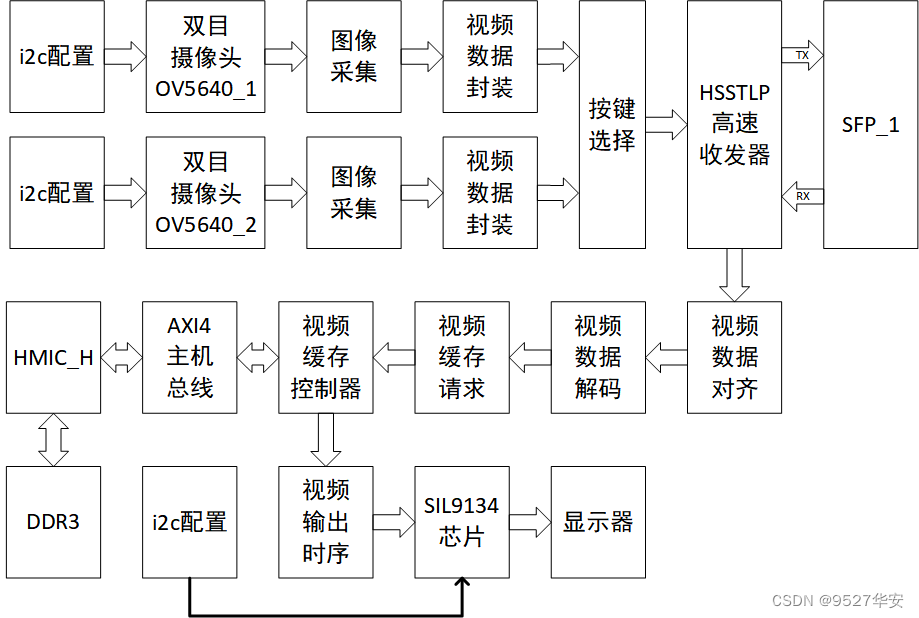

设计框图

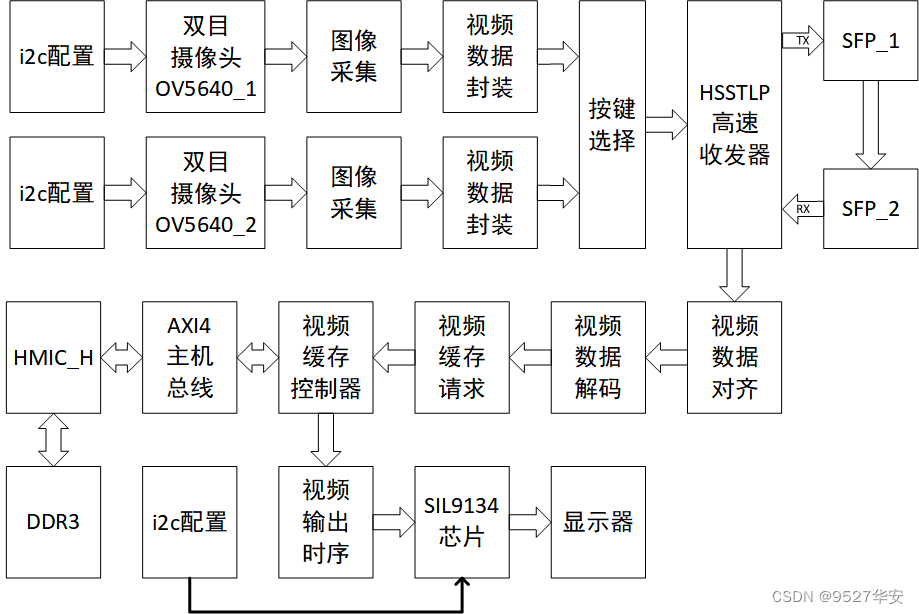

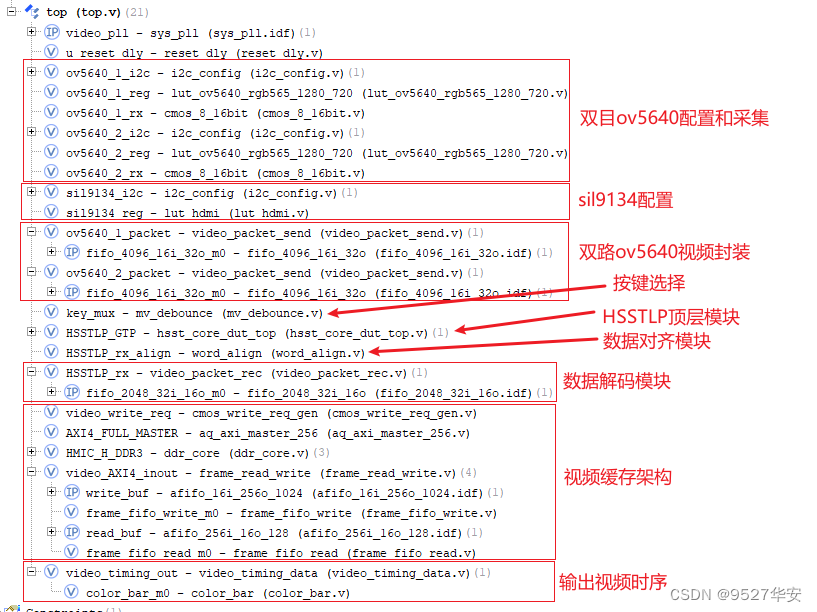

本文使用紫光同创的PG2L100H-6FBG676 FPGA实现HSSTLP高速接口视频传输,输入视频采用双目的OV5640摄像头模组,同时有两路视频进入FPGA,通过板载的按键选择其中一路作为HSSTLP发送接口的视频输入;FPGA采集到OV5640视频后,进行视频数据封装,对视频加上帧头等控制信息,然后送入HSSTLP进行8b/10b编码、PCS、PMA等操作,最后输出高速串行的差分信号,然后通过板载的SFP光口发送出去;然后板载的SFP光口再接收数据,送入HSSTLP进行PMA、PCS、8b/10b解码,最后输出并行的数据,再给到数据对齐模块,利用K码的特性将数据对齐;再将数据给到解码模块,检测并去掉帧头等控制信息,相当于之前视频数据封装的逆过程,然后给到然后视频数据给到图像缓存架构,将视频数据缓存到DDR3中缓存后输出送入输出显示时序模块,然后将输出视频送入sil9134芯片进行HDMI编码输出,最后连接显示器,即可显示输出图像;提供紫光同创FPGA的HSSTLP IP核文件,将HSSTLP IP配置为8b/10b编解码协议,单线线速率配置为5G,你也可以配置为更高速率进行测试,然后生成默认的Example工程,并对Example工程总修改和用户接口的封装;提供两种SFP连接方案,一种是使用一个SFP光口做数据连接,即同一个SFP的TX连接RX,另一种是使用两个SFP光口做数据连接,即SFP1的TX连接SFP2的RX,在PDS工程代码中,通过define宏定义来选择其中一种方案;上电默认选择第一种方案;两种方案的工程设计框图如下:

提供两种SFP连接方案,一种是使用一个SFP光口做数据连接,即同一个SFP的TX连接RX;上电默认采用此种方案,SFP连接方案1如下:

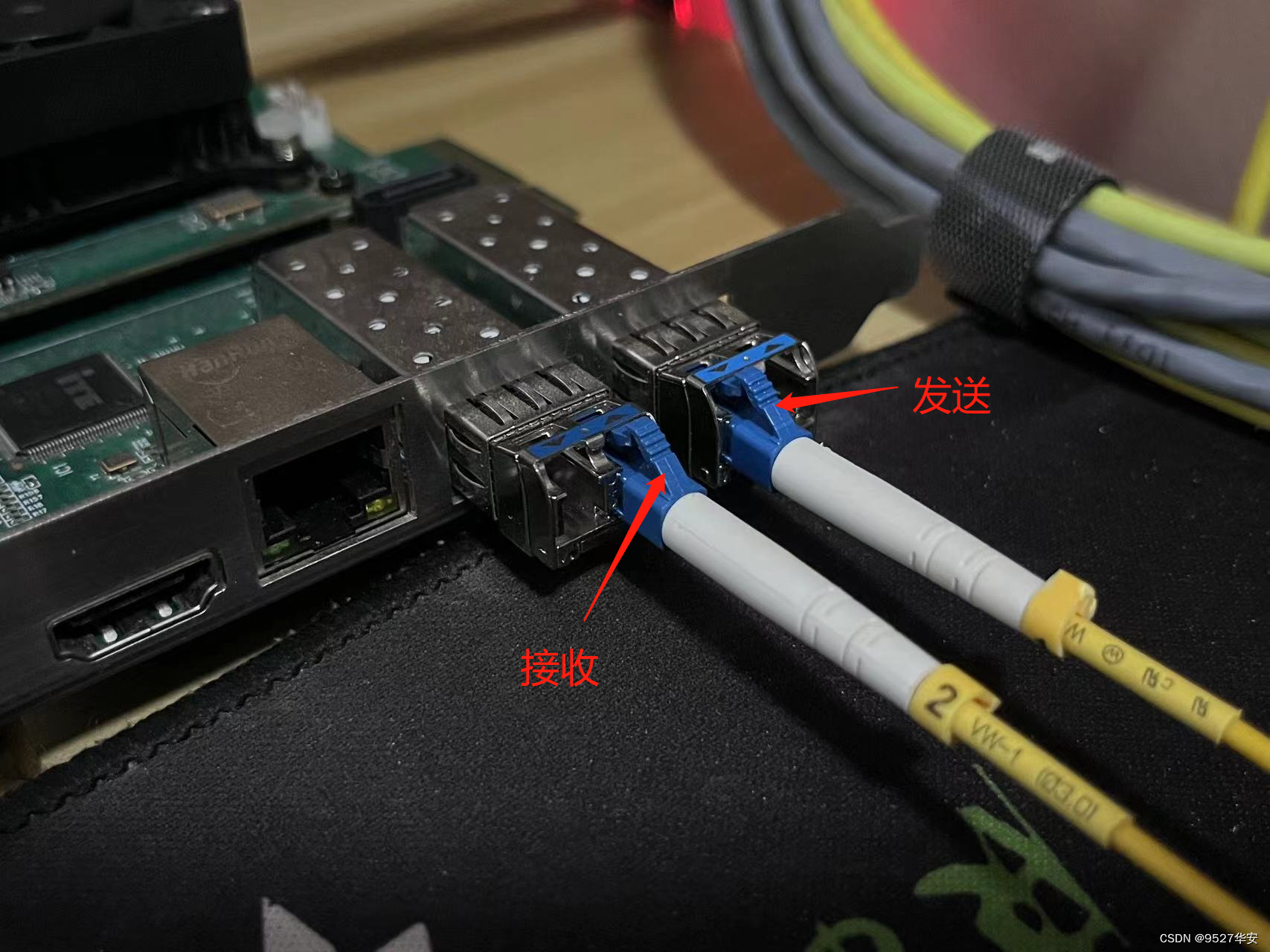

另一种是使用两个SFP光口做数据连接,即SFP1的TX连接SFP2的RX,在PDS工程代码中,通过define宏定义来选择其中一种方案;SFP连接方案2如下:

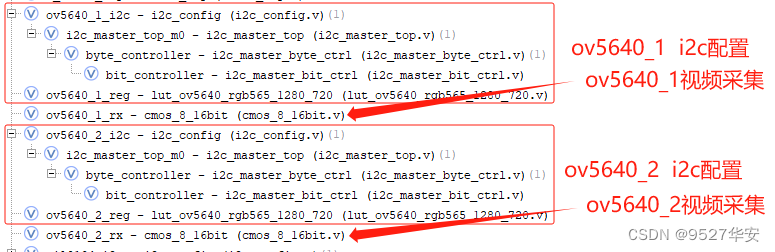

OV5640摄像头配置及采集

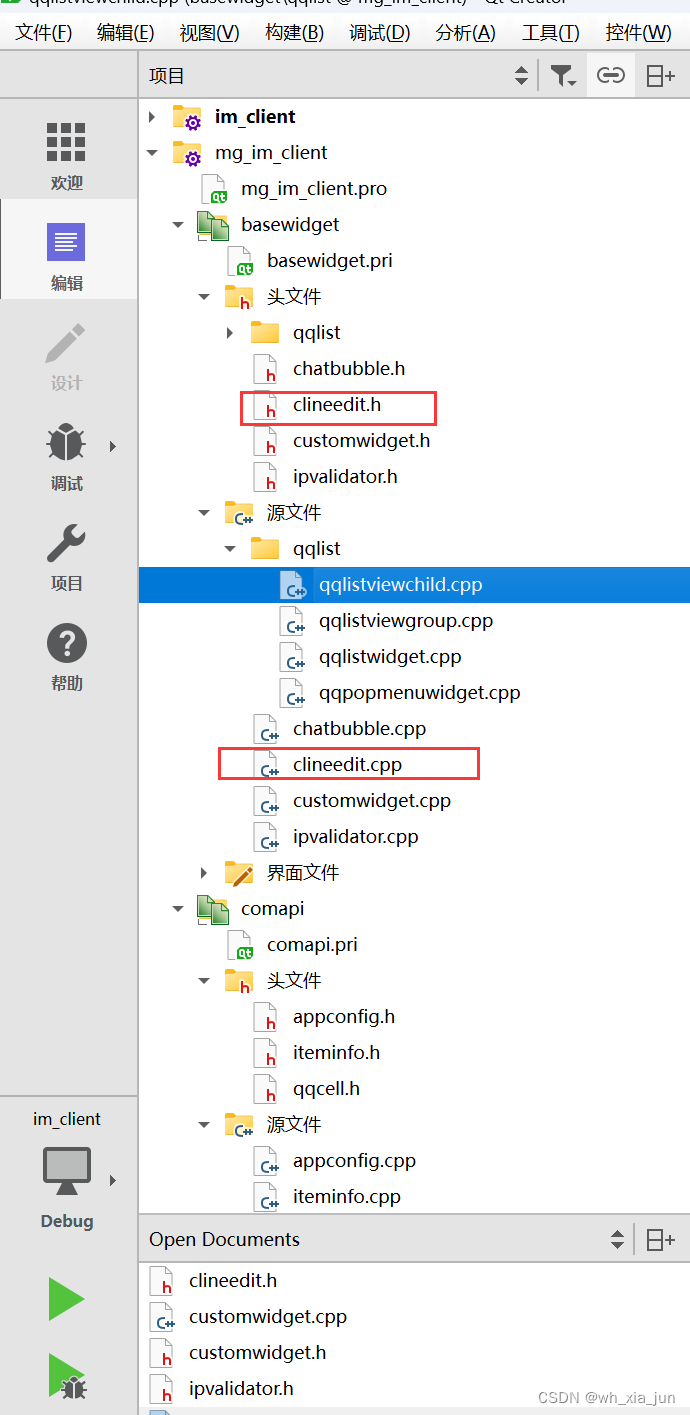

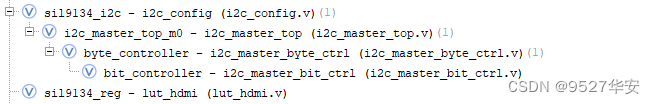

本设计的输入为双目OV5640摄像头,需要i2c配置才能使用,需要将DVP接口的视频数据采集为RGB565格式的视频数据,这两部分均用verilog代码模块实现,代码位置如下:

OV5640摄像头配置为分辨率1280x720,RGB565数据格式;

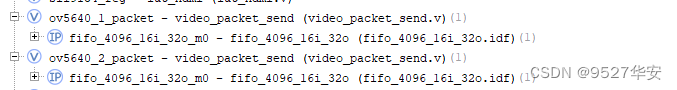

视频数据封装

视频数据封装模块代码位置如下:

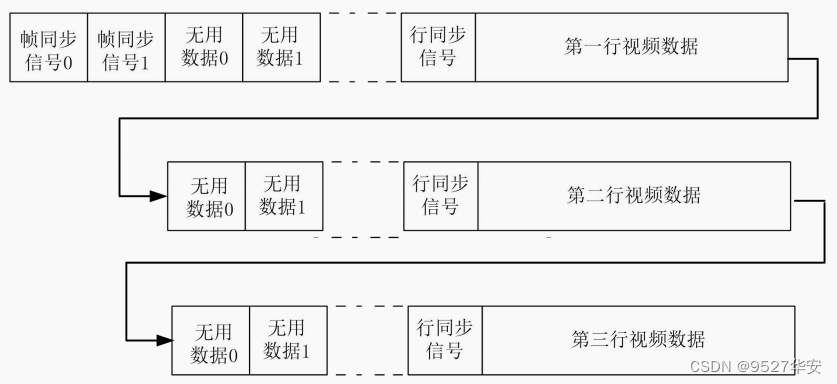

接收到的OV5640摄像头视频数据存放在 16 位进,32 位出的 FIFO 中,视频数据封装由一个状态机来发送视频图像的数据;首先一帧图像开始传输前,HSSTLP 会发送帧同步信号,再判断这个 FIFO 中的数据量,如果 FIFO 内的数据还没有一行的视频数据,HSSTLP 则发送无用的数据;当 FIFO 内已经有一行视频的数据时,HSSTLP 会先发送行同步信号,然后再把这一行视频的数据通过 HSSTLP 发送出去。一行数据发送完成,再重新判断 FIFO 内的数据量,FIFO 数据量达到一行视频数据时,接着发送第二行视频图像。HSSTLP 数据发送一帧图像的流程如下图:

所有的 HSSTLP 发送的数据位数为 32 位,帧同步信号、行同步信号、无用数据属于用户自定义协议的关键部分,这些协议会在后面的视频数据解码模块中做逆向操作,这些协议也就是我们说的“封装”,具体定义如下:

图像帧同步信号 0:定义为 32 位的“ff_00_00_bc”

图像帧同步信号 1:定义为 32 位的“ff_00_01_bc”

插入的无用数据 0:定义为 32 位的“ff_55_55_bc”

插入的无用数据 1:定义为 32 位的“ff_aa_aa_bc”

图像行同步信号:定义为 32 位的“ff_00_02_bc”

这些同步信号和无用数据的高 24 位数据是用户自己定义的,低 8 位"bc"是 K28.5 码控制字符;向 HSSTLP 发送 K28.5 码控制字符时,需要拉高 gt_tx_ctrl 信号的对应位,标示发送数据里的某个字节位为 K 码控制字。所以这里在向 HSSTLP 发送同步信号和无用数据的时候,gt_tx_ctrl 信号设置为 0001,发送视频数据的时候则置为 0000。

按键选择

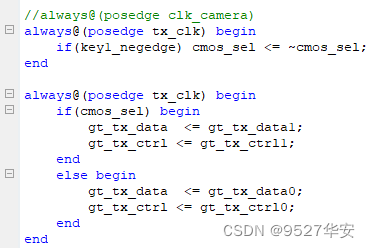

从前面的描述可以知道,此时两路视频是同时经过了数据采集和数据封装来到按键选择模块的,按键选择的作用就是根据按键来选择其中一路将视频送入下一级模块,这部分是整个工程中最简单的,按键选择代码位置如下:

上电默认是选择第二路视频送入下一级模块,当按下板载的按键后,则选择第一路视频送入下一级模块,再按下板载的按键后,则选择第二路视频送入下一级模块。。。如此往复,选择逻辑部分代码如下:

HSSTLP高速收发器详解

HSSTLP基本了解

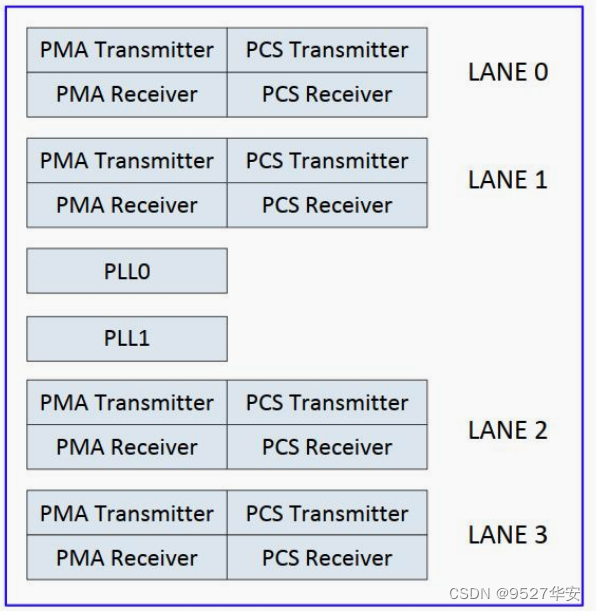

Pango 的 Logos2 系列 FPGA 集成了串行高速收发器 HSSTLP,可以实现高速串行数据通信。其性能基本可以对标Xilinx的GTP,稳定性暂且未知,毕竟没有大规模应用过;HSSTLP收发器支持不同的串行传输接口或协议,支持 PCI Express GEN1, PCI Express,GEN2,XAUI,千兆以太网,CPRI,SRIO 等协议,每通道的收发速度高达 6.6 Gb/s;本设计配置为5G;

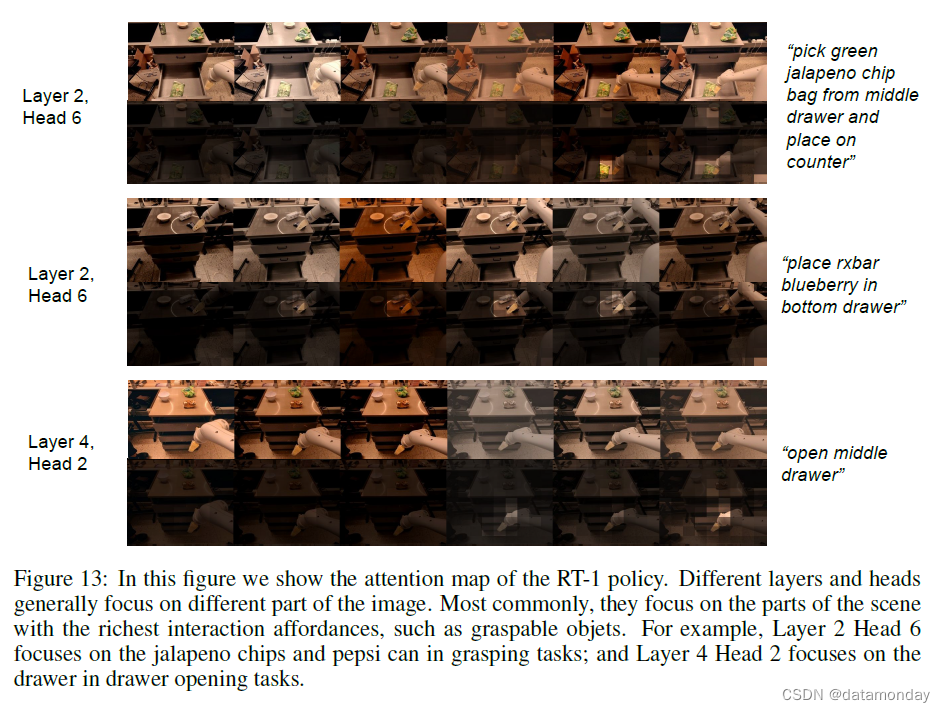

每个 HSSTLP 由两个 PLL 和四个收发 LANE 组成,其中每个 LANE 又包括四个组件: PCS Transmitter,PMA Transmitter, PCS Receiver, PMA Receiver。 PCS Transmitter 和 PMA Transmitter组成发送通路,PCS Receiver 和 PMA Receiver 组成接收通路。 HSSTLP 的结构示意图:

HSSTLP之时钟

HSSTLP 每 个 模 块 有 两 个 差 分 参 考 时 钟 输 入 管 脚 (HSSTREFCLK0P/N_QRX 和HSSTREFCLK1P/N_QRX)作为 HSSTLP 模块的参考时钟源,用户可以自行选择。在我的核心板上,有 2路 125Mhz 的 HSSTLP 的参考时钟连接到 Q3 与 Q6HSSTLP 时钟输入管脚上,作为 HSSTLP 的参考时钟。进入到 PLL0 和 PLL1 中后产生 TX 和 RX 电路中所需的时钟频率。TX 和 RX 收发器速度相同的话,TX 电路和 RX 电路可以使用同一个 PLL 产生的时钟,如果 TX 和 RX 收发器速度不相同的话,需要使用不同的 PLL 时钟产生的时钟。

HSSTLP 中的四个收发 LANE 共享 PLL0 和 PLL1,每个发送或者接收 LANE 都可以独立选择 PLL0或者 PLL1, PLL 工作频率范围为 1.6GHz~6.6GHz。 PLL0 和 PLL1 都各自对应有一对外部差分参考时钟输入,每个 PLL 还可以选择来自另一个 PLL 的参考时钟或者来自 Fabric 的时钟作为参考时钟输入( Fabric 逻辑时钟做参考时钟,仅用于内部测试); PLL 输出频率支持动态再分频,以适应0.6Gbps到6.6Gbps 的 Data Rate 范围。

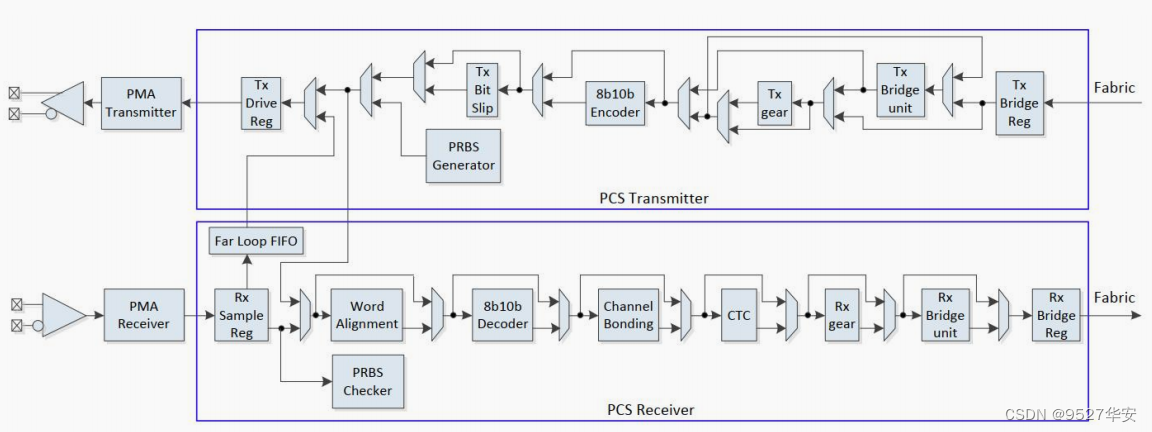

HSSTLP之PCS

PCS Transmitter 和 Receiver 结构框图如下:

每个 PCS Transmitter 主要包含以下模块:

Tx Bridge Reg 模块: 用于从 Fabric 到 PCS Transmitter 的数据桥接;

Tx Bridge unit 模块: 用于 PCS Transmitter 内部时钟域和 Fabric 时钟域相位补偿;

8b10b Encoder 模块:完成符合 IEEE 802.3 1000BASE-X specification 的 8b10b 编码;

Tx gear 模块: 完成 64b66b/64b67b 数据适配功能;

Tx Bit Slip 模块: 主要功能是根据配置对发送数据实现按位 Slip;

PRBS Generator 模块: 产生 PRBS 测试序列;

Tx Drive Reg 模块: 用于从 PCS Transmitter 到 PMA Transmitter 数据桥接;

每个 PCS Receiver 主要包含以下功能模块:

Rx Sample Reg 模块: 用于从 PMA Receiver 到 PCS Receiver 的数据桥接;

PRBS Checker 模块:用于 PRBS 序列的校验;

Word Alignment 模块:支持灵活的 Word Alignment 功能;

8b10b Decoder 模块:完成符合 IEEE 802.3 1000BASE-X Specification 的 8b10b 解码;

Rx gear 模块: 完成 64b66b/64b67b 数据适配功能;

Channel Bonding 模块:用于通道对齐;

CTC 模块:用于补偿发送时钟和接收时钟的微小频差;

Rx Bridge unit 模块:用于 PCS Receiver 内部时钟域和 Fabric 时钟域相位补偿;

Rx Bridge Reg 模块:用于从 PCS Receiver 到 Fabric 的数据桥接。

HSSTLP之PMA

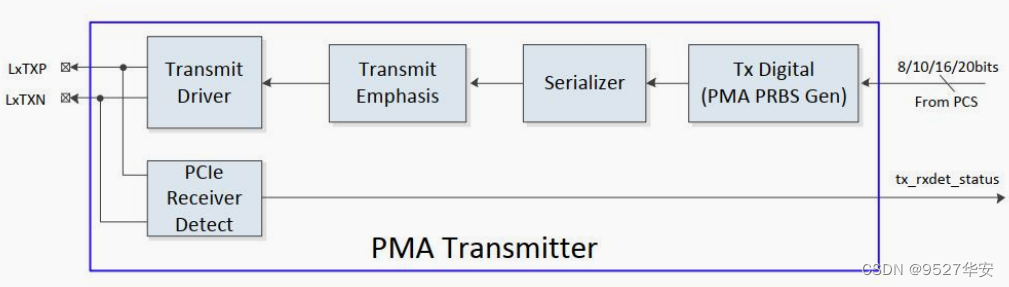

PMA Transmitter 功能示意图如下:

每个 PMA Transmitter 主要包含以下功能模块:

Tx Digital 模 块 : 完 成 PCS Transmitter 到 PMA Transmitter 的 数 据 桥 接 , 以 及 PMA PRBSGenerator;

Serializer 模块: 完成并行数据到串行数据的转换功能;

Transmit Emphasis 模块: 支持可调节的去加重功能;

Transmit Driver 模块: 支持可调节的发送驱动;

PCI Express Receiver Detect 模块:支持基于 PCI Express 的 Receiver Detection 功能;

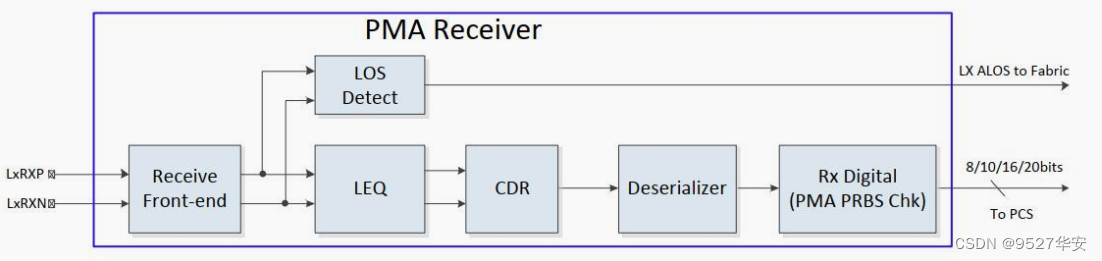

PMA Receiver 功能示意图如下:

每个 PMA Receiver 主要包含以下功能模块:

Receive Front-end 模块:支持多种接收 Termination 模式;

LEQ 模块:支持 Linear Equalizer 功能;

CDR 模块:数据和时钟恢复功能;

LOS Detect 模块:用于检测接收信号是否有效功能;

Deserializer 模块: 完成串行数据到8 bits, 10bits, 16bits 以及 20bits 并行数据的转换功能;

Rx Digital 模块: 完成 PMA Receiver 到 PCS Receiver 的数据桥接,以及 PMA PRBS Checker;

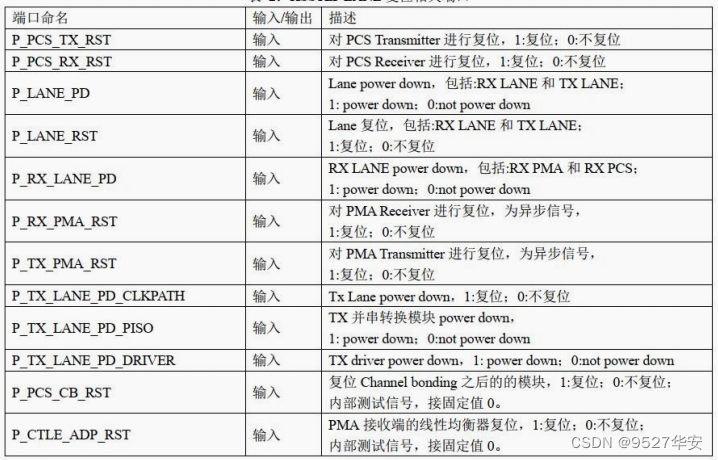

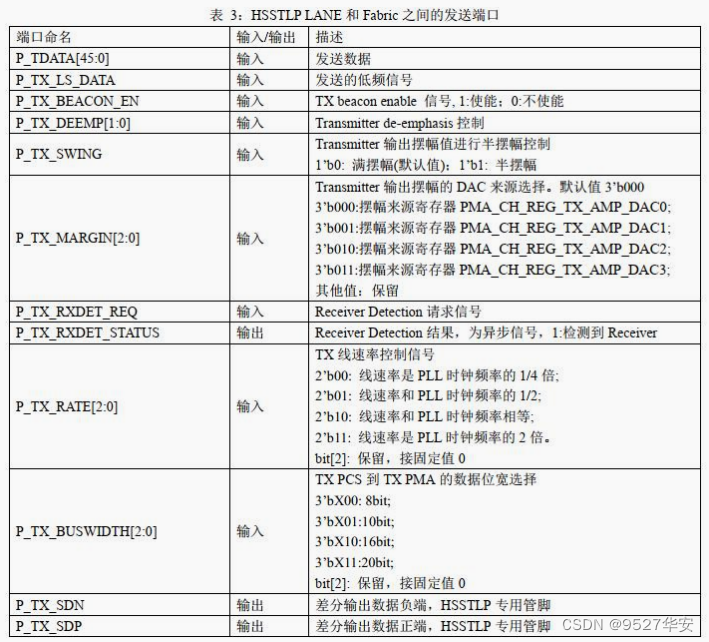

HSSTLP之接口说明

接口信号是 FPGA 的用户数据与 HSSTLP 的接口连接信号,该接口信号的名称和说明如下表所示:

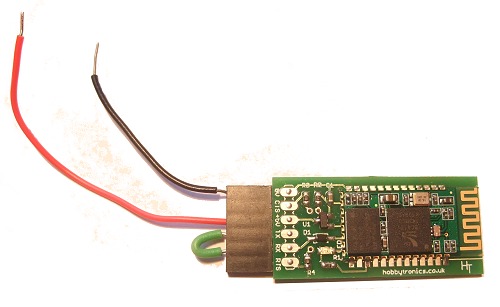

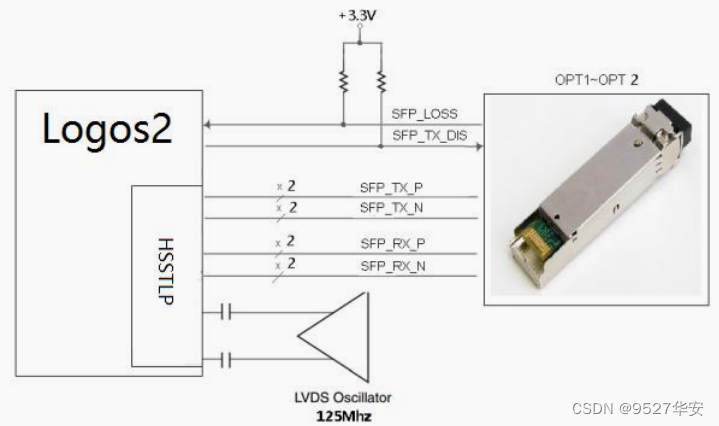

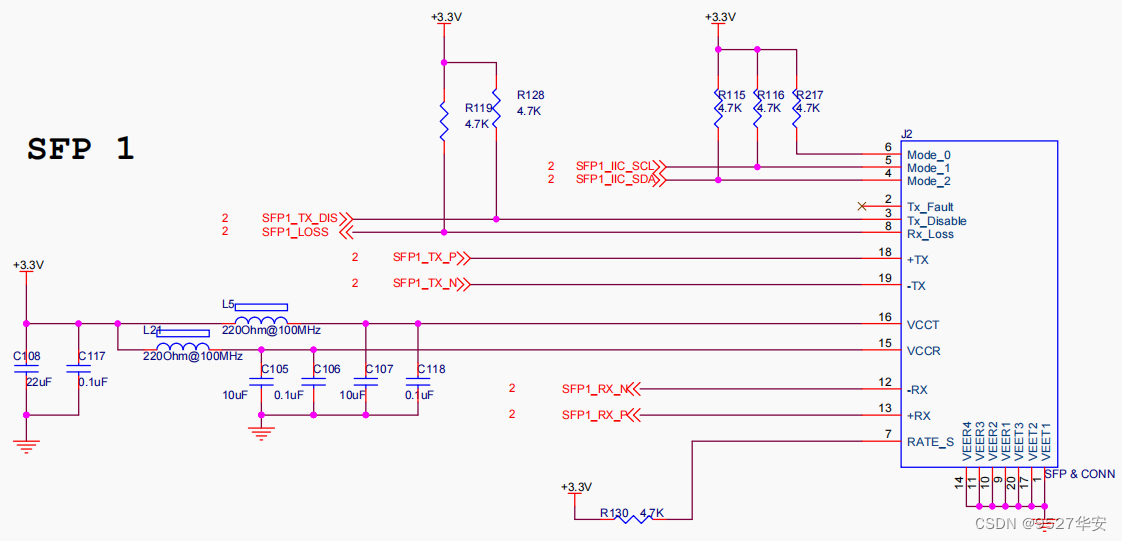

硬件设计

在我的开发板上,有 2 路光纤接口 SFP1~SFP2, 分别连接到 FPGA 芯片的 HSSTLP 的通道上。FPGA和光纤连接的设计示意图如下图所示:

其中 SFP1 光模块接口连接到 Q3 HSSTLP 的 Channel3 上,SFP2 跟 Q3 HSSTLP 的的 Channel2 相连。光模块和 FPGA 之间用 0.1uf 的电容隔开,使用 AC Couple 的模式。光模块的 LOSS 信号和 TX_Disable 信号连接到 FPGA 的普通 IO 上,LOSS 信号用来检测光模块的光接收是否丢失,如果没有插入光纤或者 Link 上,LOSS 信号为高,否则为低。TX_Disable 信号用来使能或者不使能光模块的光发射,如果 TX_Disable 信号为高,光发射关闭,否则光发送使能,正常使用的时候需要拉低此信号。硬件原理图如下:

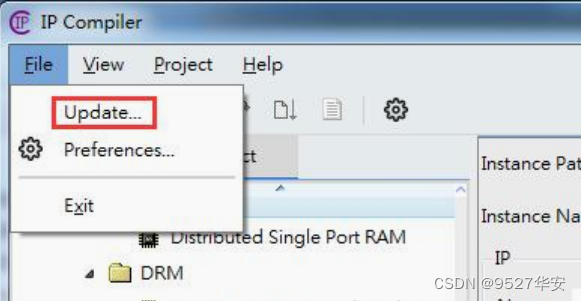

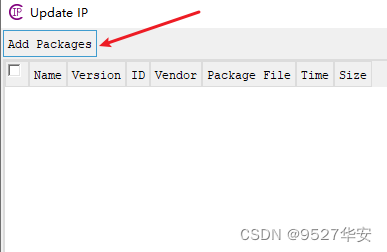

HSSTLP IP调用和配置

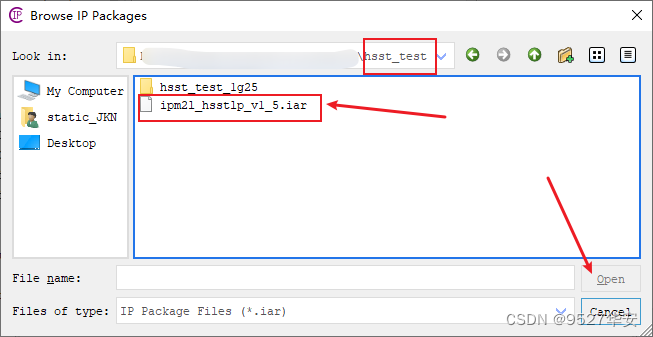

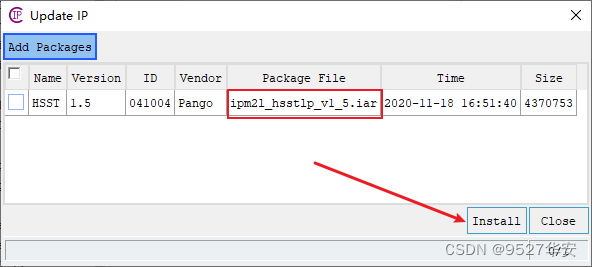

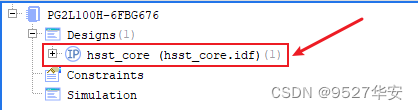

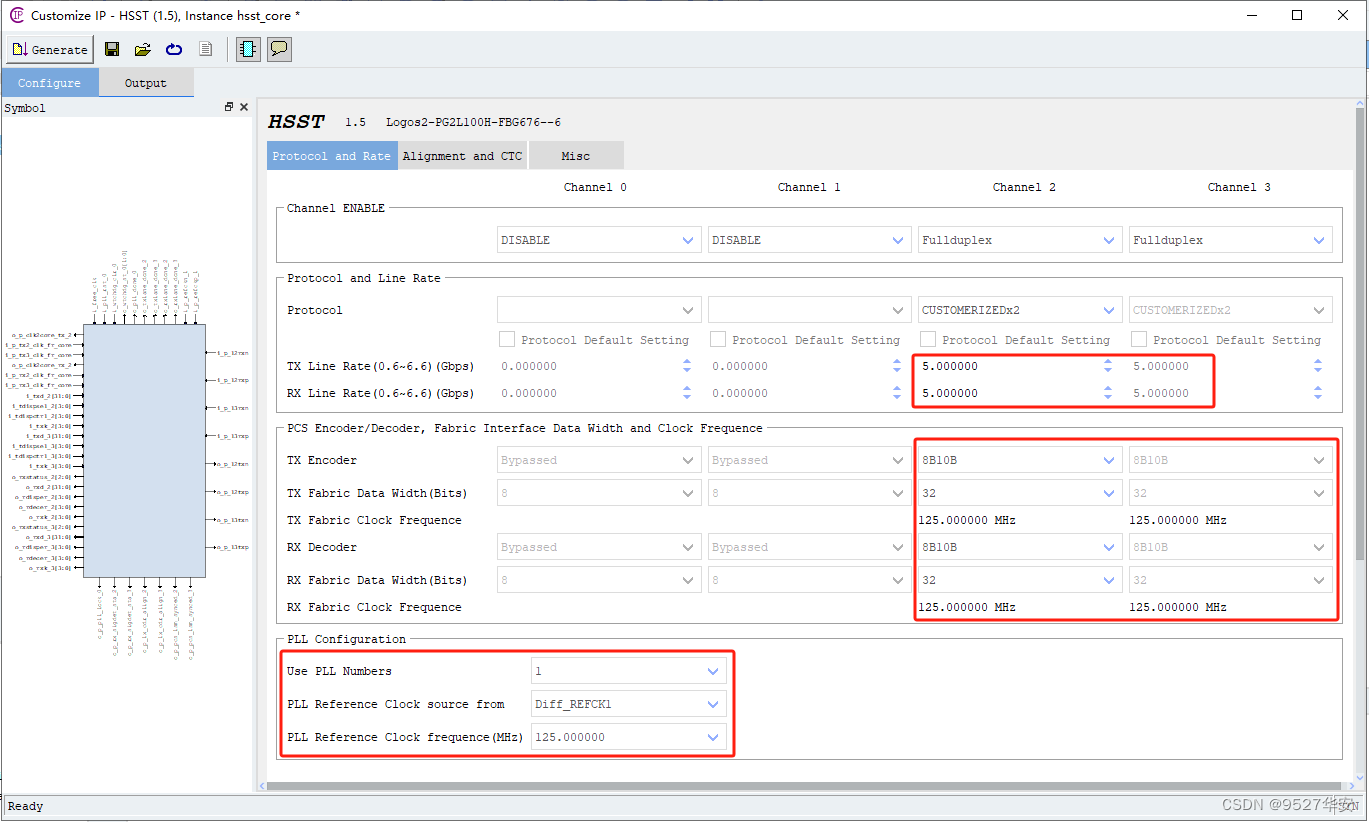

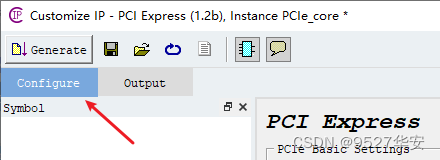

我们提供HSSTLP IP核文件,新建一个PDA工程,然后按照如下步骤添加HSSTLP IP核添加并配置:

本设计配置为5G;

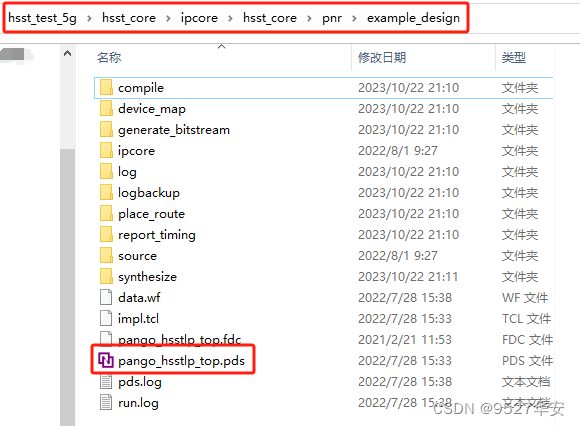

配置完成后,点击“Generate”产生 HSSTLP的Eample工程,如下:

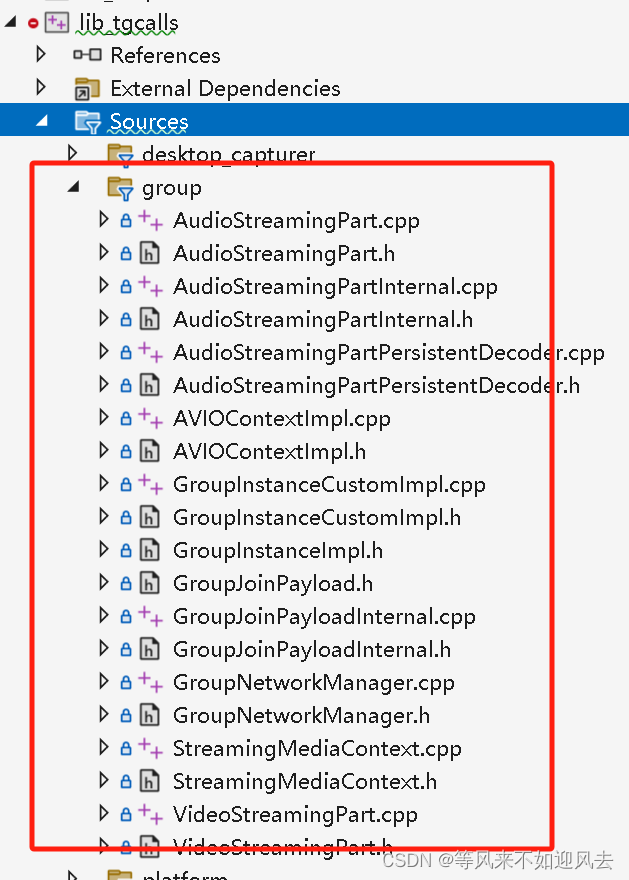

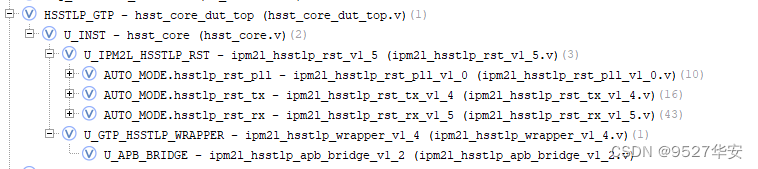

这只是官方IP自动生成的Example工程,为了做HSSTLP高速接口视频传输,我们将Example工程里的源码复制出来做修改,加上用户接口,即可提供给用户使用,代码位置如下:

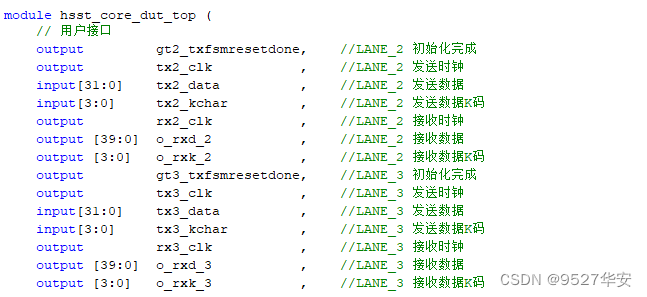

封装后的顶层用户数据接口如下:

5G配置的工程是一个单独的工程,但我们不用这个工程,如果你想把线速率改为其他时可以打开这个工程重新配置,配置好以后复制其Example工程里的源码复制出来做修改,5G配置的工程如下:

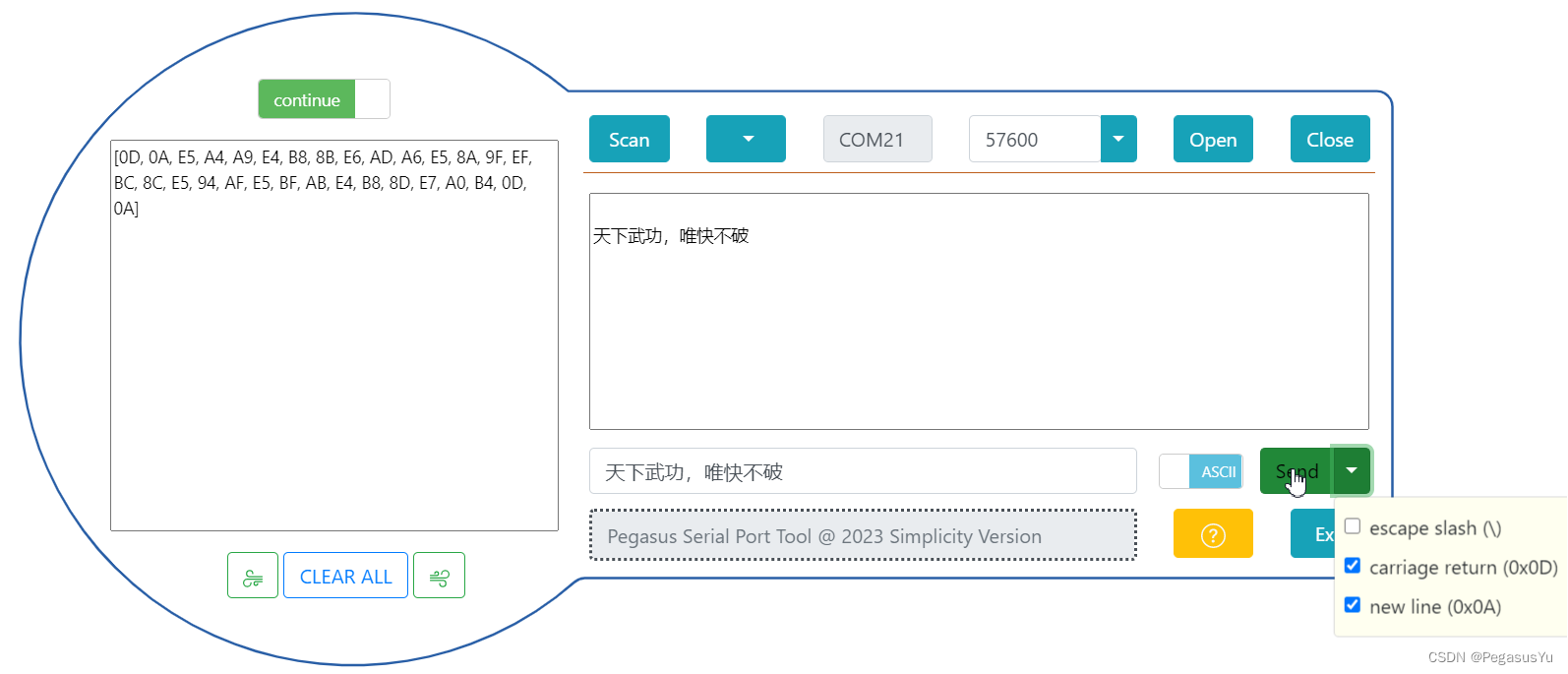

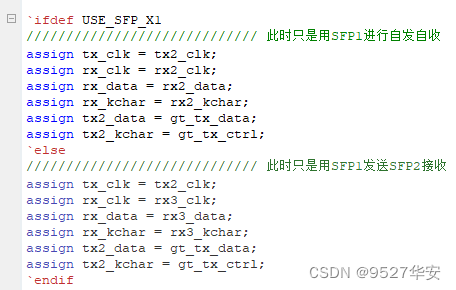

SFP连接方案选择

提供两种SFP连接方案,一种是使用一个SFP光口做数据连接,即同一个SFP的TX连接RX,另一种是使用两个SFP光口做数据连接,即SFP1的TX连接SFP2的RX,在PDS工程代码中,通过define宏定义来选择其中一种方案;上电默认选择第一种方案,即第3章节设计框图中的工程1;SFP连接方案选择代码选择逻辑代码如下:

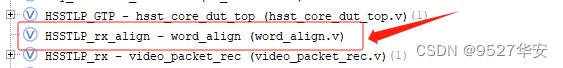

视频数据对齐

视频数据对齐模块利用K码的特性将HSSTLP接收的数据对齐,代码位置如下:

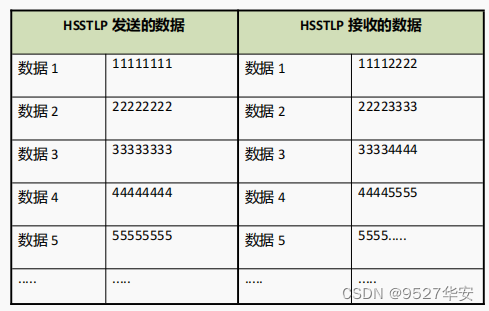

收发器外部用户数据接口的宽度为 32 位,内部数据宽度为 20 位(8b/10b 转换)。在实际测试过程中发现,发送的 32 位数据会有可能出现 16 位的数据的移位,就是说发送的数据和接收到的数据会有 16 位的错位,下表演示发送数据和接收数据移位的情况:

因为我们在发送同步信号和无用数据的时候加入了 K 码控制字,并且设置 gt_tx_ctrl 信号为0001, 如果出现 16 位数据移位的情况,接收到的同步信号和无用数据时,K 码控制字也会跟着移位,gt_tx_ctrl 的信号就会变成 0100,所以我们在程序可以通过判断 gt_tx_ctrl 信号的值来判断接收到的数据是否移位,如果接收到的 gt_tx_ctrl 为 0001,跟我们发送的时候一样,说明数据没有移位;如果接收到的 gt_tx_ctrl 为 0100,接收到的数据移位,需要重新组合;

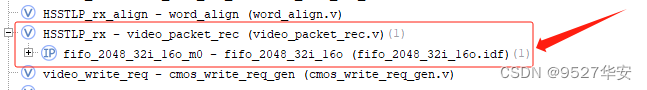

视频数据解码

视频数据解码模块是视频数据封装模块的逆过程,代码位置如下:

因为接收到的 32 位数据中只有一部分是视频图像的数据,其它的是帧同步,行同步和无用的数据,即前面提到的协议或者“封装”,在视频数据解码模块里需要把视频图像的数据解析出来存入到一个 32 位进8 位出的 FIFO 中。程序的一个功能是检测 HSSTLP 数据中的行同步信号(数据为 ff_00_02_bc),如果接收到行同步信号,就把后面接收的一行视频数据存放到 FIFO 中。程序的另一个功能是恢复视频图像的帧同步信号(数据为 ff_00_00_bc),如果接收到帧同步信号,则置位视频图像的帧信号 vs。另外模块中会判断 FIFO 中存入的视频数据,如果 FIFO 内的数据量大于一行视频的数据,则产生 FIFO 的读使能信号,把 FIFO 的一行视频数据输出给外部接口模块。

图像缓存架构详解

架构讲解

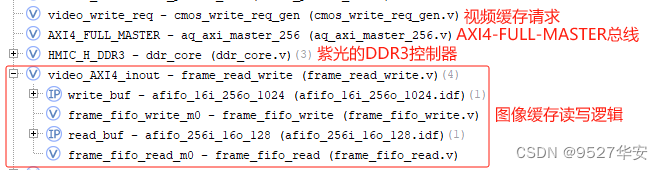

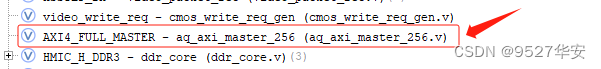

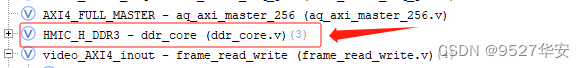

本设计的图像缓存架构基于AXI4-FULL-MASTER总线,加上用户读写逻辑实现视频缓存外部DDR3的功能,代码位置如下:

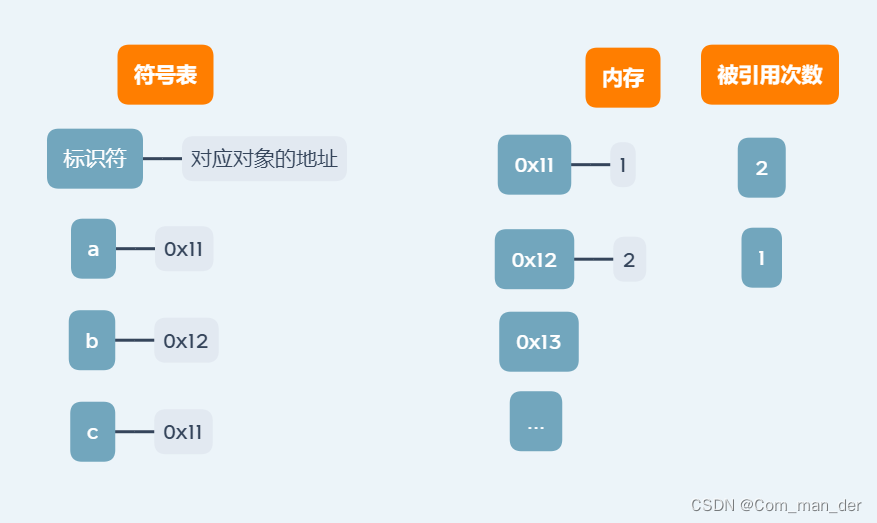

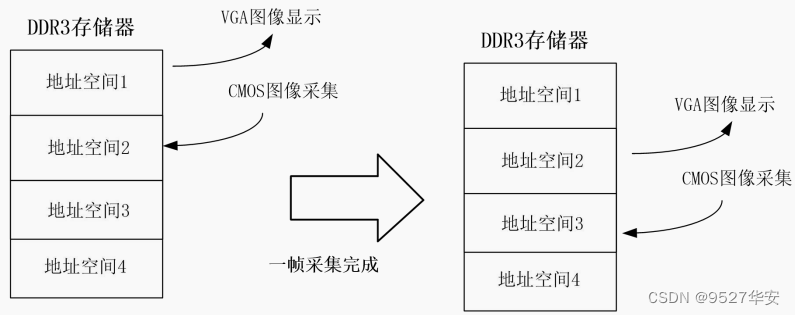

本架构关键的地方在于视频同时读写,如何做到读写不冲突?在设计帧读写模块时就已经考虑到这点,所以有帧基地址选择,最大 4 帧选择,每次读视频帧地址和正在写的帧地址是不同的,而是上次写入一帧数据的地址,这样就可以避免读写冲突,避免视频画面裂开错位,设计框图如下:

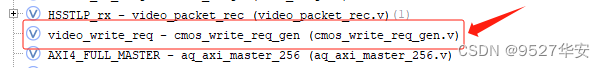

视频缓存请求

视频缓存请求模块通过判断摄像头的列同步信号 cmos_vsync 的上升沿,生成ov5640 数据写入的请求信号,表示一帧图像开始写入请求。另外生成 write_addr_index 写地址选择和 read_addr_index 读地址选择,这里 read_addr_index 的值会比 write_addr_index 的值延迟一帧,使得读和写的地址不冲突;代码位置如下:

模块顶层接口如下:

AXI总线

这是一个加了FIFO用户接口的AXI4 FULL MASTER总线,作用是对接紫光的DDR3控制器HMIC_H,代码位置如下:

他的设计也很简单,即标准的AXI协议加上FIFO用户接口,这里不过多介绍,详情参考代码;

HMIC_H

HMIC_H是紫光的DDR3控制器IP,这里调用该IP,根据自己板子的DDR3型号做配置,我这里配置IP后,打开了IP的Eample工程,并将其源码复制出来放到了工程中,所以在工程中看不到HMIC_H IP核的身影,这种用法和直接调用IP是一样的,只不过方便修改里面的代码和引出仿真接口,优点是修改调试方便,缺点是其IP的使用熟练程度较高,不喜欢这种用法的朋友可以改为调用IP方式;代码位置如下:

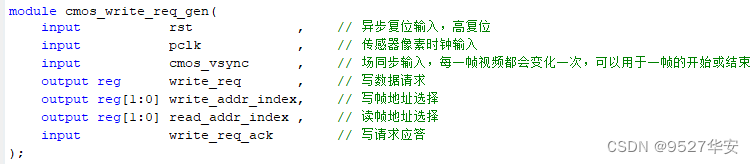

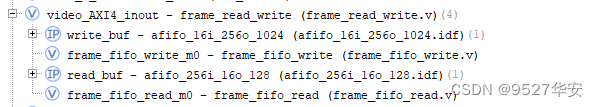

图像缓存读写逻辑

图像缓存读写逻辑模块把摄像头采集的数据存入写 FIFO 里,然后产生 DDR3 的 Burst 写请求,写入到 DDR3 中,另外读也是一样,当读 FIFO里 的 数 据 小 于 一 定 值 时,产 生 DDR3 的 Burst 读 请 求,代码位置如下:

模块顶层接口如下:具体实现过程参考源代码;

module frame_read_write #

(

parameter MEM_DATA_BITS = 16,

parameter READ_DATA_BITS = 16,

parameter WRITE_DATA_BITS = 16,

parameter ADDR_BITS = 24,

parameter BUSRT_BITS = 10,

parameter BURST_SIZE = 128

)

(

input rst , // 异步复位输入,高复位

input mem_clk , // 外部存储器用户时钟输入

output wr_burst_req , // 对接存储器控制器,写请求

output[BUSRT_BITS - 1:0] wr_burst_len , // 对接存储器控制器,写请求长度

output[ADDR_BITS - 1:0] wr_burst_addr , // 对接存储器控制器,写请求基地址

input wr_burst_data_req , // 对接存储器控制器,写请求数据索取,提前一个时钟周期发出,用于连接 FIFO 的读数据

output[MEM_DATA_BITS - 1:0] wr_burst_data , // 对接存储器控制器,写数据

input wr_burst_finish , // 对接存储器控制器,写请求完整

input write_clk , // 对用户,写时钟

input write_req , // 对用户,一帧(大量数据)写开始,收到应答后必须撤销请求,新的请求会中断正在进行的请求

output write_req_ack , // 对用户,一帧(大量数据)写应答

output write_finish , // 对用户,一帧(大量数据)完成

input[ADDR_BITS - 1:0] write_addr_0 , // 对用户,一帧(大量数据)写基地址 0

input[ADDR_BITS - 1:0] write_addr_1 , // 对用户,一帧(大量数据)写基地址 1

input[ADDR_BITS - 1:0] write_addr_2 , // 对用户,一帧(大量数据)写基地址 2

input[ADDR_BITS - 1:0] write_addr_3 , // 对用户,一帧(大量数据)写基地址 3

input[1:0] write_addr_index , // 对用户,一帧(大量数据)写基地址选择,0:write_addr_0,1:write_addr_1,2:write_addr_2,3:write_addr_3

input[ADDR_BITS - 1:0] write_len , // 对用户,一帧(大量数据)写长度

input write_en , // 对用户,写使能

input[WRITE_DATA_BITS - 1:0] write_data , // 对用户,写数据

output rd_burst_req , // 对接存储器控制器,读请求

output[BUSRT_BITS - 1:0] rd_burst_len , // 对接存储器控制器,读请求长度

output[ADDR_BITS - 1:0] rd_burst_addr , // 对接存储器控制器,读请求基地址

input rd_burst_data_valid, // 对接存储器控制器,读请求数据有效

input[MEM_DATA_BITS - 1:0] rd_burst_data , // 对接存储器控制器,读请求数据

input rd_burst_finish , // 对接存储器控制器,读请求完全

input read_clk , // 对用户,读时钟

input read_req , // 对用户,一帧数据读开始

output read_req_ack , // 对用户,一帧数据读应答

output read_finish , // 对用户,一帧数据读完成

input[ADDR_BITS - 1:0] read_addr_0 , // 对用户,一帧数据读基地址 0

input[ADDR_BITS - 1:0] read_addr_1 , // 对用户,一帧数据读基地址 1

input[ADDR_BITS - 1:0] read_addr_2 , // 对用户,一帧数据读基地址 2

input[ADDR_BITS - 1:0] read_addr_3 , // 对用户,一帧数据读基地址 3

input[1:0] read_addr_index , // 对用户,一帧(大量数据)读基地址选择,0:read_addr_0,1:read_addr_1,2:read_addr_2,3:read_addr_3

input[ADDR_BITS - 1:0] read_len , // 对用户,一帧(大量数据)读长度

input read_en , // 对用户,读使能

output[READ_DATA_BITS - 1:0] read_data // 对用户,读数据

);

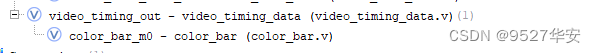

输出视频时序

输出视频为标准的VGA时序,配置为1280x720@60Hz,采用纯verilog代码实现,底层为一个彩条图像,在其上叠加输出的视频图像,这样做的目的是测试该模块,如果说屏幕上只有彩条而没有视频图像,则说明输出视频时序模块是OK的,视频输入或缓存可能有问题,代码位置如下:

sil9134配置

视频数据缓存到DDR3中缓存后输出送入输出显示时序模块,然后将输出视频送入sil9134芯片进行HDMI编码输出,最后连接显示器,即可显示输出图像;sil9134配置由纯verilog代码实现,这里配置为输出自适应,本设计的输出为1280x720@60Hz,代码位置如下:

4、PDS工程详解

开发板FPGA型号:紫光同创–PGL22G-6MBG324;

开发环境:Pango Design Suite 2021.4

输入:双目OV5640摄像头,分辨率为1280x720;

输出:SFP光口和HDMI;

工程作用:紫光同创FPGA实现HSSTLP高速接口视频传输;

工程代码架构如下:

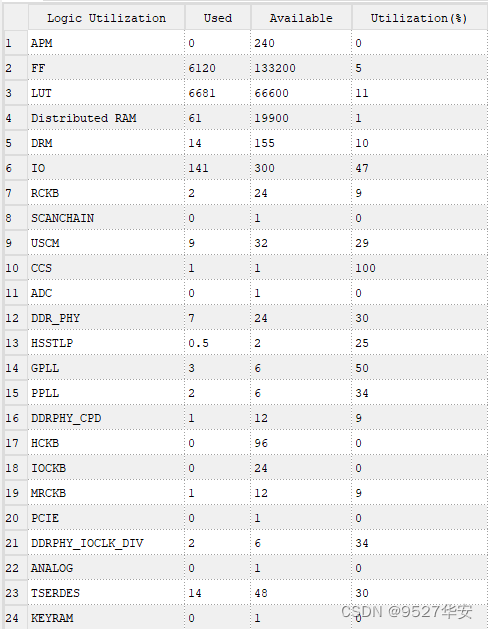

工程的资源消耗如下:

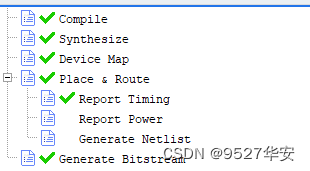

工程已经综合编译完成,如下:

5、上板调试验证并演示

准备工作

连接开发板:

连接好摄像头,下载bit;

静态演示

HSSTLP高速接口视频传输,HDMI输出静态演示如下:

6、福利:工程源码获取

福利:工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:私,或者文章末尾的V名片。