萌新的SOC学习之自定义IP核的学习与设计

本章为了更加深入的了解FPGA的自定义IP和IP封装测试等问题

参考了正点原子 第六讲自定义IP核呼吸灯实验 和 第十九章 IP封装与接口定义实验

为了更好的理解自定义IP核

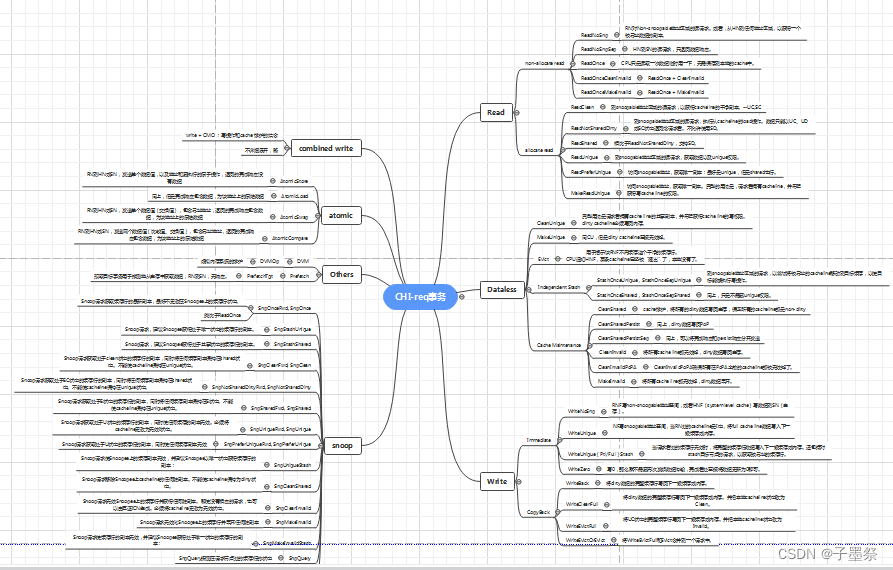

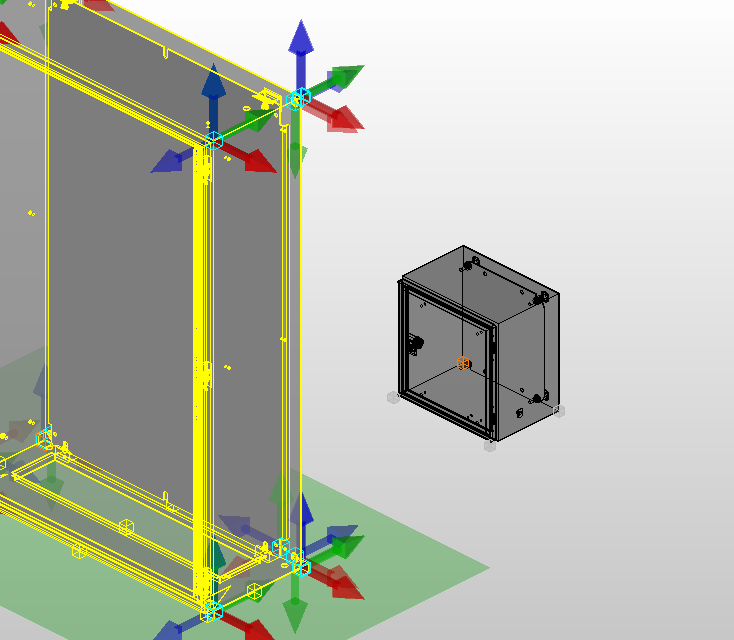

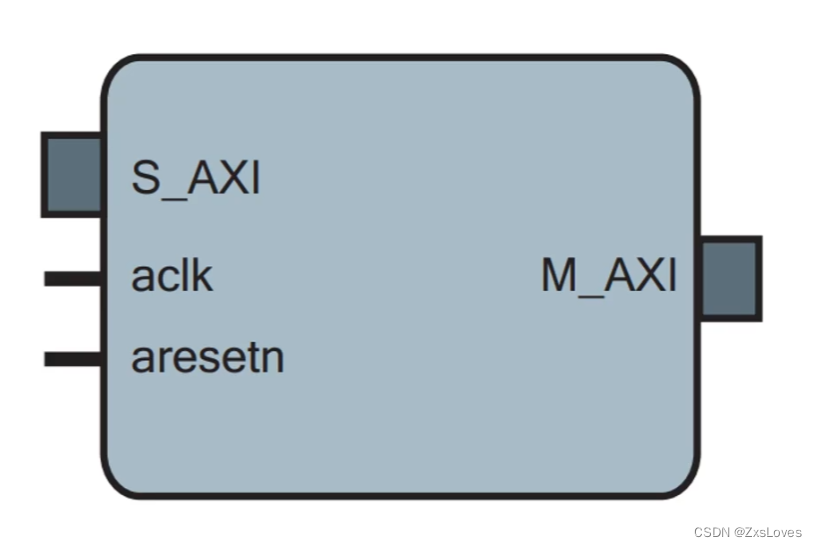

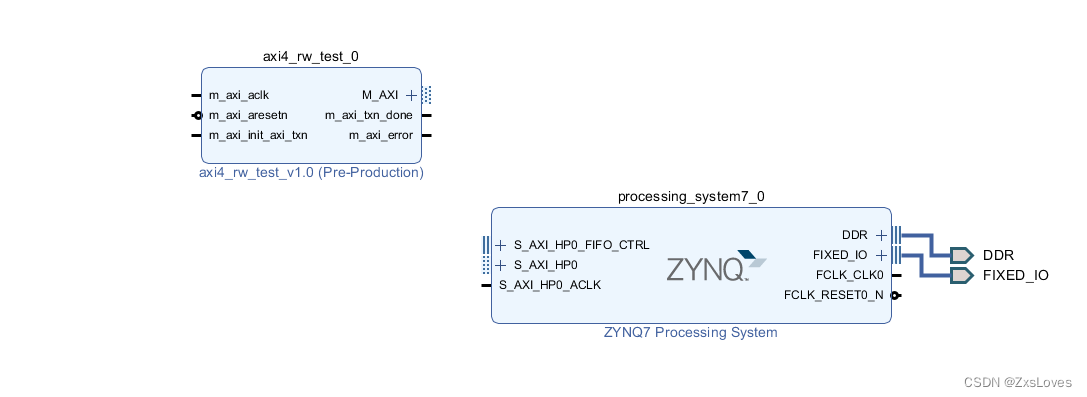

我们先介绍一个带AXI主从接口的IP核

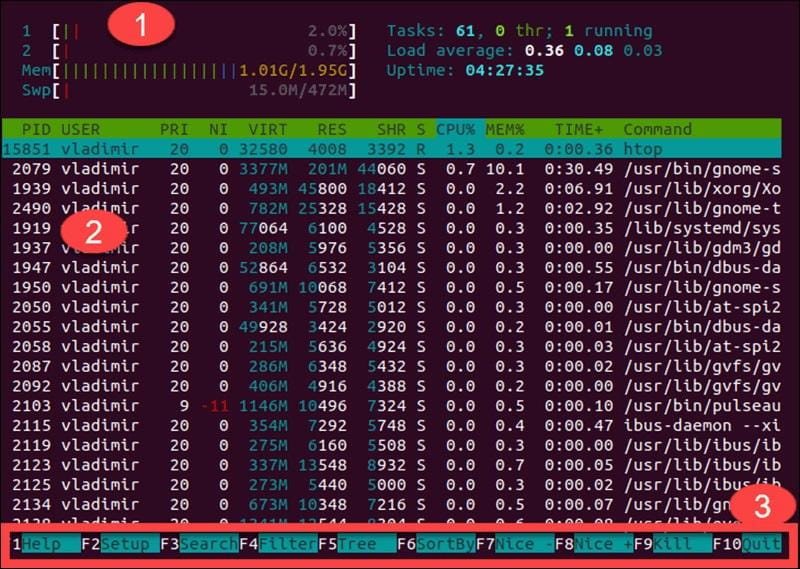

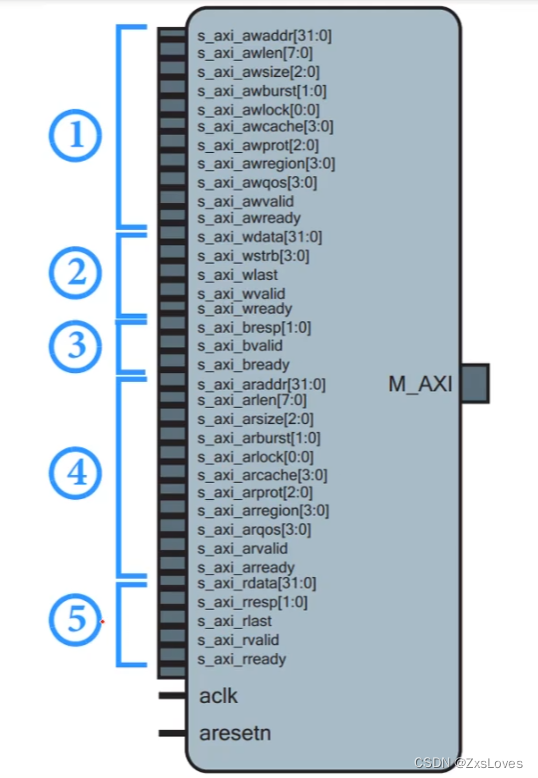

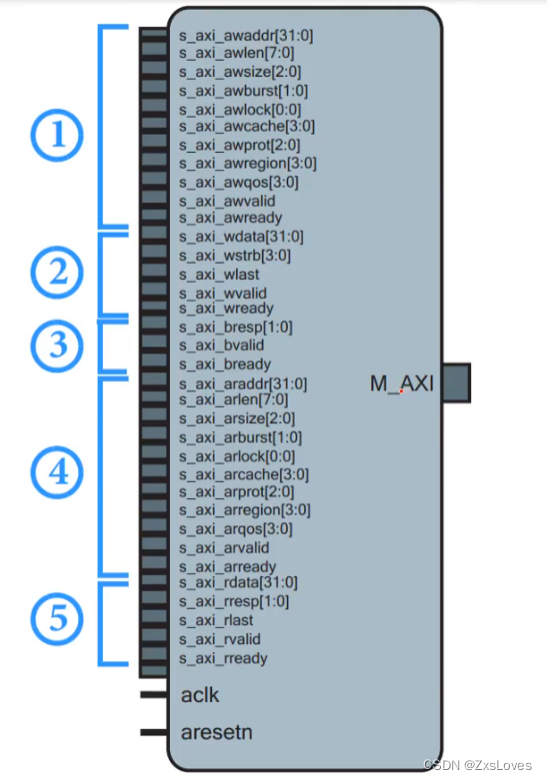

我们可以展开AXI从接口

下面开始vivado 工程的创建

我们创建的这个IP核 默认提供的功能是 根据外部的输入按键 当检测到上升沿的时候 它就开始对DDR3内存 开始读写 读写的范围是4096个字节

先写 然后 读 读完之后做一个比较 如果读写正确 会有一个 error 信号 读写正确 error 信号拉低 读写错误 把 error 信号拉高

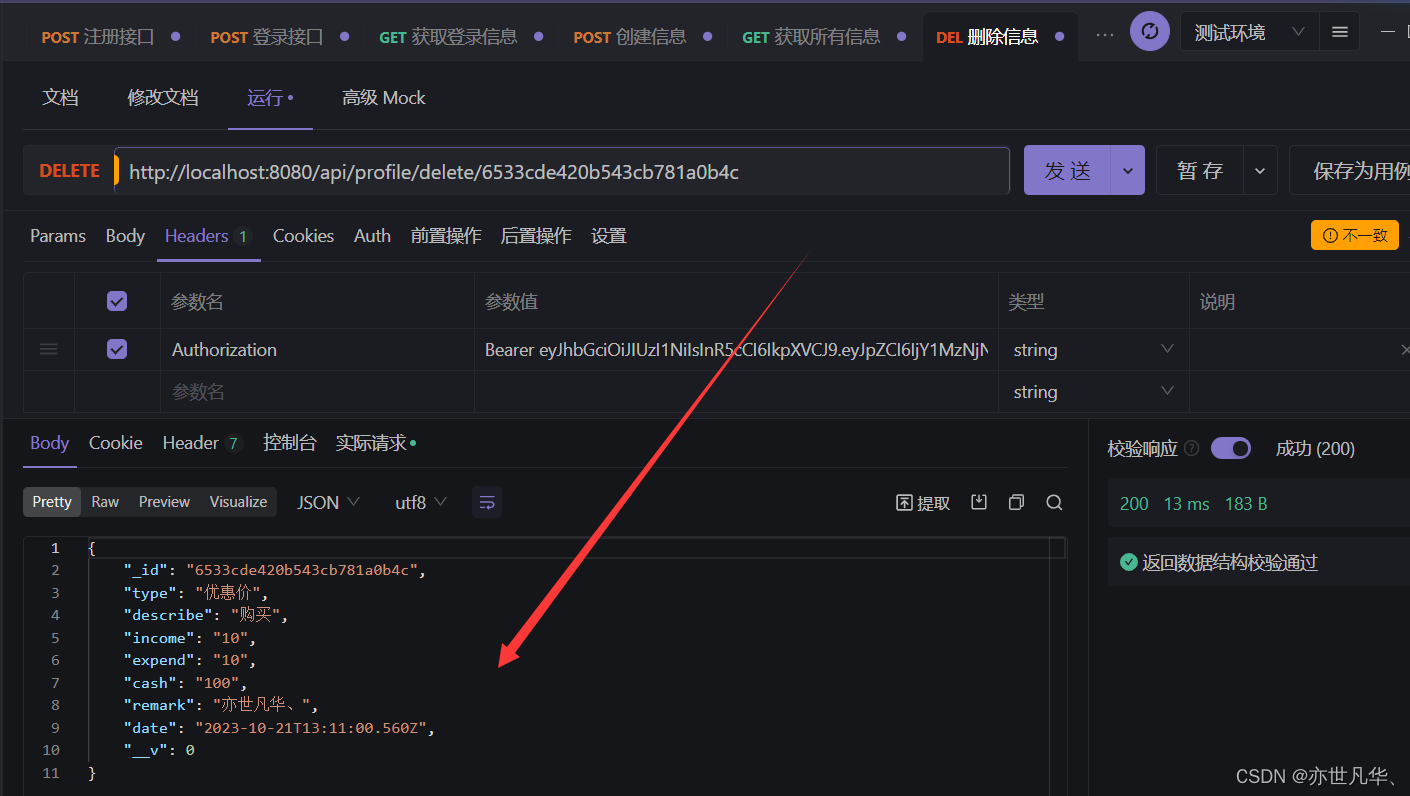

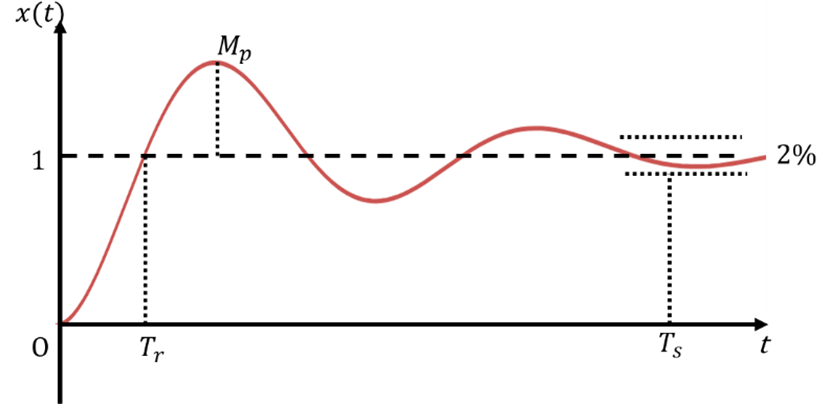

下面介绍 AXI4 接口 之DDR读写实验

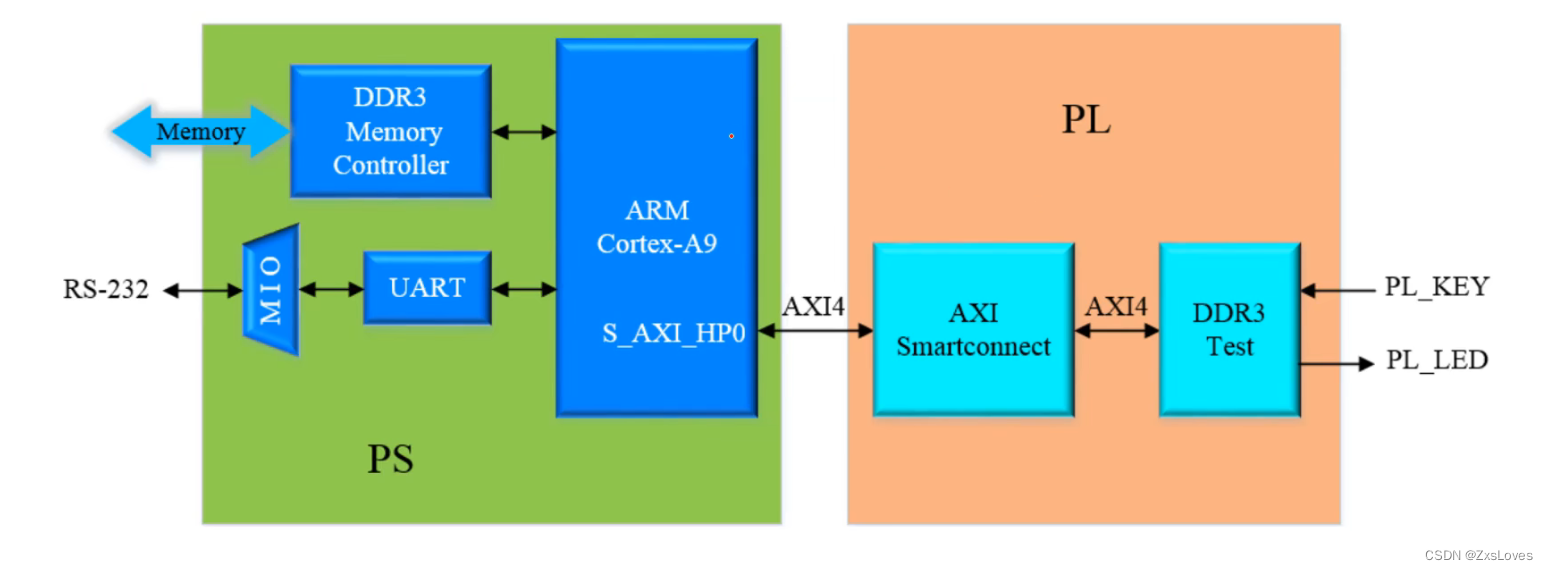

实验任务 : 本章的实验任务是通过自定义的一个AXI4 接口的 IP核,通过AXI_HP 接口 对PS 端 DDR3 进行读写测试

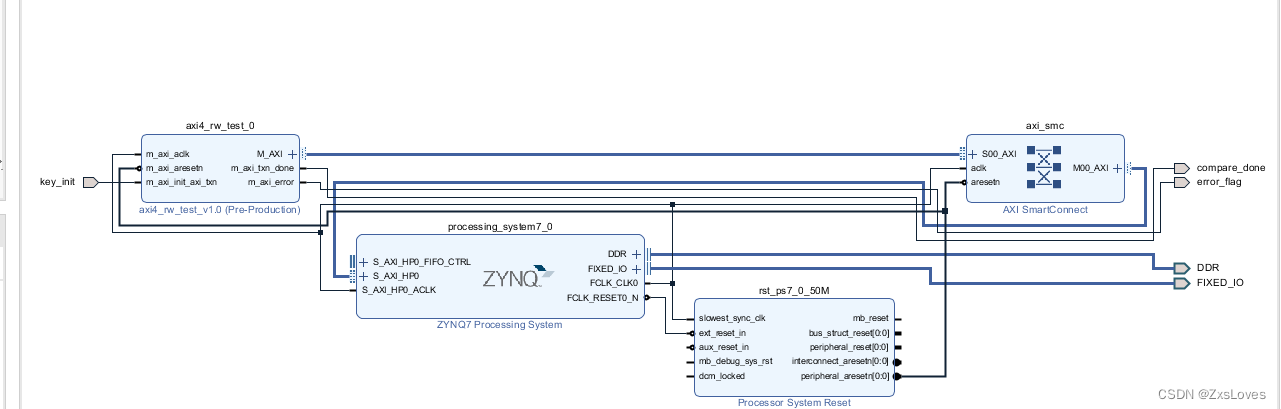

我们查看本次实验的系统框图

这个DDR3 Test IP核 就是我们自己设置的

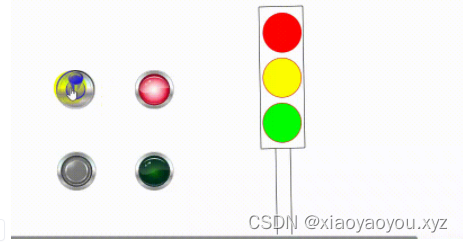

有一个输入端口信号连接到了 PL_KEY 按键 还有两个输出 分别连接到了两个灯

把上面自定义的IP添加进入整个设计

#include"stdio.h"

//为了保证访问DDR的一致性 我们把 cache 缓存关掉

#include"xil_cache.h"

#include"xil_printf.h"

#include"xil_io.h"

int main()

{

int i ;

char c ;

Xil_DCacheDisable();

printf("AXI4 PL DDR TEST!\n\r");

while(1)

{

scanf("%c",&c);

if(c == 'c')

{

printf("start\r\n");

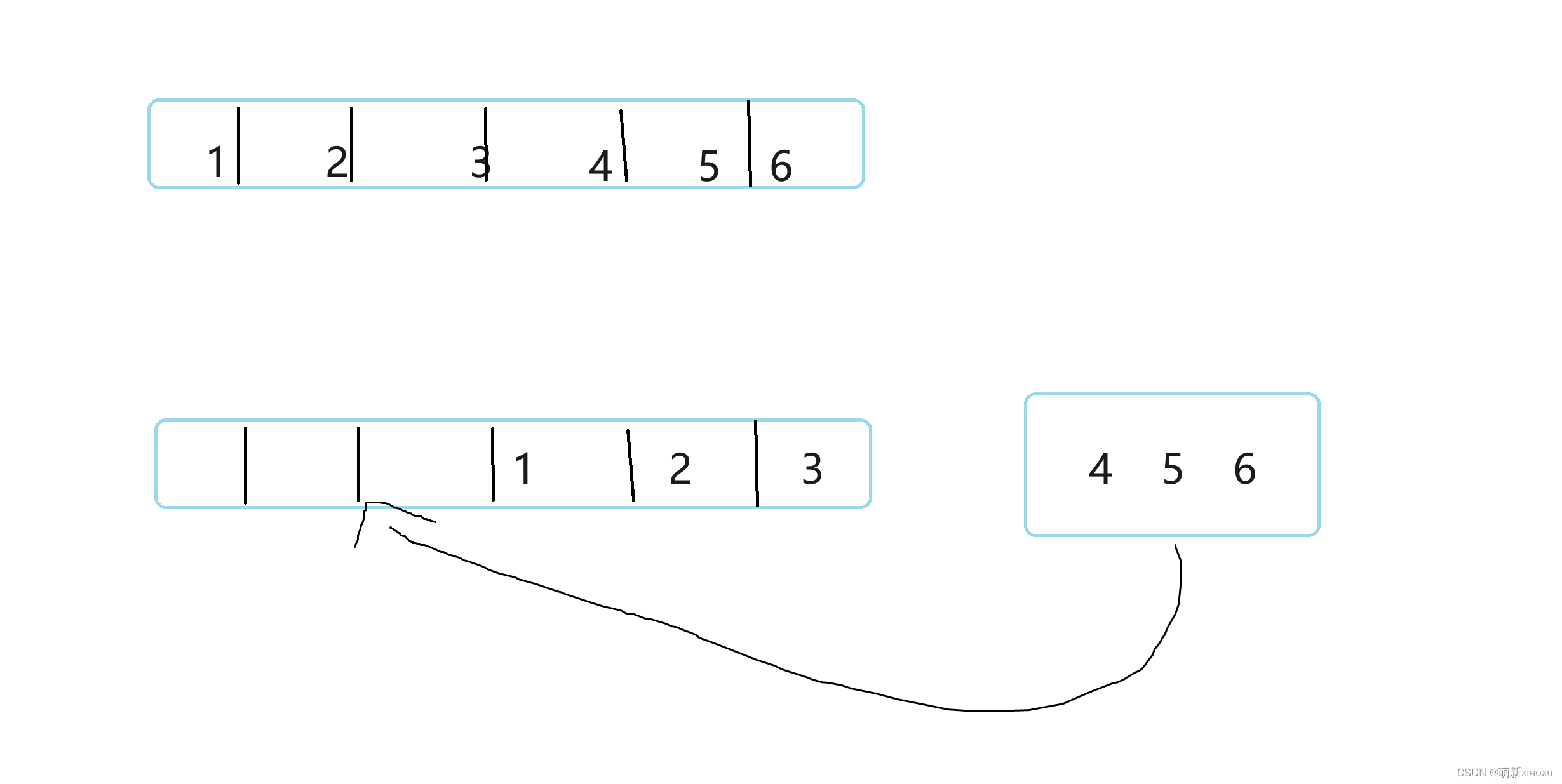

for(i=0;i<4096;i=i+4)// 为什么是i+4因为单次是读4个字节

{

printf("%d is %d\n",i,(int)(Xil_In32(0x10000000+i)));

}

}

}

return 0 ;

}

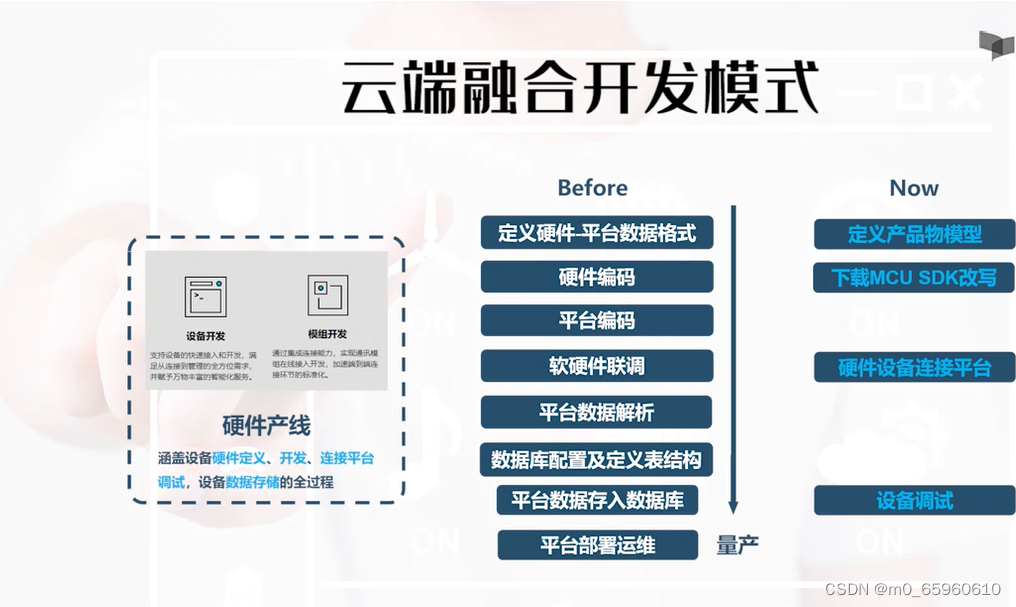

前面我们用的更多的是xillix官方提供的 AXI4 AXI4-lite

我们想要把verilog文件封装成ip核 这样我们在后续的实验 操作时 可以很容易的调用这个ip核完成实验

我们接下来还会学习一下接口的定义 (什么是接口 我们回忆一下做的 AXI4 的 数据实验 我们会想起来 我们在外面进行的交互是以接口的形式 并不会把简单的一个个端口给暴露出来 )

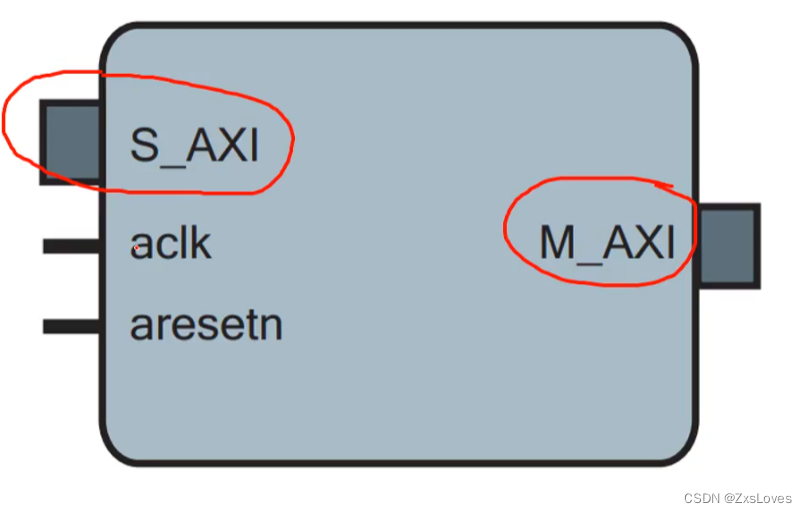

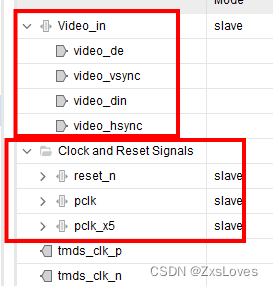

下面展示带 AXI主从接口的IP核

这是接口 我们可以通过点击 + 号 将所有的端口都展示出来

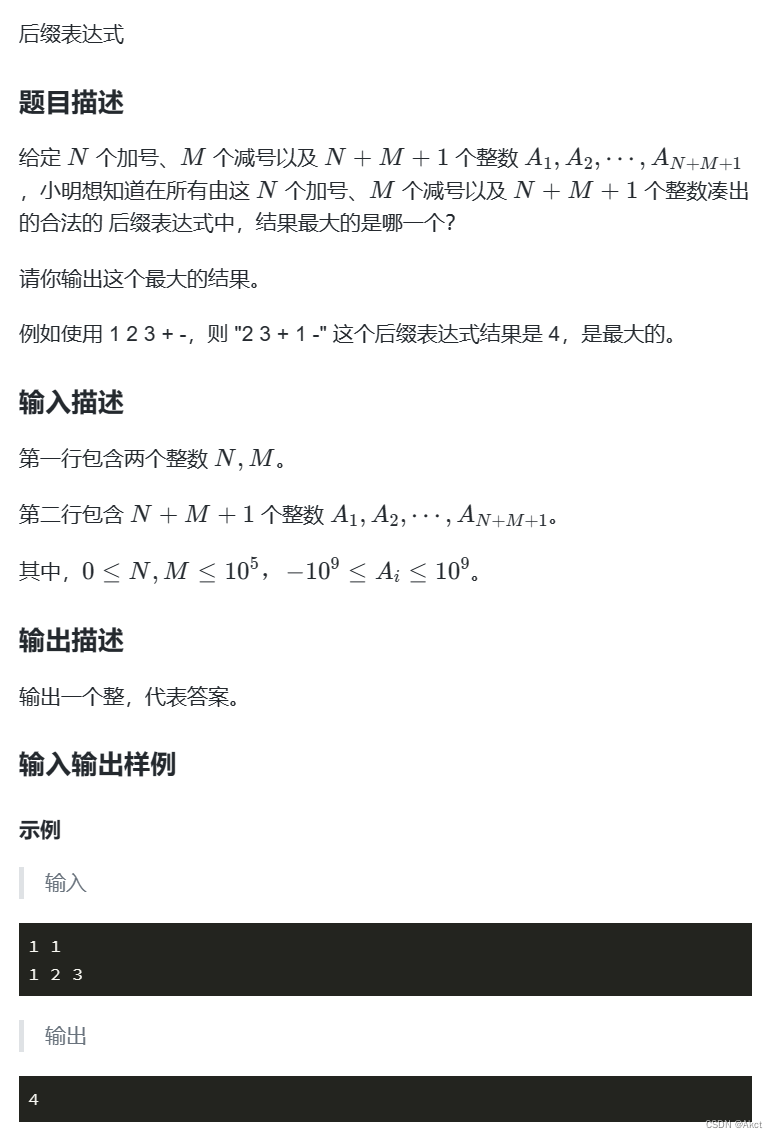

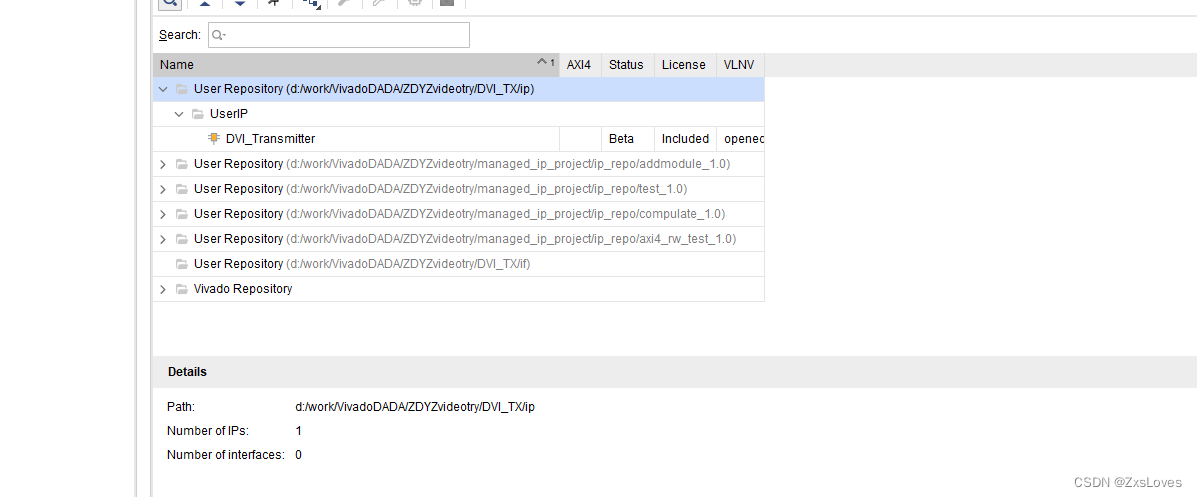

第一个 : 把指定目录 封装成IP核

先创建一个文件夹 然后带上 ip还有if ip是我们创建的ip if 是interface接口

ip里面创建一个 src的文件夹 在 src内部写下verilog文件

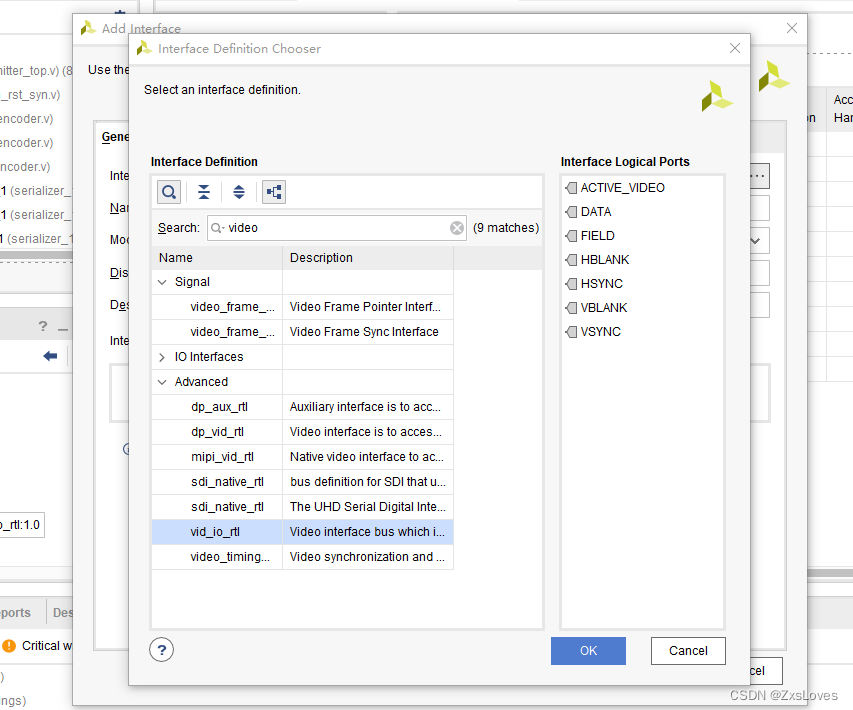

下面我们来研究一下如何对接口的封装

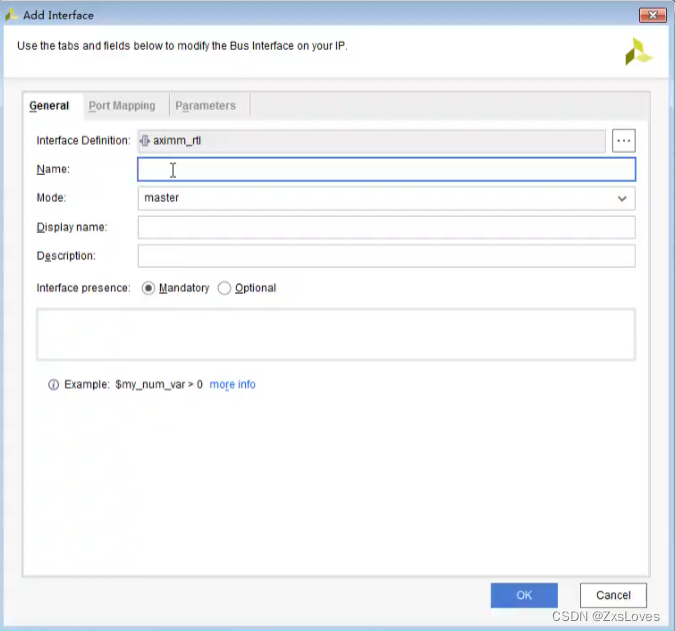

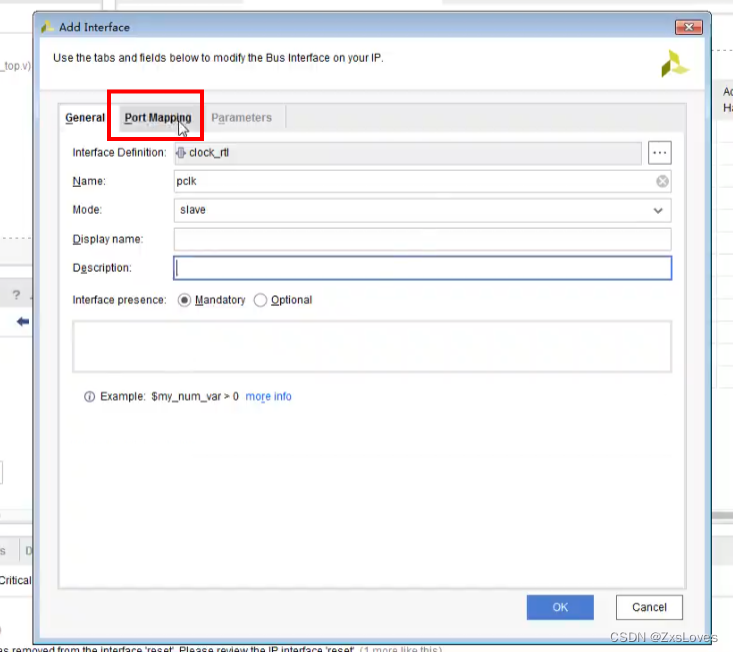

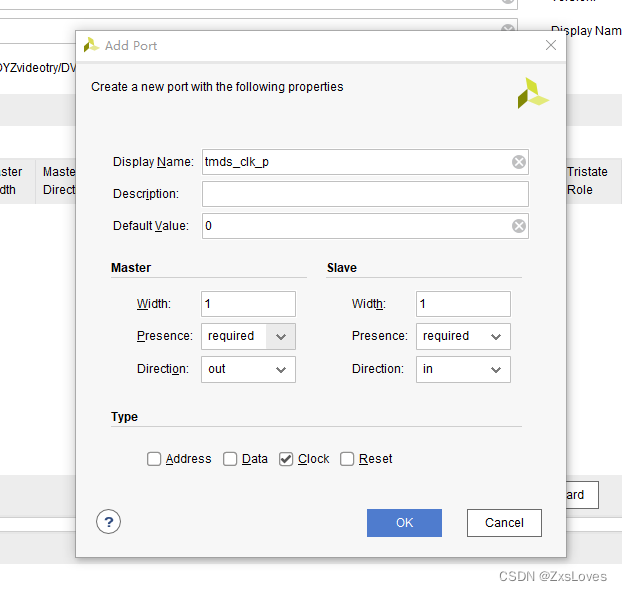

举例如 pclk 我们点击

第一行是对接口的定义 我们点击三个点 选择分类 点击clock

第三行 的那个 module 我们是选择输入的模式 作为 时钟信号 应该选择为 输入模式 毕竟是外界给这个点提供时钟的

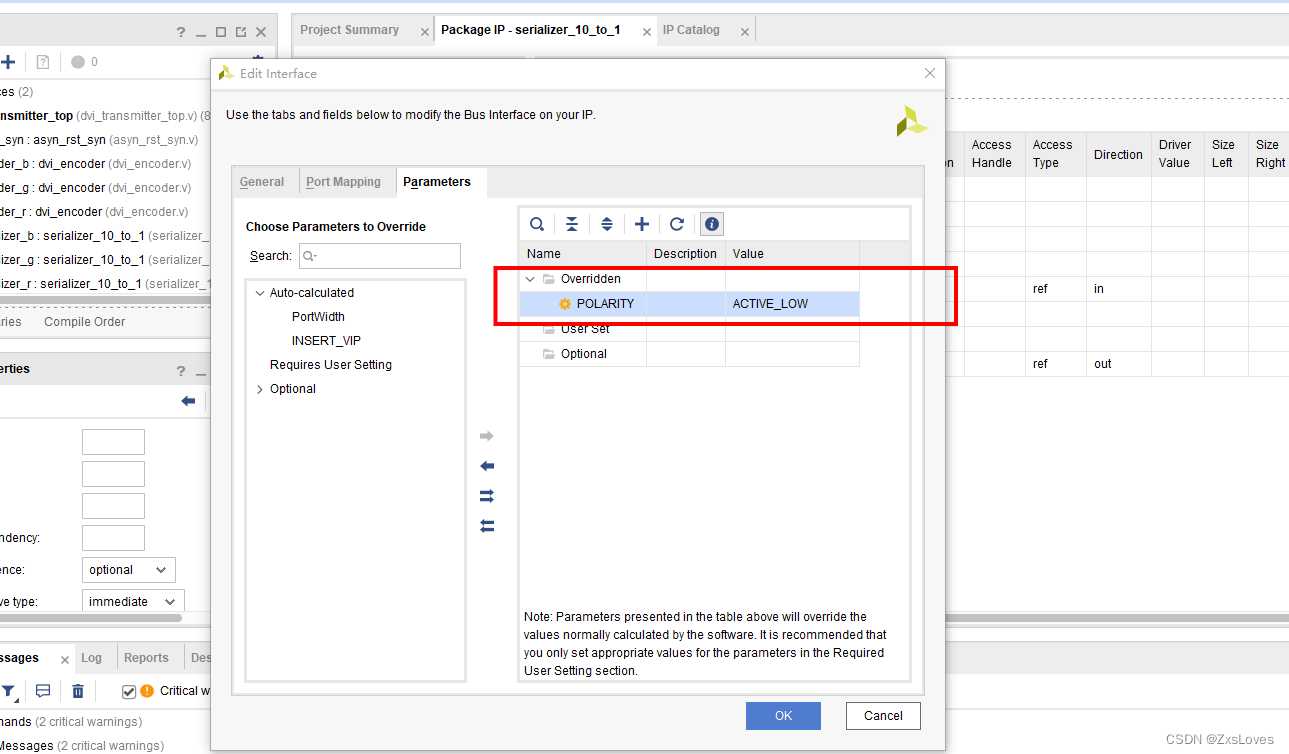

这个 port Mapping 是端口映射的意思

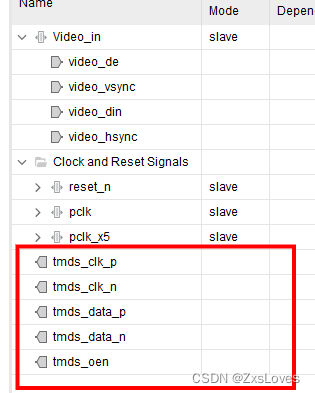

然后我们就可以看到 我们封装完成的 两个大的接口

我们现在还需要把这几个接口封装起来 上面的这几个 塞林斯 的官方是有接口提示的 但是 这个并没有 所以需要我们自己去定义

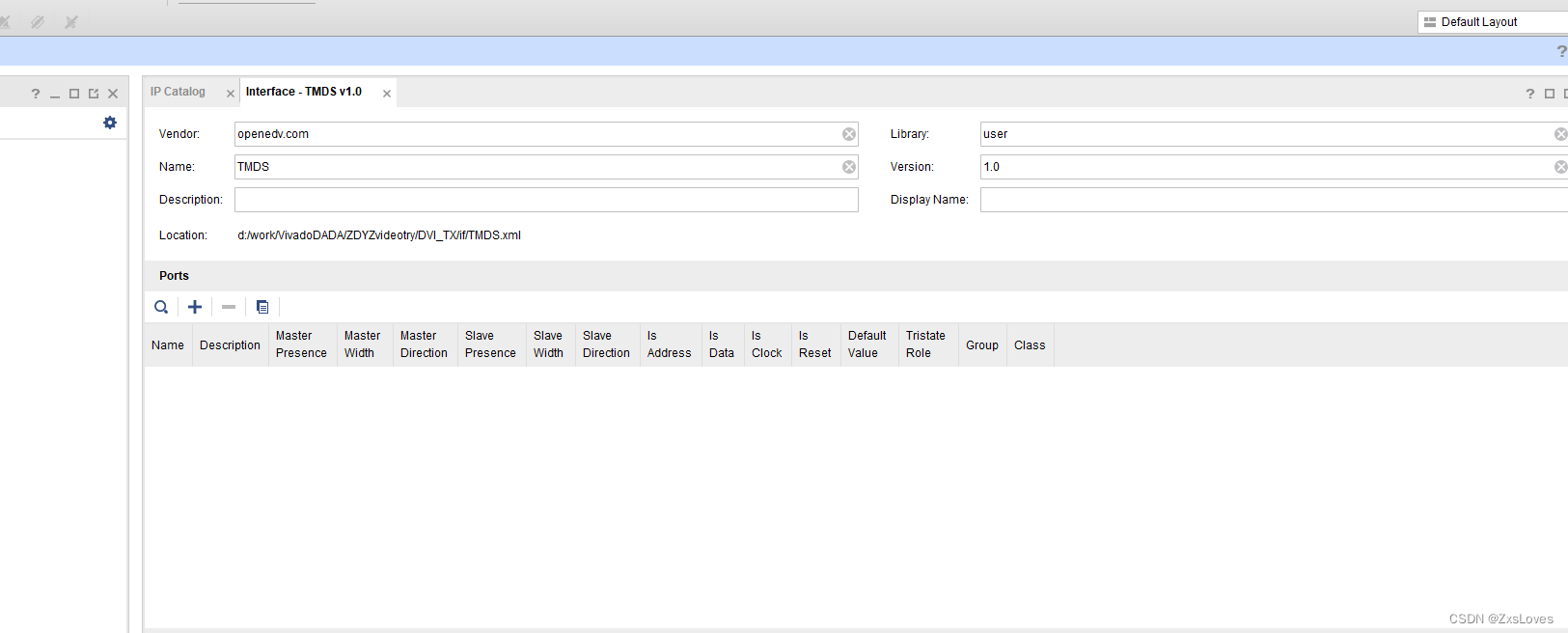

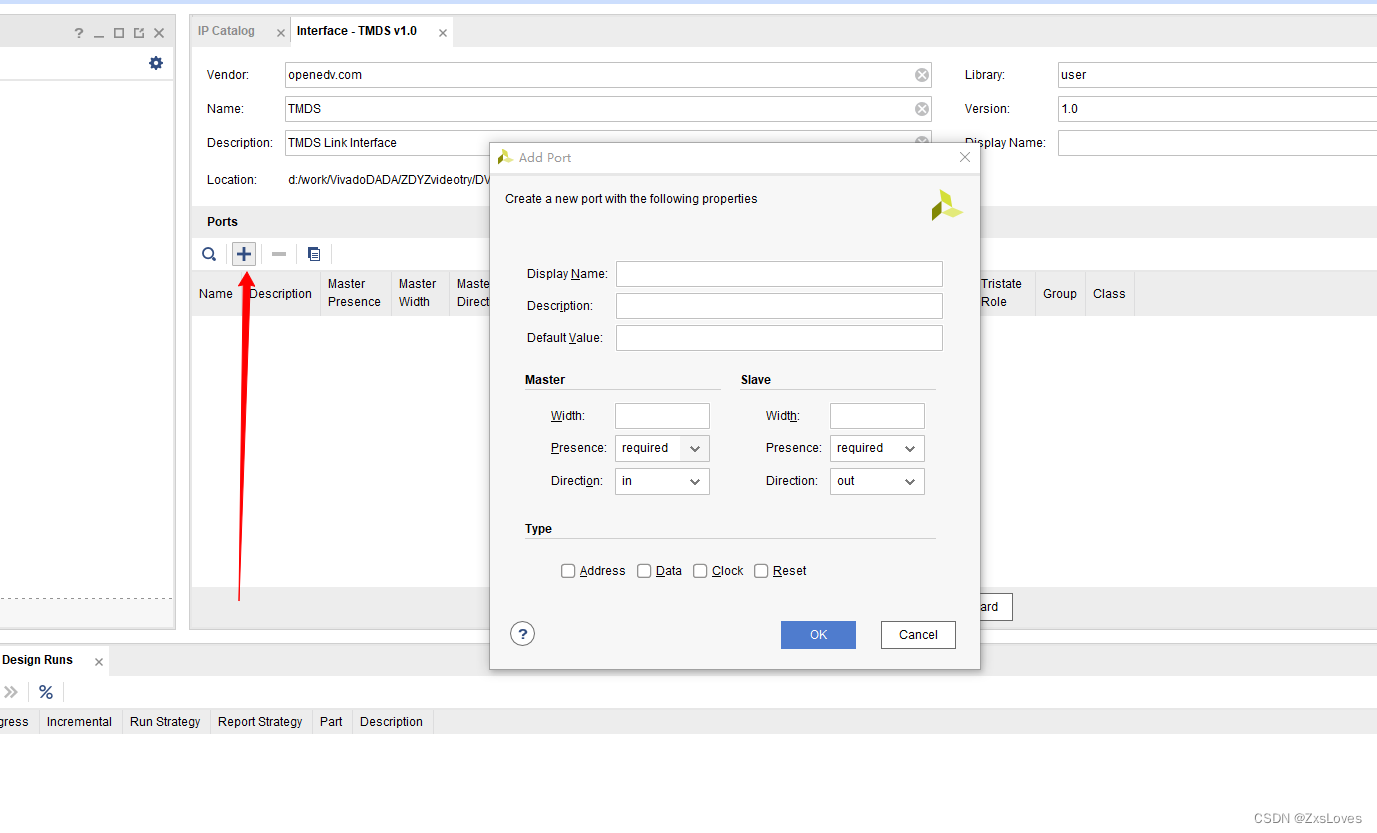

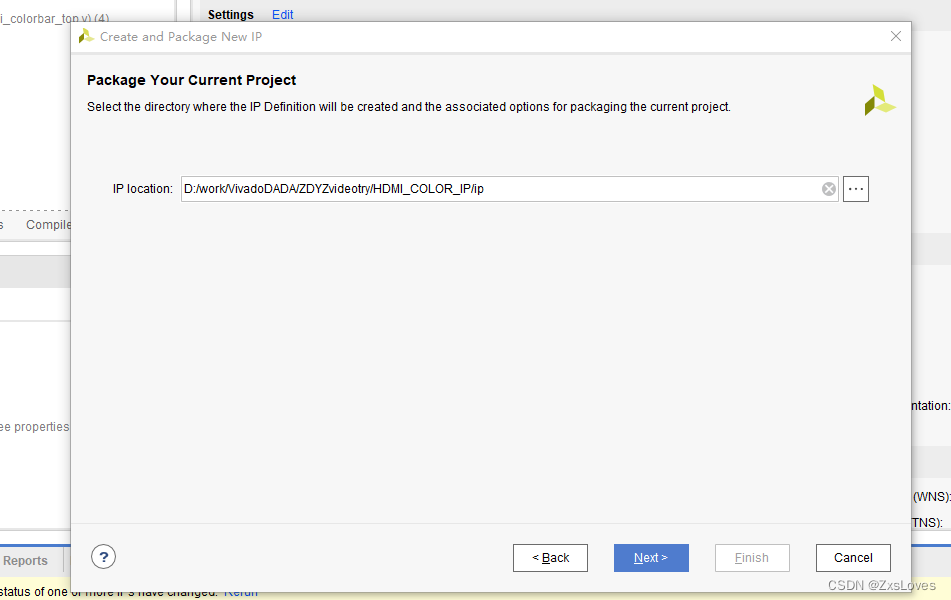

我们现在需要做的是 回到之前我们点击创立 IP核 的 界面 开始创立 一个接口定义

这个部分 最后指向我们的if文件夹

clock 如下图显示

在这里 相当于给了它一个注释 下次我们打开它 我们就能看到什么意思 了

这样就建设完IP了

完成实验配置

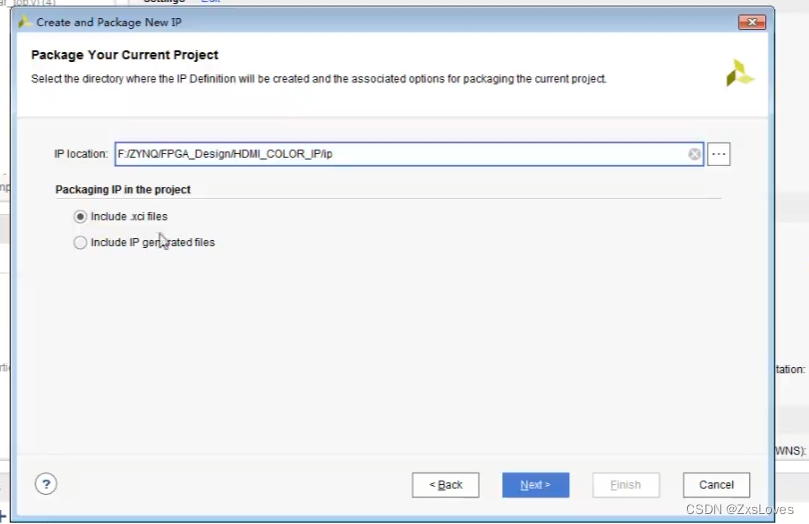

下面讲述 IP核封装之打包当前的工程为IP核

我们在打包 当前文件为IP核的时候 尽量选择 打包成.xci 文件 这样包含文件信息 可以 方便后续 更新升级 IP核

不过有一说一

我跟着正点原子的例程走 我在vivado 2019.1 并没有找到 .xci

但是视频显示的 是

打包完成打开

然后 先点击 接口 看一下 有没有把自定义接口加进去

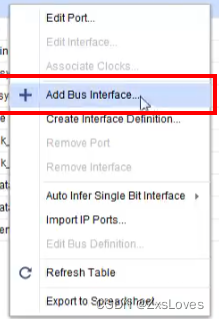

然后 点击 add interface 添加接口