👉个人主页:highman110

👉作者简介:一名硬件工程师,持续学习,不断记录,保持思考,输出干货内容

参考资料:《镁光SDRAM数据手册》、《PC SDRAM specification》

目录

写操作

WRITE Burst

Random WRITE

WRITE Terminated By WRITE

WRITE Terminated By READ

Write Terminated By Precharge

编辑Write Terminated By BURST TERMINATE

编辑Alternating Bank Write Accesses

编辑WRITE Continuous Page Burst

写操作

写和读总体类似,最大的区别是写没有CAS latency,写命令和输入数据是在同一个时钟沿生效。

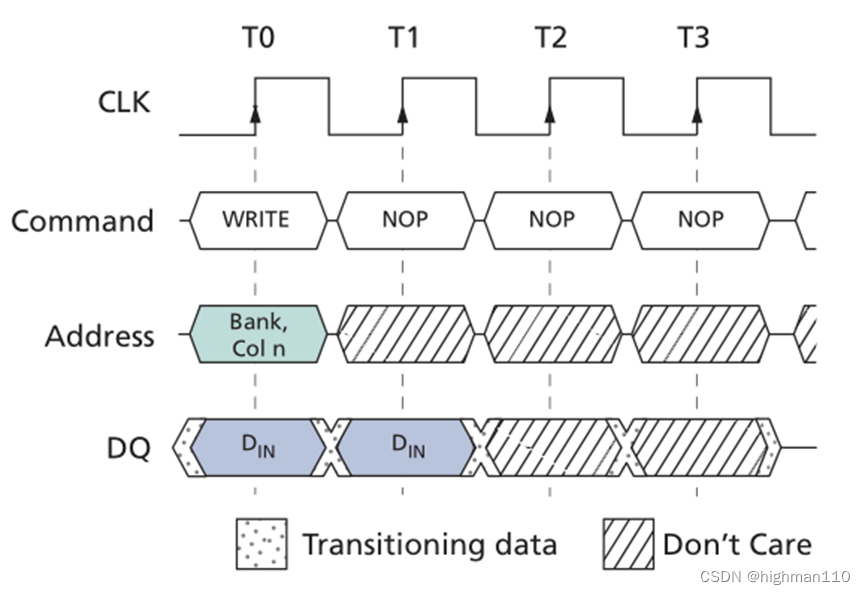

WRITE Burst

下图的BL=2。在完成固定长度突发时,假设没有其他命令,DQ将保持在高阻状态,并且任何额外的输入数据都将被忽略。

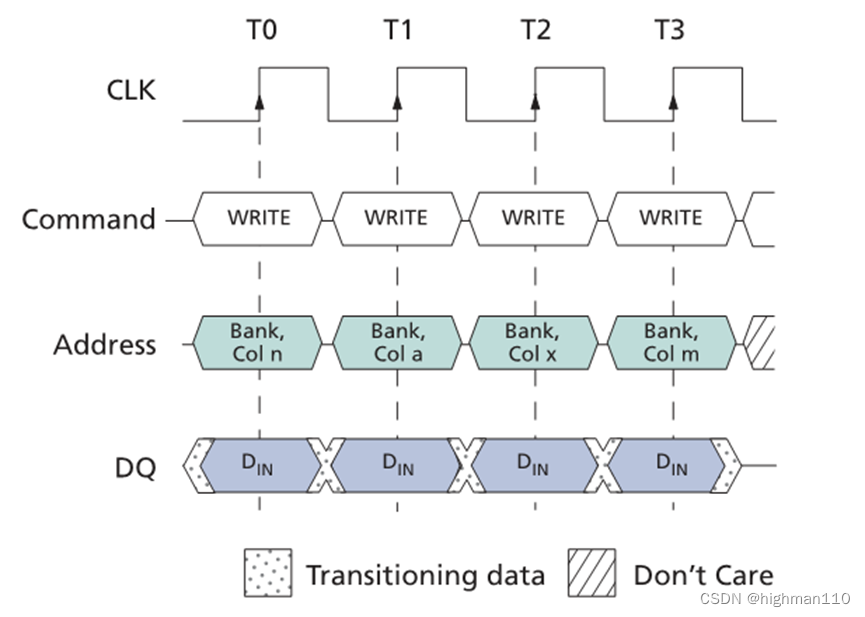

Random WRITE

发一个列地址写一次数据:

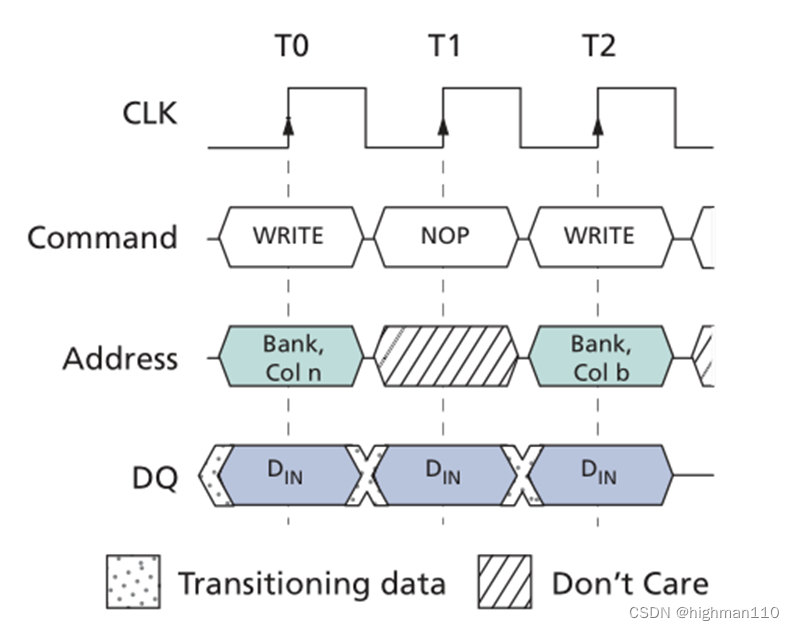

WRITE Terminated By WRITE

任何WRITE突发的数据都可以被后续的WRITE命令截断。新的WRITE命令和数据可以在前一个WRITE指令之后的任何时钟上发出。

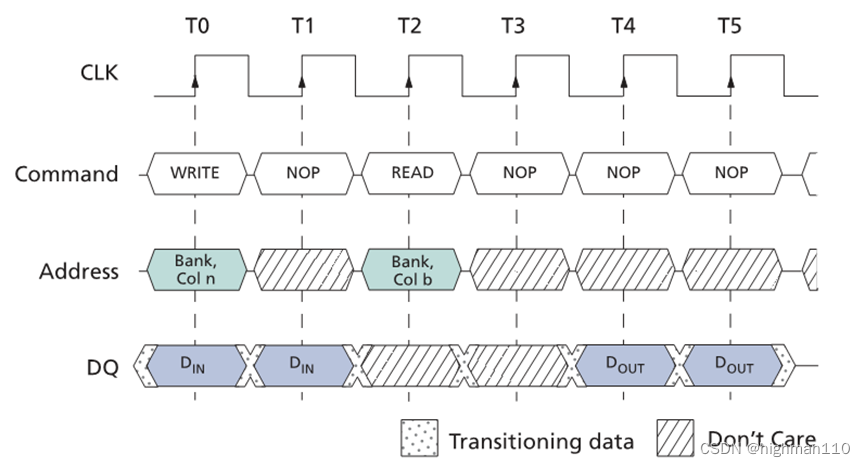

WRITE Terminated By READ

任何WRITE突发的数据都可以用后续的READ命令截断。注册READ命令后,将忽略数据输入,并且不会执行WRITE。

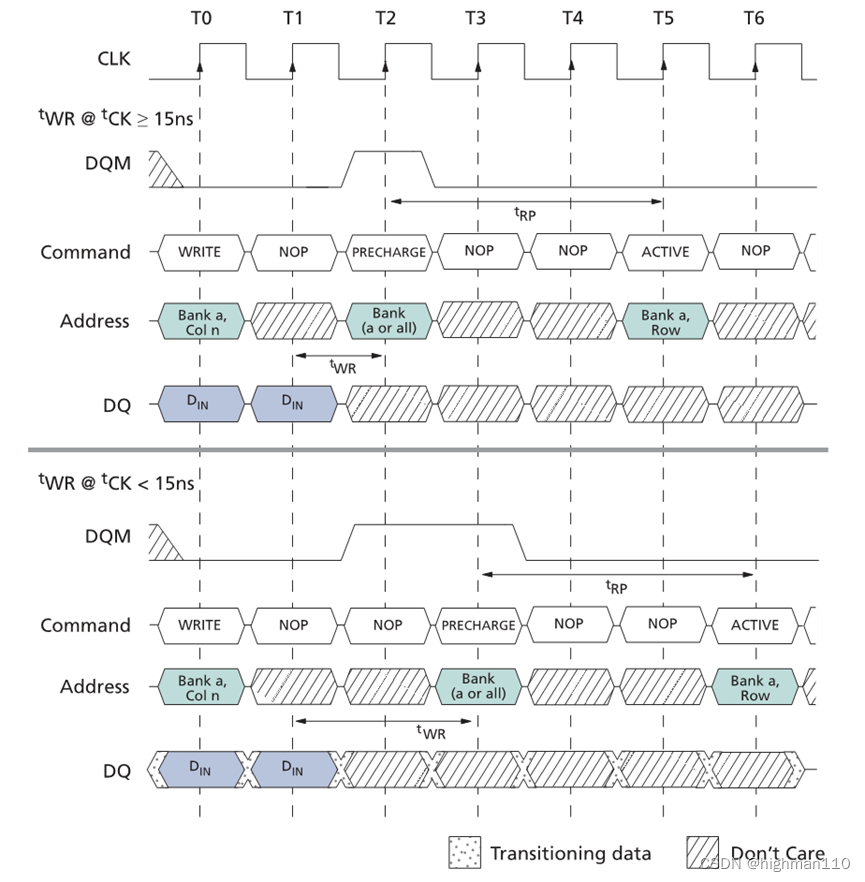

Write Terminated By Precharge

写操作同样可以被预充电命令截断,这里需要注意预充电命令的时机,一定要等所需要的最后一笔数据存储完毕才能进行预充电,这个从数据采样到完全存储是需要时间的,这个时间称为tWR,Write recovery time,这个时间单位为ns,当时钟频率越大时,一个tWR可能包含多个时钟周期,在这些时钟周期里,需要拉高DQM来屏蔽IO上的数据输入。

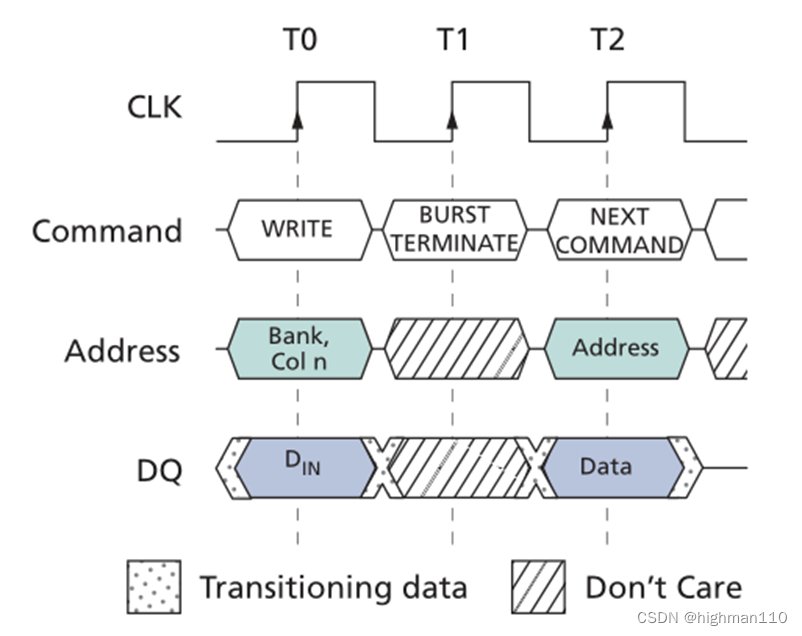

Write Terminated By BURST TERMINATE

Write Terminated By BURST TERMINATE

写突发也可以用BURST TERMINATE截断,如下图:

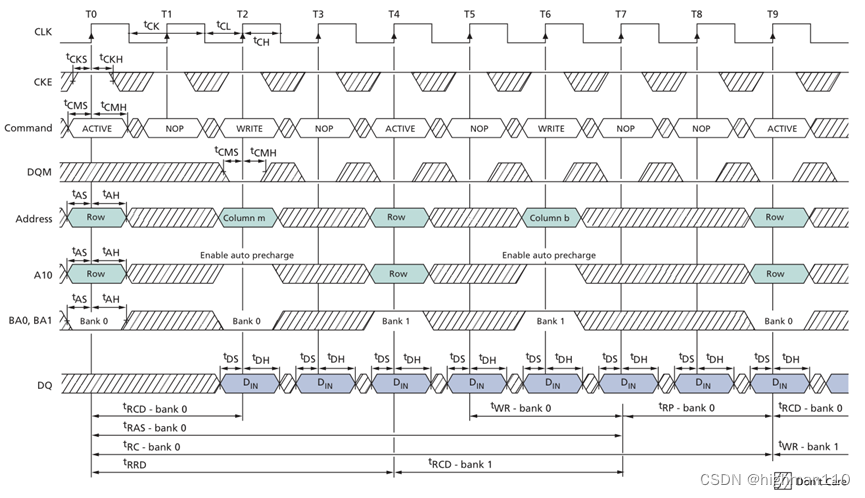

Alternating Bank Write Accesses

Alternating Bank Write Accesses

如下是带自动预充电的、BL=4的、Bank0和Bank1交错写操作的示意图。图中的时序参数之前都讲过了,这里就不重复了。

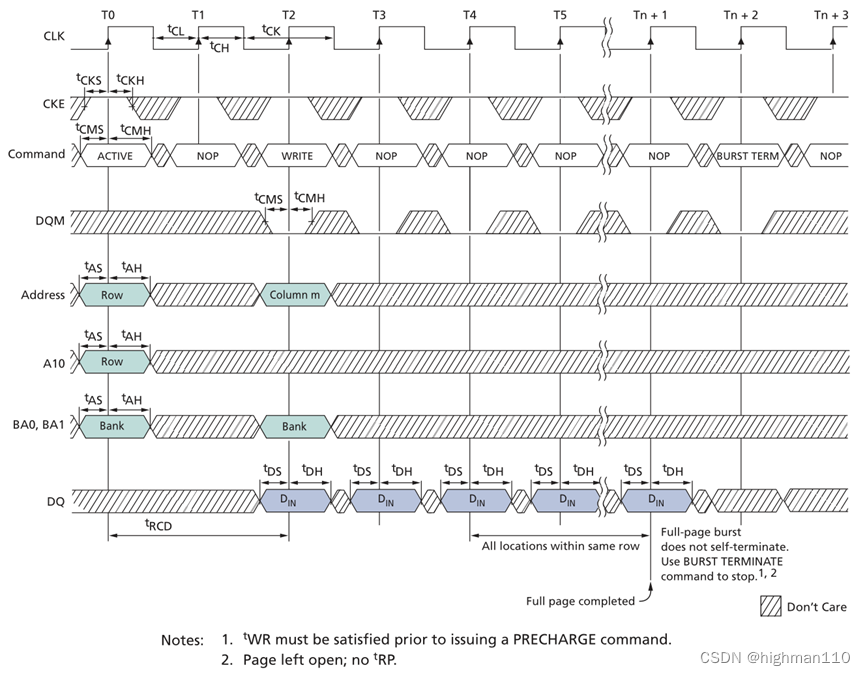

WRITE Continuous Page Burst

WRITE Continuous Page Burst

连续页突发写,可以被burst terminate命令截断。

OK,SDRAM就先介绍到这里,相信看完这几篇对SDRAM能有一个比较清晰的认识,有了这个基础,后面再学习一代代的DDR会更容易。

![[PyTorch][chapter 57][WGAN-GP 代码实现]](https://img-blog.csdnimg.cn/1a227a6496cf4e3fb077aa12551839c9.png)

![[C++基础]-多态](https://img-blog.csdnimg.cn/8daed871137246219ff7dfe3c58fb5a3.png)