原创 硬件设计技术 硬件设计技术 2023-07-20 00:04 发表于广东

收录于合集#集成电路--IC7个

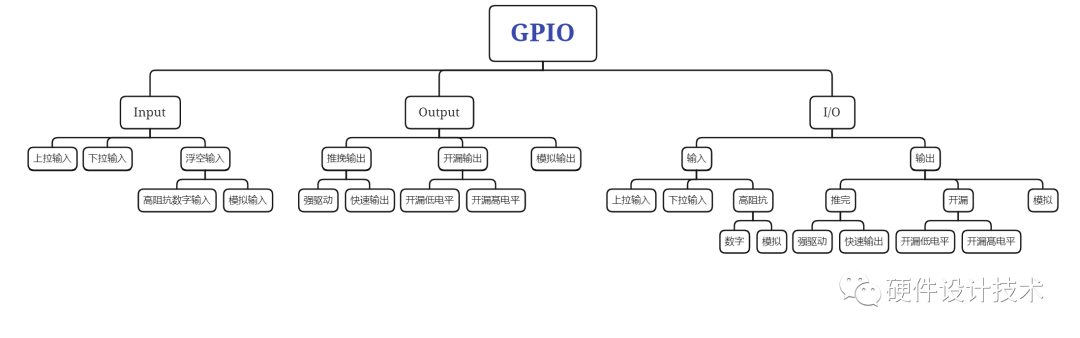

一、GPIO定义、分类:

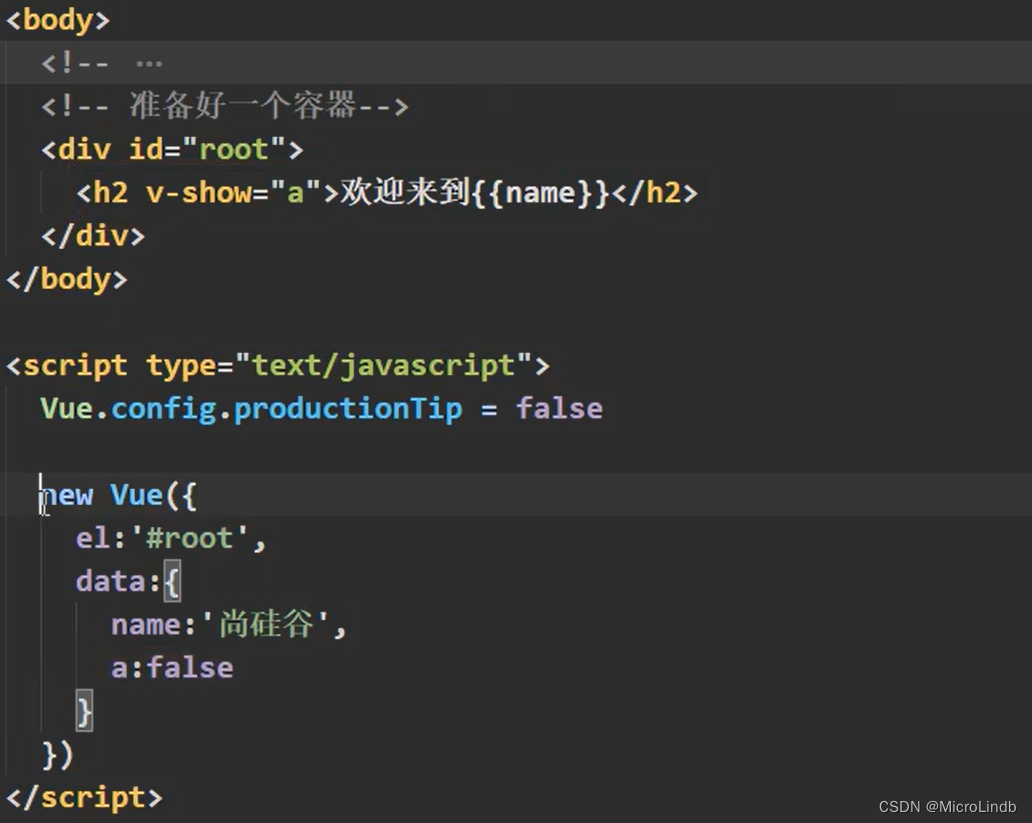

GPIO(英语:General-purpose input/output),通用型之输入输出的简称,其接脚可以供使用者由程控自由使用,PIN脚依现实考量可作为通用输入(GPI)或通用输出(GPO)或通用输入与输出(GPIO。

分类如下:

二、GPIO内部结构:

既然一个引脚可以用于输入、输出、其他特殊功能,那么一定有寄存器用来选择这些功能。对于输入:可以通过读取某个寄存器来确定引脚电位的高低;对于输出:可以通过写入某个寄存器来让这个引脚输出高电位或者低电位;对于其他特殊功能:另外的寄存器来控制它们。

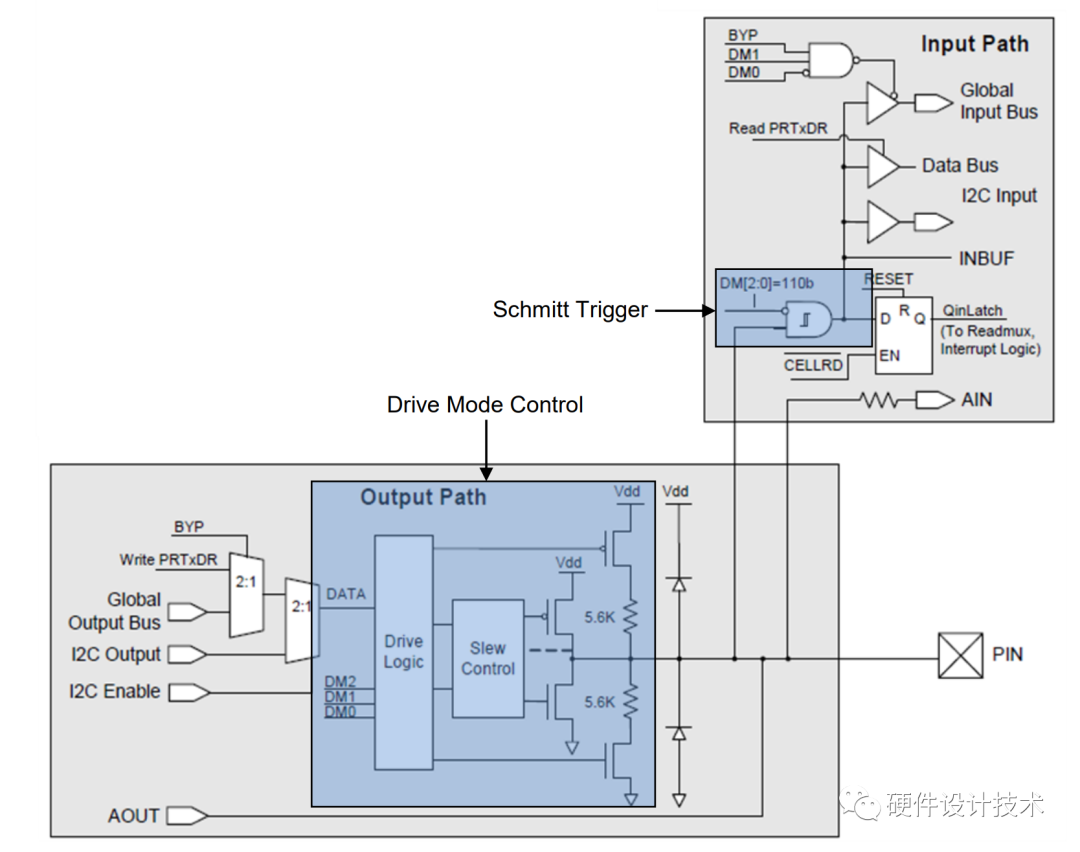

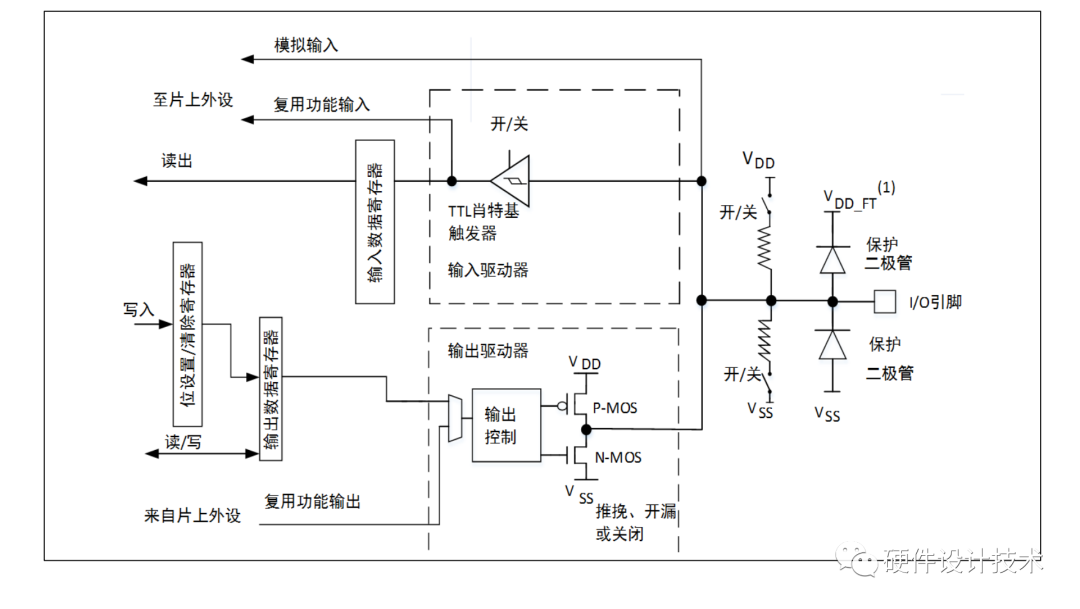

内部简易系统框图如下所示:

简易等效图一、<From cypress or infineon>

简易等效图二、<From ST>

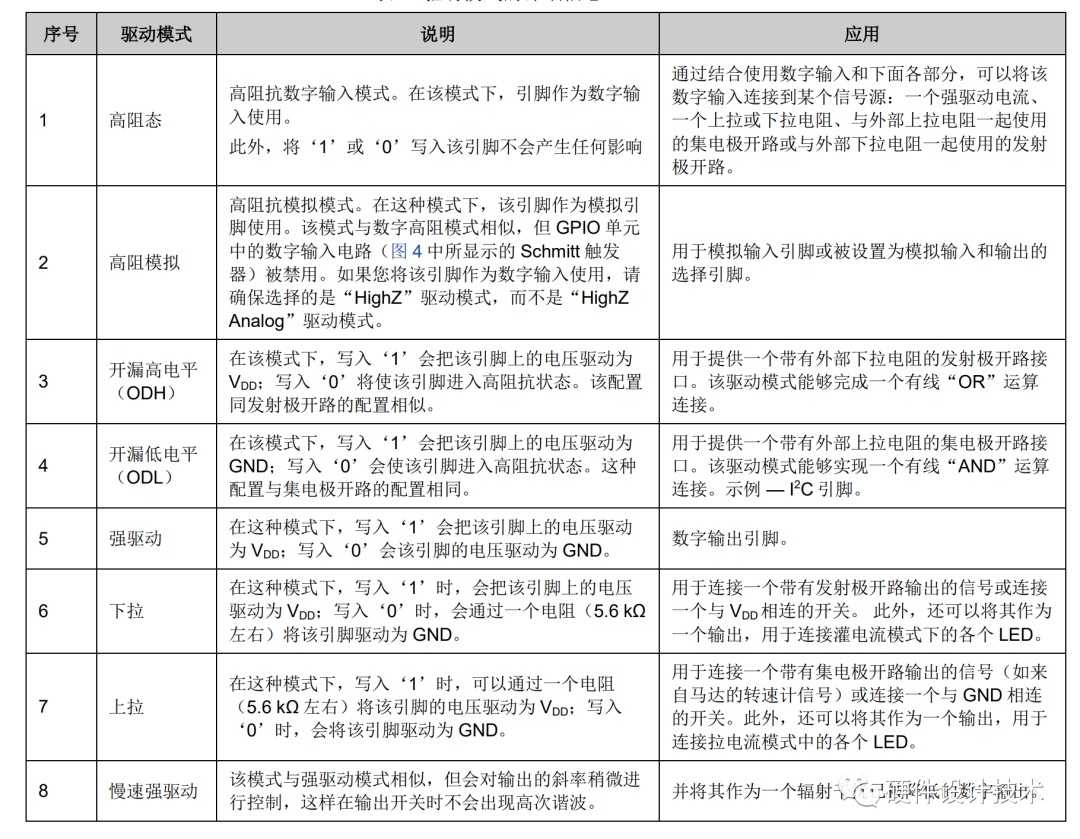

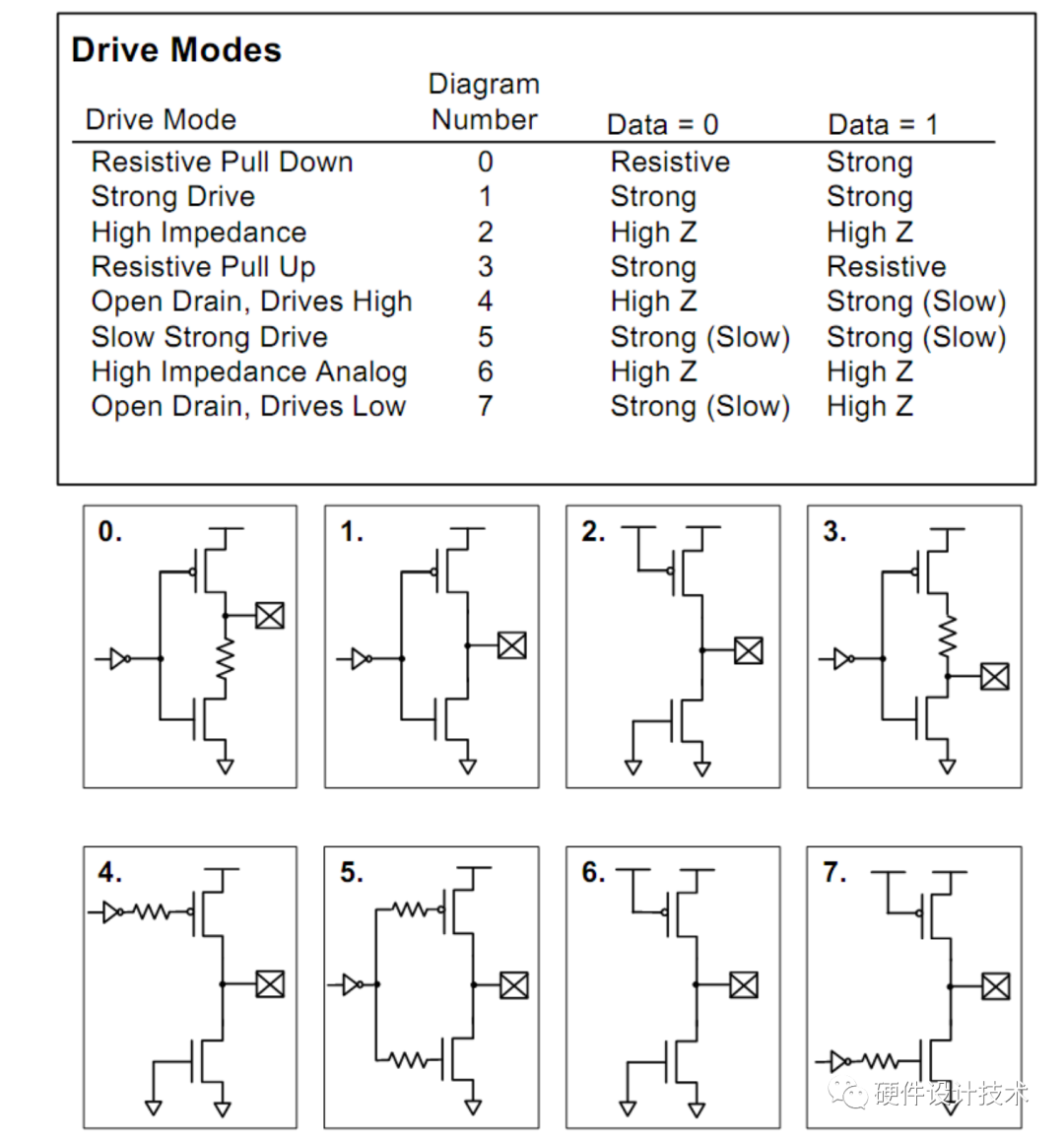

三、GPIO驱动模式诠释以及等效模型:

下图提供了某个 GPIO 引脚八种驱动模式,同时给出了每一种驱动模式下的 GPIO 单元配置等效电路模型。<From cypress or infineon>

3.1、输入模式配置:

3.1.1、当器件I/O引脚配置为输入时,必须选择以下三个选项之一:

• 带内部上拉的输出。使用上拉电阻,以确保在浮动输入信号的情况下具有良好定义的逻辑电平。根据应用要求,也可以使用外部上拉电阻。

• 带内部下拉的输入。使用下拉电阻,确保在浮动输入信号的情况下具有

良好定义的逻辑电平。根据应用要求,也可以使用外部下拉。

• 悬空输入。信号电平跟随外部信号。当没有外部信号时,施密特触发器在由外部噪声引起的逻辑电平之间随机切换。但同时这也增加了总体消耗。

3.1.2、编程为输入时,I/O端口具有以下特征:

• 输出缓冲器被关闭

• 施密特触发器输入被打开

• 根据GPIOx_PUPDR寄存器中的值决定是否激活上拉或下拉电阻

• 输入数据寄存器每隔 1 个 AHB 时钟周期对 I/O 引脚上的数据进行一次采样

• 通过读取GPIOx_IDR输入数据寄存器可获取I/O状态

3.2、输出模式配置:

3.2.1、当器件I/O引脚配置为输出时,必须选择以下两个选项之一:

• 推挽输出模式:

推挽输出实际上使用两个晶体管:一个PMOS和一个NMOS。每个晶体管接通才能将输出

驱动到适当的电平:

– 当输出必须驱动为高电平状态时,顶部晶体管(PMOS)导通

– 当输出必须驱动为低电平状态时,底部晶体管(NMOS)导通

两个晶体管的控制通过GPIO端口输出类型寄存器(GPIOx_OTYPER)完成。将输出寄存器(GPIOx_ODR)的相关位写0可激活NMOS晶体管,强制I/O引脚接 地。

将输出寄存器(GPIOx_ODR)的相关位写1可激活PMOS晶体管,强制I/O引脚接 通VDD。

• 开漏输出模式:

开漏输出模式不使用PMOS晶体管,而是需要一个上拉电阻。

当输出必须变为高电平时,必须关闭NMOS晶体管,仅通过上拉电阻将电平拉高。该上拉电阻可以是内部的,也可使用外部的。

注意:不可能在同一个I/O引脚上同时激活上拉和下拉。用户也可以使用外部上拉或下拉电阻代替内部电阻。在这种情况下,必须调整该值以符 合GPIO输出电压和电流特性。

3.2.2、编程为输出时,I/O端口具有以下特征:

• 可将输出缓冲器配置为开漏或推挽模式

• 施密特触发器输入被打开

• 根据GPIOx_PUPDR寄存器中的值决定是否激活上拉或下拉电阻。

• 写入输出数据寄存器GPIOx_ODR的值将I/O引脚状态置位

• GPIOx_ODR中的写入数据可从GPIOx_IDR中读取,该寄存器每个AHB时钟周期更新一次

开漏输出通常用于控制供电电压与主控电平不同的器件。需要特定上拉电阻时,开漏模式也用于驱动一个或多个I2C器件。

3.3、模拟配置:

有一些 GPIO引脚可以配置为模拟模式,允许使用ADC、DAC、PAMP和COMP等内部外设。要在模拟模式下使用GPIO引脚,请考虑以下寄存器:

•GPIOx_MODER,选择模式(输入,输出,复用,模拟)

•GPIOx_ASCR,选择所需的功能,ADC,DAC,OPAMP或COMP

对 I/O 端口进行编程作为模拟配置时:

• 输出缓冲器被关闭

• 施密特触发器输入被禁用,因此I/O引脚的每个模拟值零消耗。施密特触发器的输出被强制为恒定值(0)。

• 上拉和下拉电阻被硬件关闭,对输入数据寄存器的读访问值为“0”。

本次关于SOC的GPIO学习分享,到此结束。感谢各位朋友的时间!同时预留以下几个思考题:

1、不同器件之间的GPIO链接为什么需要电平一致呢?

2、既然GPIO允许被配置为开漏输出。那么是否可以直接使用开漏功能实现不同电平之间转换呢?比如:3V-1.8V