参考来源:

逻辑制程 - 台湾积体电路制造股份有限公司 (tsmc.com)

1、 TSMC逻辑制程发展路线图

2、从65nm到3nm制程技术发展的简介

2.1 65nm 制程

Y2005:成功试产65nm晶片;

Y2006:成功通过65nm制程技术的产品验证,推出了低耗电量(Low Power,LP)制程技术;

推出65nm的泛用型(General Purpose,GP)制程;

提升:TSMC 65nm是第三代同时采用铜制程及低介电质技术,与前一世代的90nm制程技术相比,65nm制程技术的标准元件密度增为两倍。具备更高的整合性、更好的晶片效能,病拥有电源管理技术,能大幅降低耗电量。

2.2 40nm 制程

Y2008:40nm 量产;

提升:TSMC 40nm 泛用型(GP)及40nm 低耗电(LP)制程的晶片闸密度(Raw gate density)最多可达65nm制程技术的2.35倍。与65nm GP制程技术相较,在相同的漏电流水准下,40nm GP制程技术的效能增加幅度可达40%;在相同的运转速度情况下,其操作功耗减少幅度则可达50%。此外,与65nm LP制程相较,在相同的运转速度情况下,40nm LP制程技术的漏电流减少幅度可达51%,操作功耗减少幅度可达51%。

除上述制程外,还推出了40nm低耗电强效版(LP+)以及40nm超低耗电(ULP)等制程。与40nm LP制程相较, 40nm LP+制程的效能增加幅度可达30%;40nm ULP的漏电流减少幅度可达70%,操作功耗减少幅度可达30%。

应用:40nm GP制程技术适用于高效能的产品应用,例如中央处理器、绘图处理器、游戏机、网路、场域可程式化逻辑闸阵列(FPGA)以及硬碟驱动晶片等产品应用;40nm LP及40nm LP+制程则适用于智慧型手机、数位电视(DTV)、机上盒(STB)、游戏晶片及无线网路连接产品等应用;40nm ULP制程适用于物联网及穿戴式装置相关产品应用。

2.3 28nm 制程

Y2011:推出28nm GP制程技术。

提升:28nm 制程技术以采用高介电层/金属闸极(High-k Metal Gate,HKMG)的后闸极(Gate-last)技术为主。相较于前闸极(Gate-first)技术,后闸极技术具备较低的漏电流以及能提供更佳的晶片效能等优势。

应用:具备高效能、低功耗等优势,并与TSMC 28nm 的设计生态环境无缝接轨,以协助客户加速产品上市时间,能够支援客户包括中央处理器、图像处理器、高速网路晶片、智慧型手机、应用处理器(AP)、平板电脑、家庭娱乐、数位消费性电子产品、车用装置及物联网等产品应用。

2.4 22nm 制程

Y2018 Q4:完成验证。

提升:与28nm 高效能精简型制程技术(28nm High Performance Compact,28HPC)相较,22ULP技术拥有晶片面积缩小10%,及效能提升超过30%或功耗降低超过30%的优势,以满足影像处理器、数位电视、机上盒、智慧型手机及消费性产品等应用。

22nm 超低漏电制程技术(22nm Ultra-Low Leakage, 22ULL)已顺利完成开发并于2018年第四季按计划开始试产,能够支援物联网及穿戴式装置相关产品应用。与40nm ULP及55nm ULP制程相较,新的ULL元件和ULL静态随机存取记忆体(Static Random Access Memory, SRAM)可以大幅降低功耗。

2.5 16/12 nm 制程

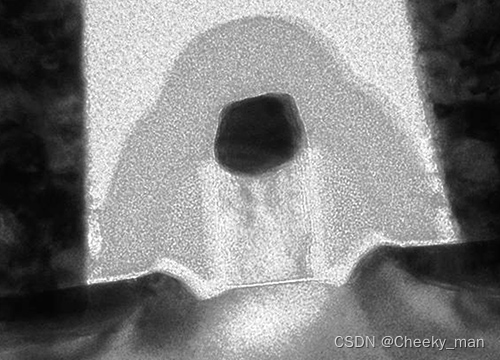

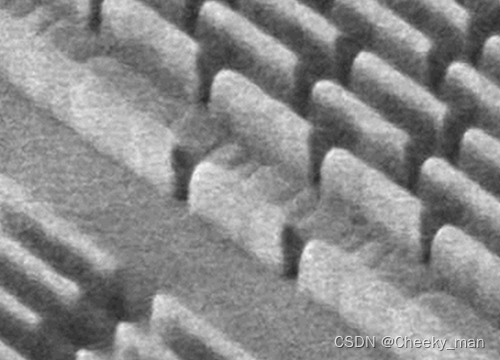

Y2013M11:成功试产16nm FinFET(Fin Field Effect Transistor,鳍式场效应晶体管)制程技术。

Y2014:16nm 量产。

Y2015M7:16nm FinFET强效版制程(16FF+)量产。

Y2016Q1:更具成本效益的16nm 精简型制程技术(16nm FinFET Compact Technology,16FFC)量产。

Y2017Q2:进一步提升晶体密度的12nm 精简型制程技术(12nm FinFET Compact Technology,12FFC)进入生产。

提升和应用:16/12nm 速度增快 50% ,在相同速度下功耗降低60%,能够协助客户达到最佳效能与功耗,成功支援下一世代高阶行动运算、网路通讯、消费性产品以及车用电子产品的应用。

2.6 7nm 制程

Y2016M6:成功产出良率达2位数的256Mb的SRAM。

Y2017M4:试产。

Y2018M8:第二代7nm (N7+)开始试产,是业界第一个商用EUV制程技术。

Y2020Q1:预计试产6nm(N6)制程技术。

提升:相较于10nm FinFET制程技术,7nm FinFET制程技术在逻辑闸密度(Logic Density)提高1.6倍,速度增快约20%,功耗降低约40%。

应用:支援多样化的产品应用,包括高阶到中阶行动产品、消费性应用、人工智慧、网通、5G基础架构、绘图处理器、以及高效能运算。

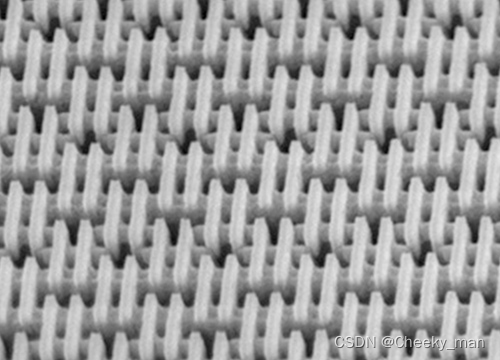

2.7 5nm 制程

Y2020Q2:成功量产5nm(N5)鳍式场效应晶体管。

提升:相较于7奈米(N7)技术,N5技术速度增快约20%,或者功耗降低约40%。

Y2022:预推出N5的强化版--4nm(N4)技术。

2.8 3nm 制程

Y2022H2:预量产3nm (N3)。

提升:相较于N5制程技术,N3制程技术的逻辑密度将增加约70%,在相同功耗下速度提升10-15%,或者在相同速度下功耗降低25-30%。

![[学习笔记]PageRank算法](https://img-blog.csdnimg.cn/48de627f51ec460f8aa932c198d22b72.png)