文章目录

- 前言

- 一、异步FIFO仿真过程

- 1、异步FIFO设计

- 2、UVM验证

- 二、脚本文件编写

- 三、编译错误

前言

2022.11.15 记录自己开始使用UVM仿真异步FIFO项目

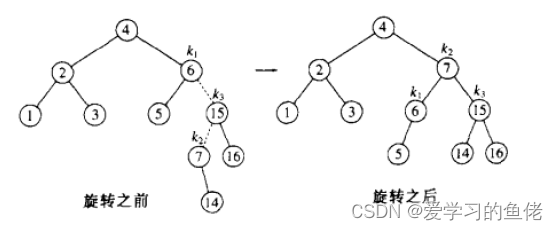

一、异步FIFO仿真过程

1、异步FIFO设计

首先对编写的异步FIFO设计代码进行验证,写了一个test.v文件

(1)设置读写时钟相同

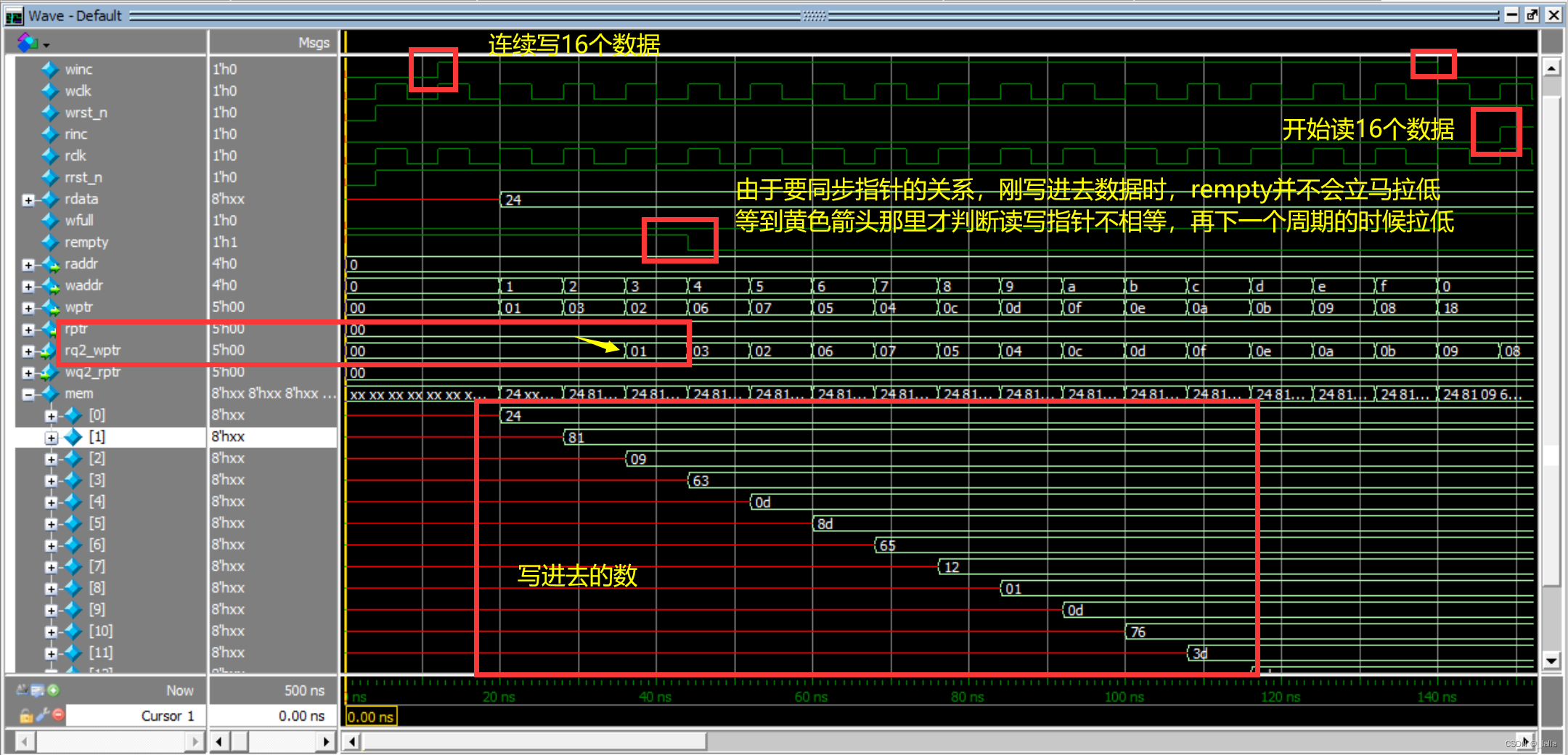

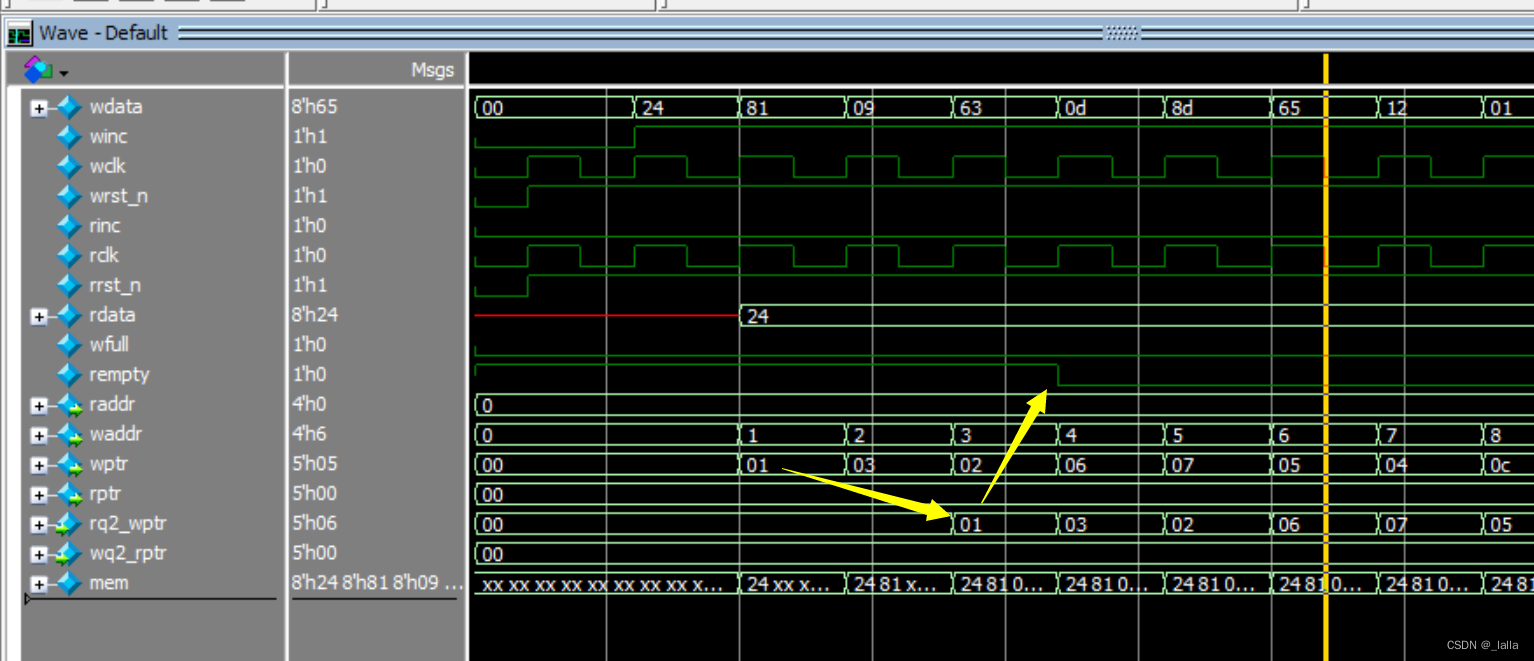

- 先连续写16个数,再连续把16个数读出来

把写指针同步到读时钟域需要两个周期,当读写指针不相同时,下一个周期拉低

产生了“虚空”现象

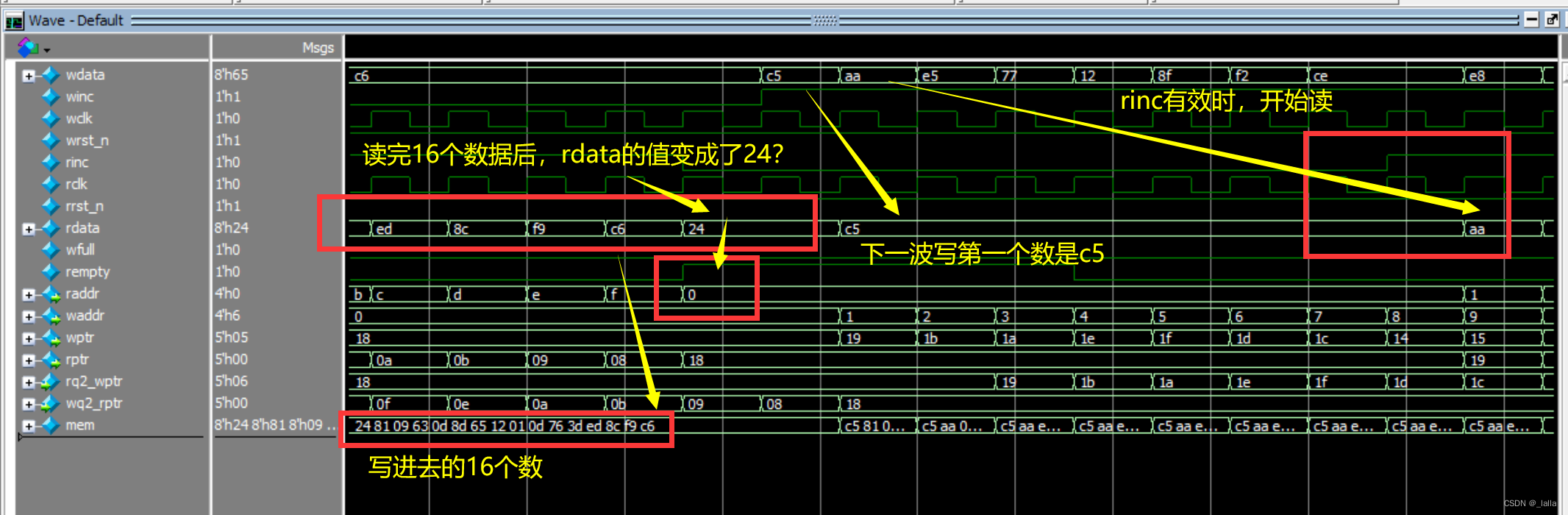

因为读完之后,读指针又回到了0的位置,而0位置处的值就是24。

当又开始写时,0位置处值为c5

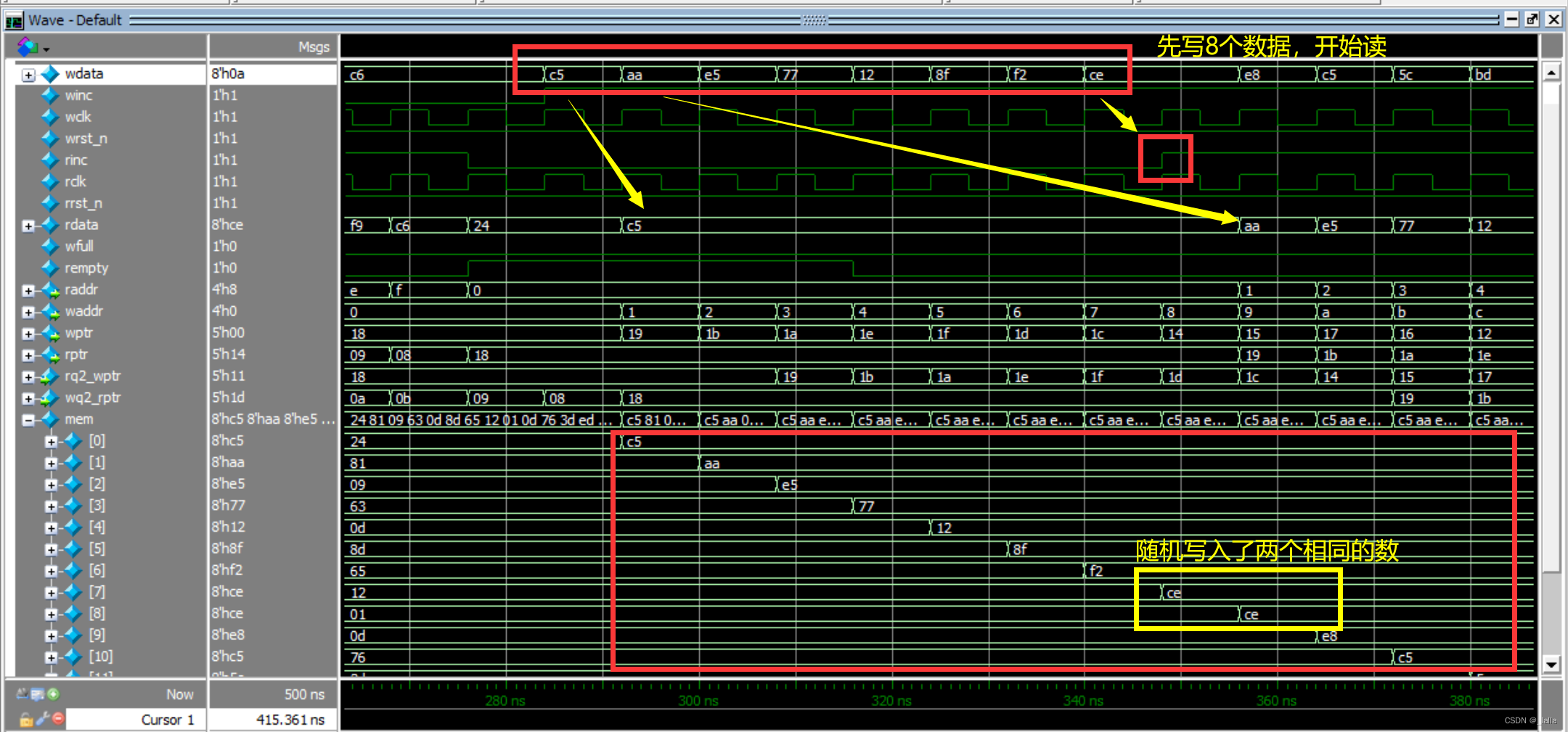

- 先写8个数据进去,开始读,然后边写边读

(2)写快读慢

同样数据是正确的

2、UVM验证

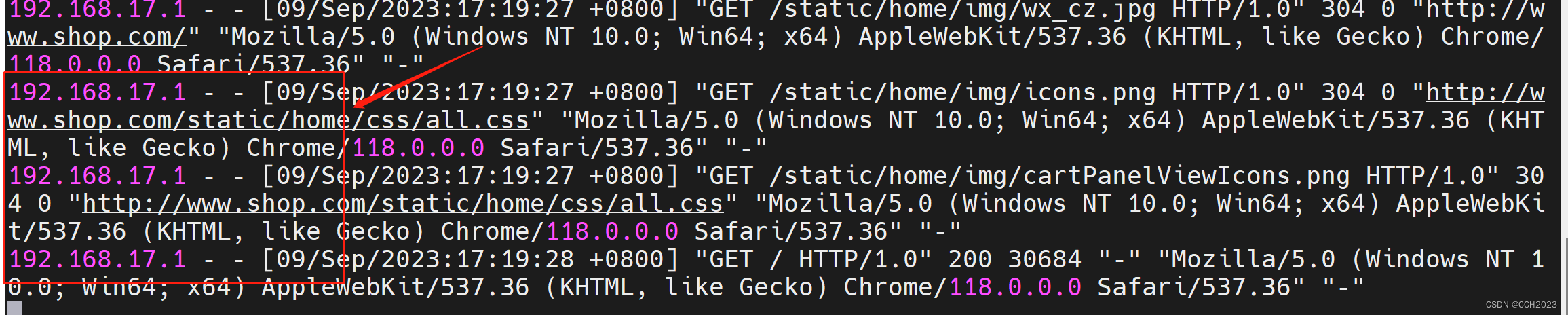

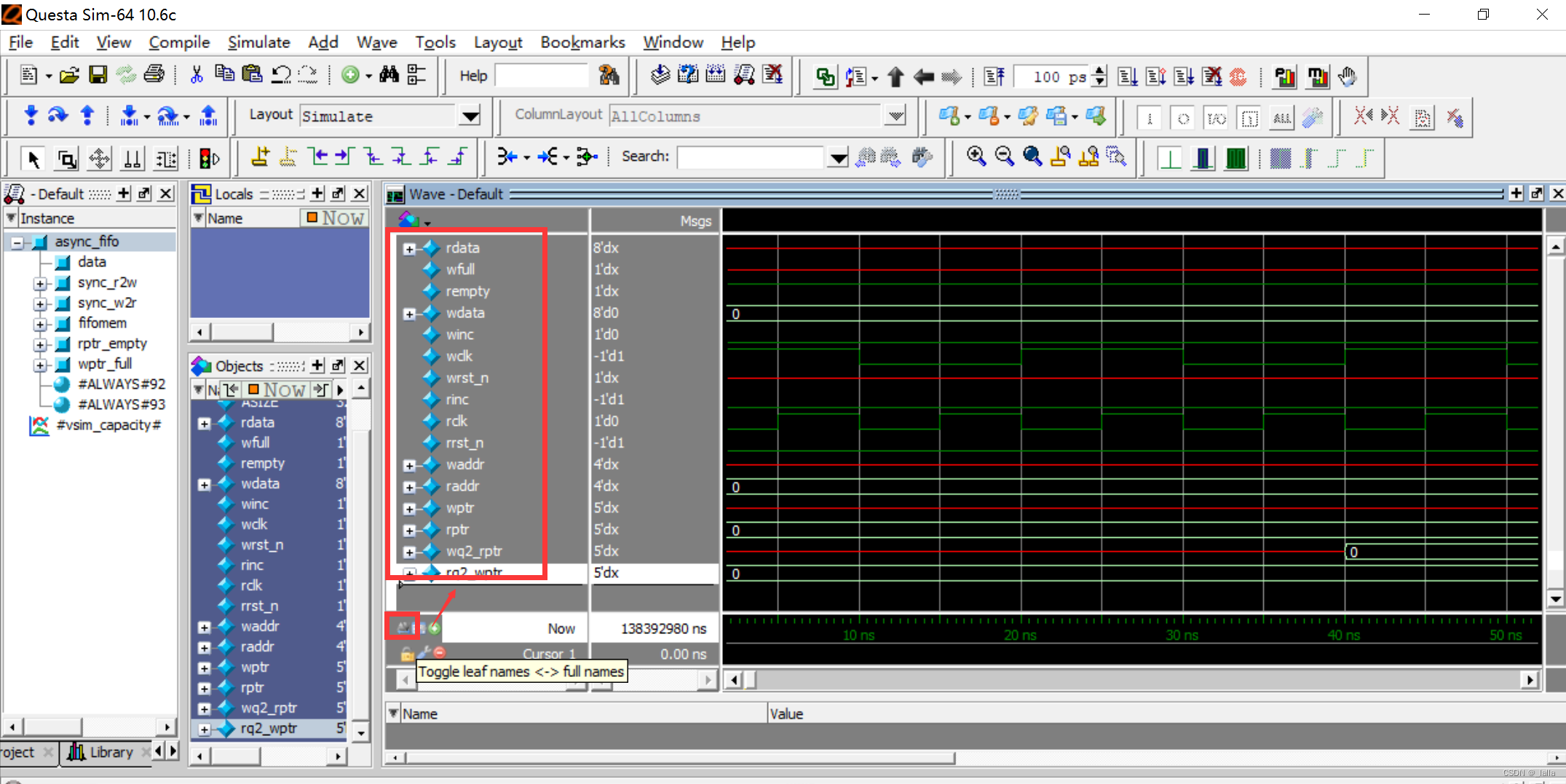

仿真之前先输入log -r /*,可以确保TB层次下所有信号都可以保存到数据库以供查看任何信号的波形。

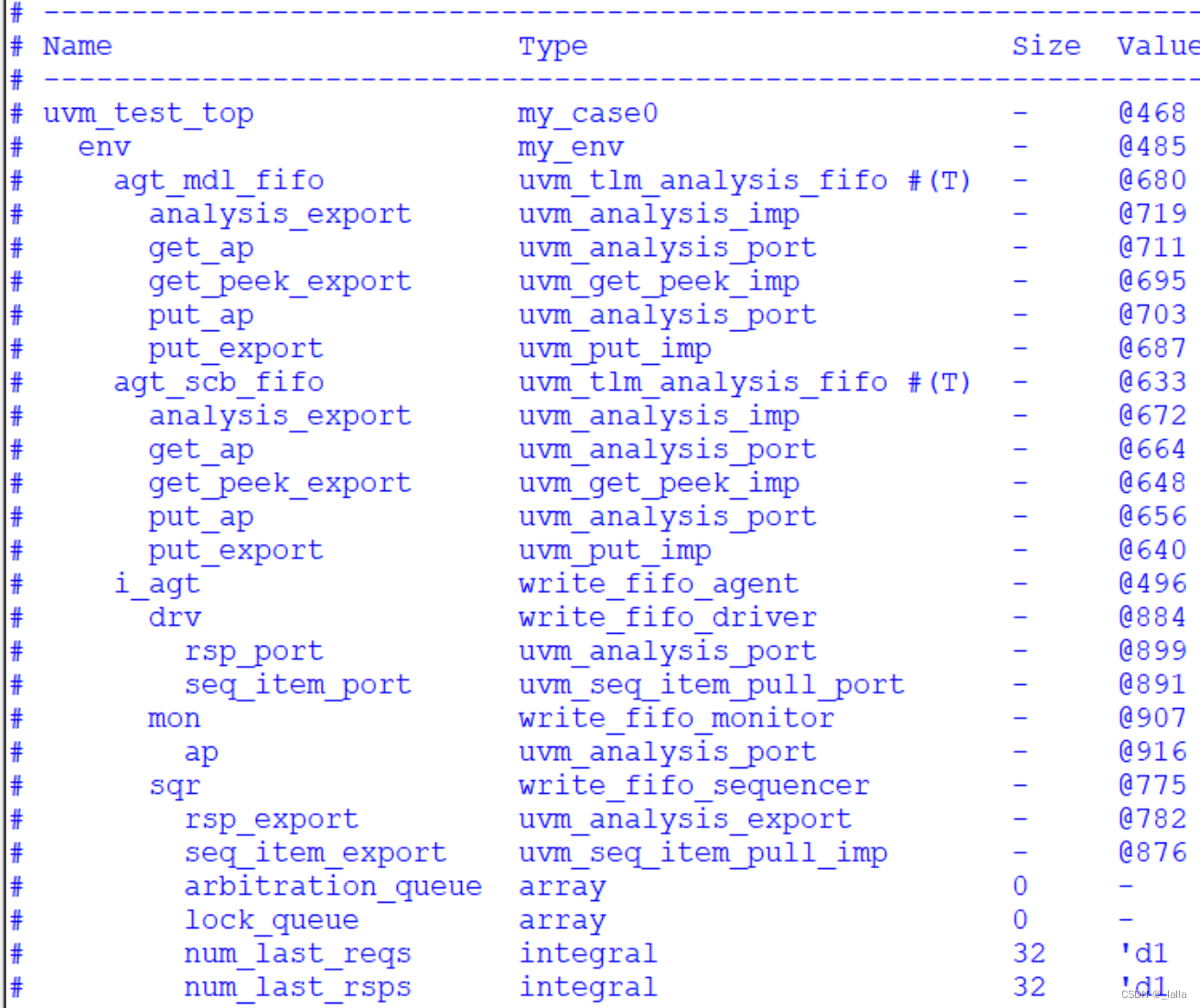

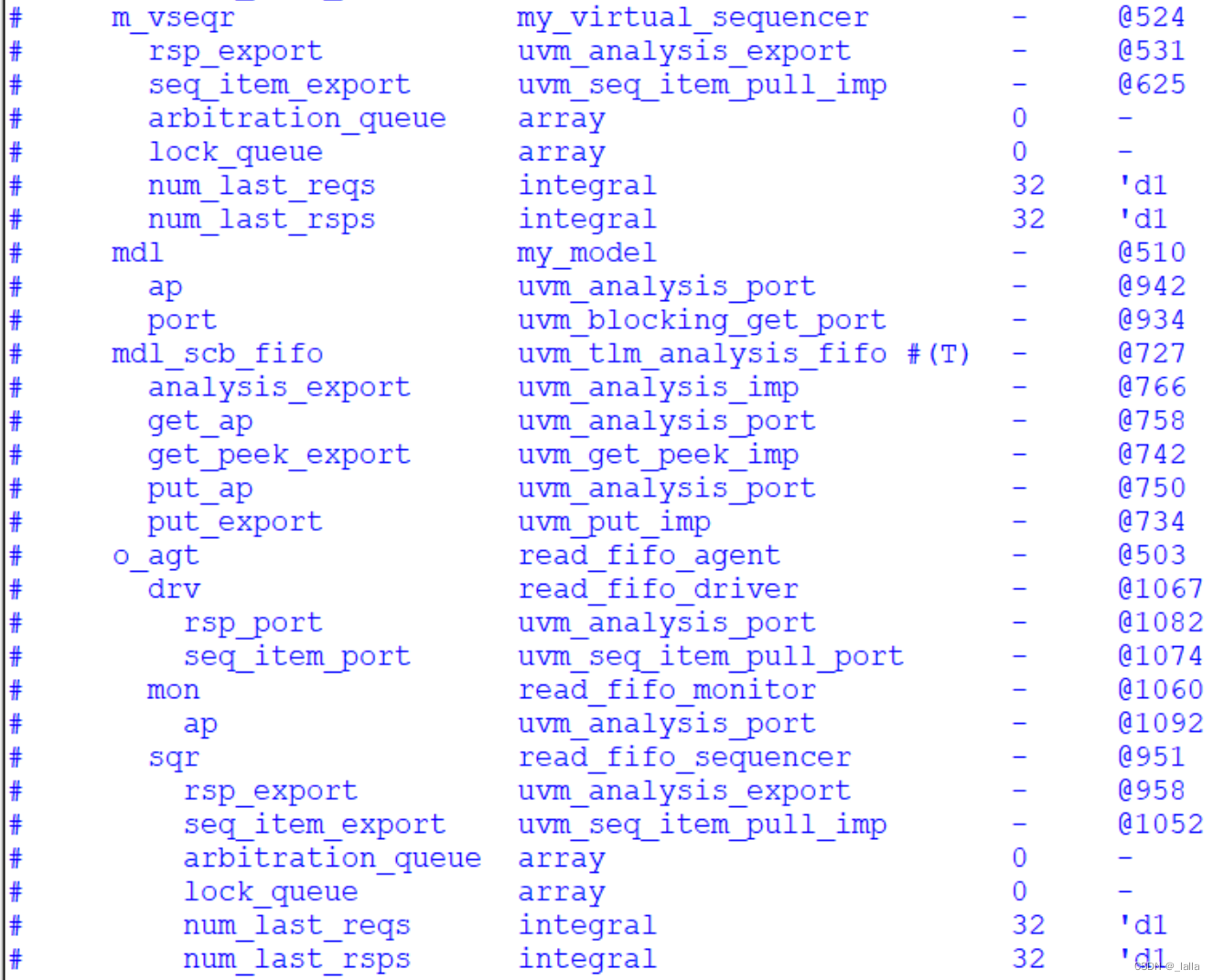

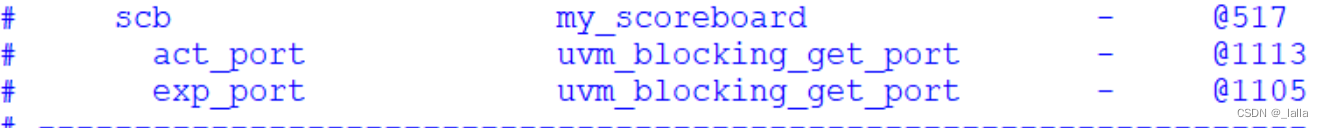

1、仿真命令如下,仿真后可以看到如下信息,包括树形结构等

vsim -novopt -classdebug work.top_tb

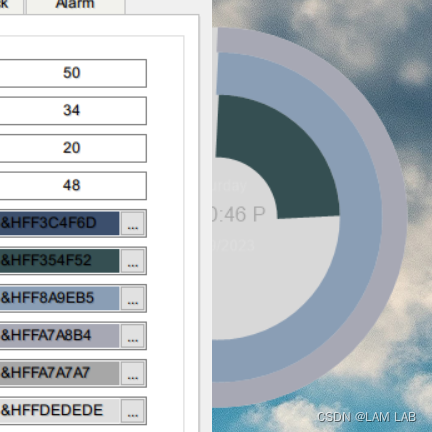

2、显示变量名称,点击如图所示按钮

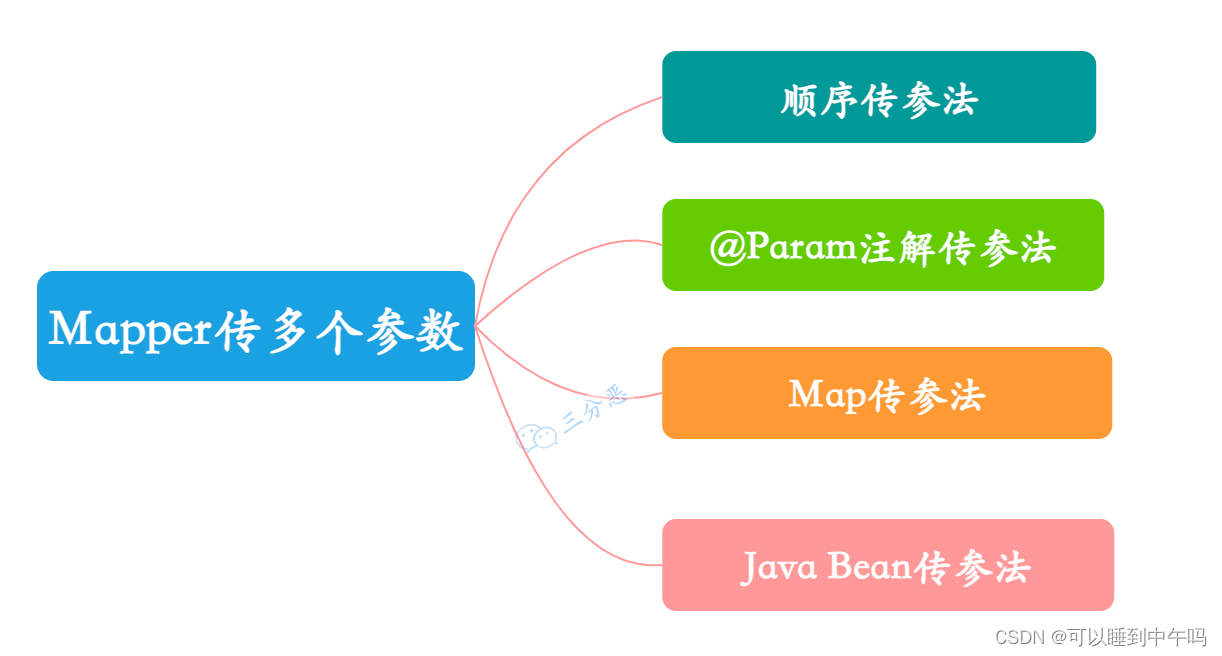

二、脚本文件编写

一般来说,使用图形化界面操作较为麻烦,通常用脚本代替

1、如下面所示的最简单的脚本文件,sim.do文件

TCL脚本

cd D:/uvm_test //通过cd命令切换到当前存放.sv代码的文件夹

vlib work //建立一个work工作区文件夹

set UVM_HOME C:/questasim64_10.6c/verilog_src/uvm-1.1d //设置UVM库的路径

set WORK_HOME D:/uvm_test //设置工作文件夹

set UVM_DPI_HOME C:/questasim64_10.6c/uvm-1.1d/win64 //设置DPI的路径

vlog +incdir+$UVM_HOME/src -L mtiAvm -L mtiOvm -L mtiUvm -L mtiUPF $UVM_HOME/src/uvm_pkg.sv $WORK_HOME/dut.sv top_tb.sv //编译verilog代码

vsim -novopt -c -sv_lib UVM_DPI_HOME/uvm_dpi work.top_tb //启动仿真

view wave * //添加所有顶层模块的仿真波形

run -all //运行仿真

再去执行这个do文件(两种方式)

vsim -do sim.do //写入bat文件,批处理文件,直接双击这个文件,就可以进行仿真出结果。新建txt,修改文件后缀名为.bat即可

do sim.do //命令行的执行方式,切换到路径,再直接使用do命令

下面这部分代码也类似

set TB "tb_top"

set INCDIR "+incdir+../design"

set VCOMP "vlog -cover bst -timescale=1ns/1ps -l comp.log $INCDIR"

# clean the environment and remove trash files

set delfiles [glob work *.log *.ucdb sim.list]

file delete -force {*}$delfiles

# compile the design and dut with a filelist

vlib work

eval $VCOMP ../src/designfile1.v

eval $VCOMP ../src/designfile2.v

eval $VCOMP ../src/designfile3.v

eval $VCOMP -sv ./dut_pkg1.sv

eval $VCOMP -sv ./$TB.sv

# run a test

set TEST chnl_burst_test

set SEED [expr int(rand() * 100)]

vsim work.tb -sv_seed $SEED -l sim.log +TESTNAME=$TEST

run -all

2、makefile脚本进行VCS仿真

all: com sim run_dve //定义all指令

com: //编译

vcs -sverilog -debug_all -timescale=1ns/1ns -f file.list -l com.log

sim: //仿真

./simv -l sim.log

run_dve: //后台打开仿真波形

dve -vpd vcdplus.vpd &

clean: //清除仿真生成的文件

rm -rf *.vpd csrc *.log *.key *.vdb simv* DVE*

三、编译错误

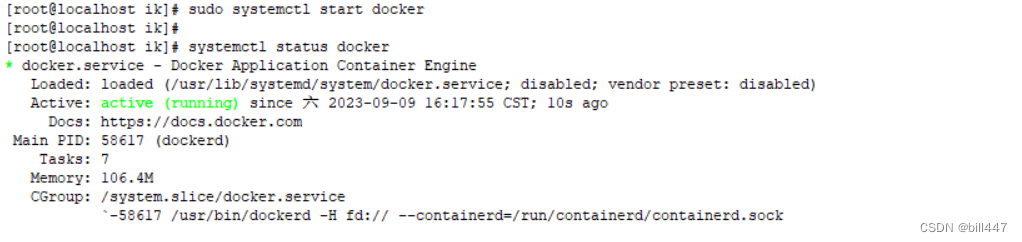

1、编译sv文件时报错(2022-11-27)

vlog -work work -vopt -sv -stats=none D:/practice/base_test.sv

QuestaSim-64 vlog 10.6c Compiler 2017.07 Jul 26 2017

** Error: (vlog-13069) D:/practice/base_test.sv(4): near "uvm_test": syntax error, unexpected IDENTIFIER.

** Error: D:/practice/base_test.sv(4): Error in class extension specification.

解决方法:在文件开头加入UVM库文件

但是我在头文件里面添加这些,然后每个分开的文件也要加这个,是不是有简单的方法?

更新: 可以分开做成package,比如agent里面的各组件打包,env、model分开打包,再去包含。这样在每个子文件的开头就不需要都去写下面两行代码,也不需要根据它使用了哪些类,然后去include这些文件。(2023-2-13)

`include "uvm_macros.svh"

import uvm_pkg::*; //vcs里需要先编译,Questa则已经编译到库里

更新:不是添加上面两个文件,而是在每个文件中添加涉及到除自身之外的模块!例如最后的case0中就用到了如下这些文件

(不确定是不是正确,这样做了之后没报错,但是总感觉很麻烦,不能直接在最顶层全部包含这些文件,然后每个子文件自己去调用吗)

`include "my_virtual_sequencer.sv"

`include "write_fifo_seq.sv"

`include "read_fifo_seq.sv"

`include "base_test.sv"

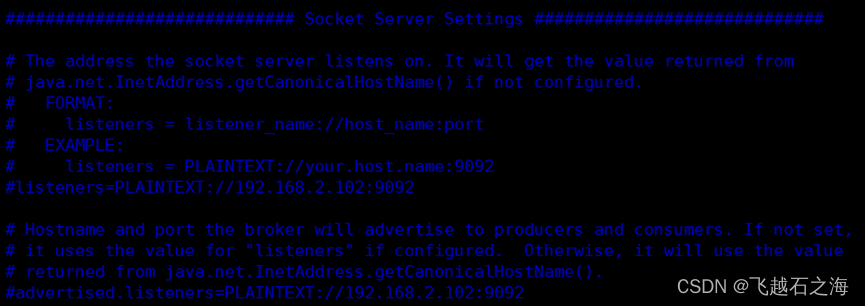

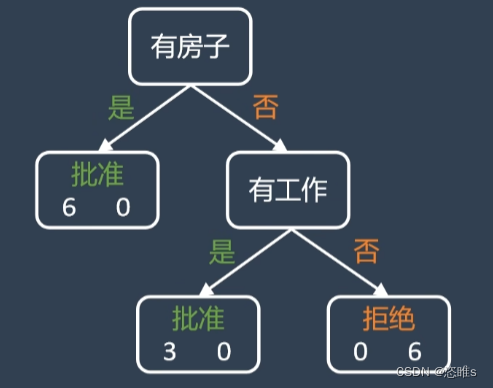

2、编译设计的.v文件时报错(2023-2-13)

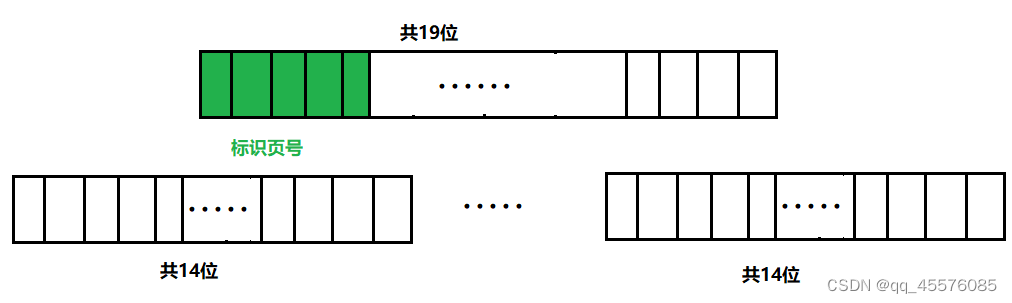

在设计文件中,为了修改fifo memory更加方便,因此把参数定义在了defines.v文件,包括存储宽度、深度、读写时钟频率,然后在其他文件中要用到这个参数就使用 'WIDTH来代替(前面的符号是一个顿号)。

把设计文件放到一起编译时,报错

(vlog-2163) Macro `ADDRSIZE is undefined.

解决方法: 在每个文件的开头加入include "defines.v",这样就能索引到defines中定义的参数。有时候再出现类似问题,可能是要把其换成绝对路径。

3、编译是有警告,仿真是有这个错误(2023-2-13)

在testbench中有如下代码

initial begin

$fsdbDumpfile("Wave.fsdb"); //FSDB Dumper 指定波形文件名称

$fsdbDumpvars; //指定某个模块下的多少信号,把这些信号输出为波形

end

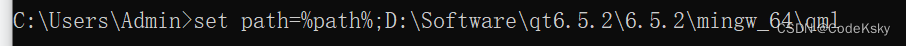

原因好像是没有FSDB Dumper这个库,需要添加环境变量。或者是在vcs/verdi中使用这些代码

[TOFD] - System task or function '$fsdbDumpvars' is not defined.