目录

DDS实现原理

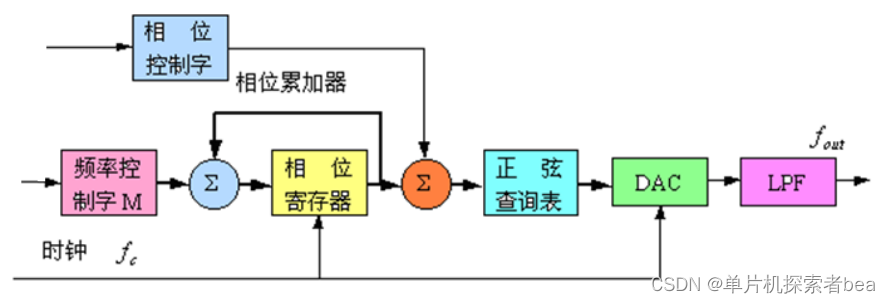

DDS整体设计框图

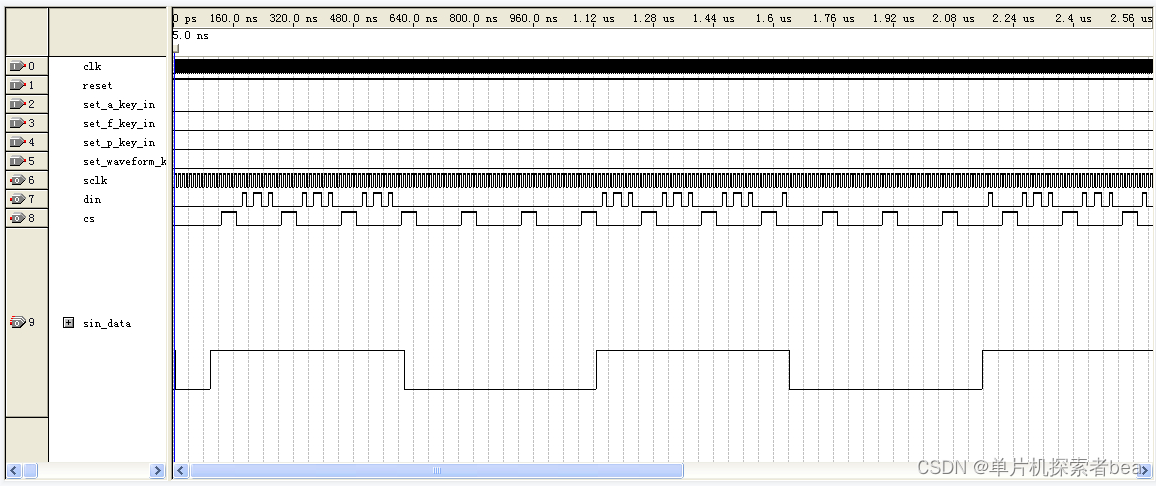

Quartus II 仿真

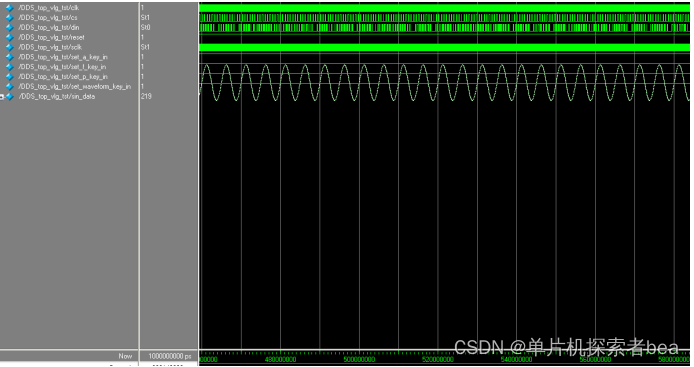

modelsim仿真

顶层代码

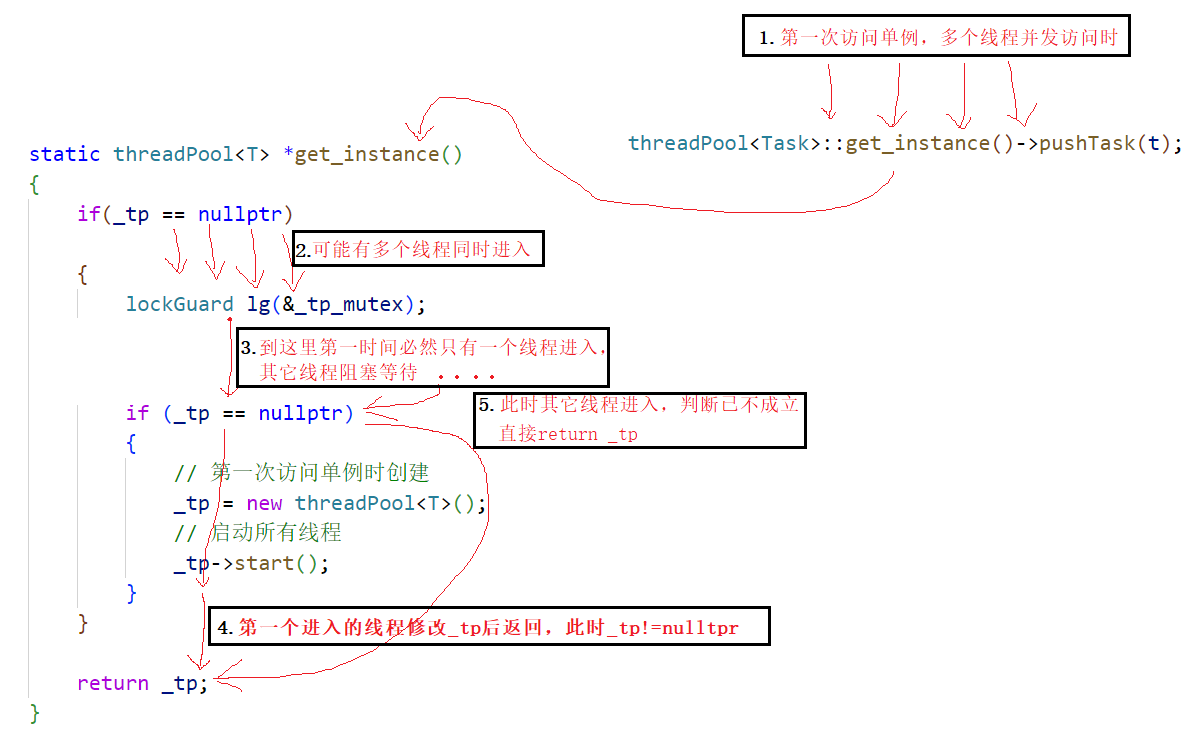

DDS实现原理

DDS(Direct Digital Frequency Synthesizer)直接数字频率合成器,也可叫DDFS。

- DDS是从相位的概念直接合成所需波形的一种频率合成技术。

- 不仅可以产生不同频率的正弦波,而且可以控制波形的初始相位。

-

主要构成:

内部:相位累加器,正弦查找表

外围:DAC,LPF(低通滤波器)

工作过程

1、将存于ROM中的数字波形,经DAC,形成模拟量波形。

2、改变寻址的步长来改变输出信号的频率。 步长即为对数字波形查表的相位增量。由累加器对相位增量进行累加,累加器的值作为查表地址。

3、DAC输出的阶梯形波形,经低通滤波,成为模拟波形。

-

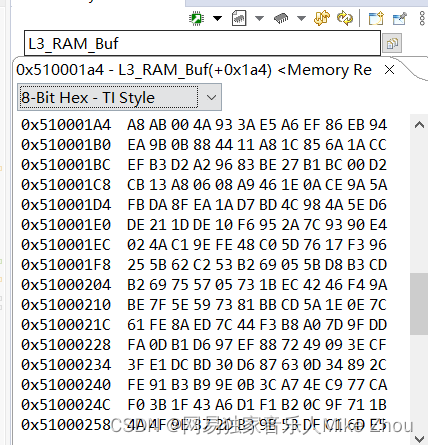

DDS整体设计框图 Quartus II 仿真

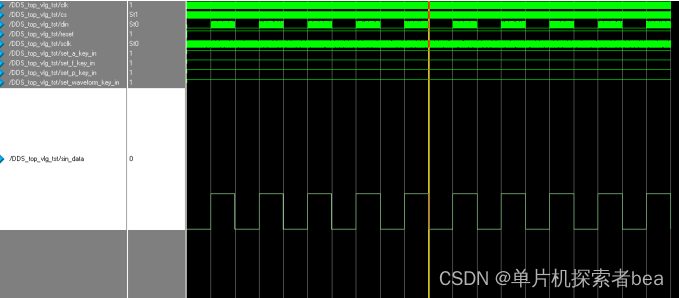

Quartus II 仿真

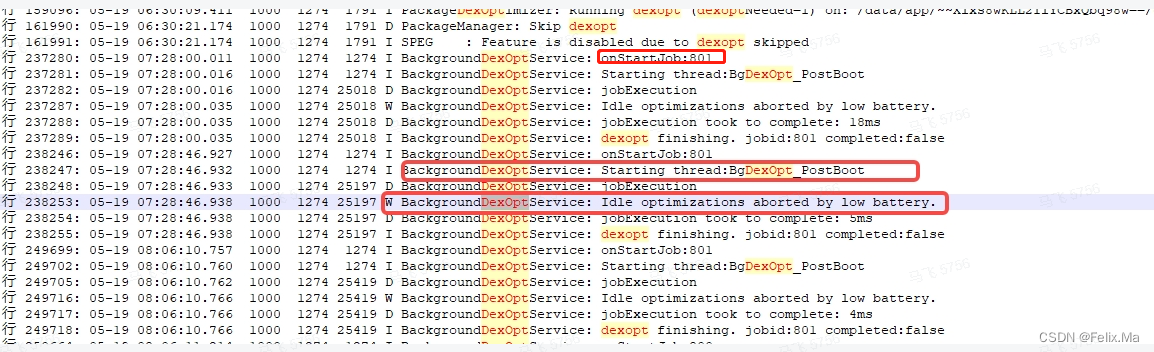

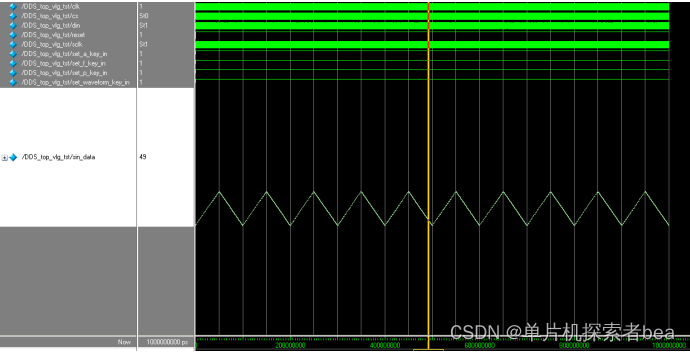

modelsim仿真图

顶层代码

(代码较长,完整工程免费获取请关注公众号:FPGA设计苑)

module DDS(

clk, //时钟输入

dds_data_out, //DDS数据输出

set_waveform, //设置输出的波形

set_f, //设置频率

set_a, //设置幅值

set_p //设置频率

);

input clk;

input [1:0] set_waveform;

input [20:0] set_f;

input [4:0] set_a;

input [8:0] set_p;

output [9:0] dds_data_out;

wire clk;

wire [1:0] set_waveform;

wire [20:0] set_f;

wire [4:0] set_a;

wire [9:0] set_p;

wire [9:0] dds_data_out;

/**************连接线***************/

wire [31:0] f32_bus;//AC频率控制字输入

wire [31:0] reg32_out;//32位寄存器输出

wire [31:0] reg32_in;//32位寄存器输入

wire [8:0] reg10_in;

wire [8:0] reg10_out_address;

/**************缓存寄存器******************/

wire [9:0] sin_data;

wire [9:0] tri_data;

wire [9:0] squ_data;

//wire [9:0] saw_data;

reg [9:0] dds_data_reg;

reg [20:0] set_f_reg;

/***********************************/

assign f32_bus[31:21]=11'b000_0000_0000;//初始化,高位置低

assign f32_bus[20:0]=set_f_reg; //低位可以设置DDS的输出频率

/*********************元件例化************************************/

adder_32 u1(.data1(f32_bus),.data2(reg32_out),.sum(reg32_in));

reg32 u2(.clk(clk),.data_in(reg32_in),.data_out(reg32_out));

adder_10 u7(.data1(set_p),.data2(reg32_out[31:23]),.sum(reg10_in));

reg_10 u8(.clk(clk),.data_in(reg10_in),.data_out(reg10_out_address));

/*****************波形选择*******************************************/

sin_rom u3(.address(reg10_out_address),.clock(clk),.q(sin_data));//正弦

tri_rom u4(.address(reg10_out_address),.clock(clk),.q(tri_data));

squ_rom u5(.address(reg10_out_address),.clock(clk),.q(squ_data));

// saw_rom u6(.address(reg10_out_address),.clock(clk),.q(saw_data));

/***********************设置波形和设置频率***************************/

always @(set_waveform,sin_data,tri_data,squ_data)

begin

case (set_waveform)

2'b00://正弦波

begin

dds_data_reg<=sin_data;

set_f_reg<=set_f;//设置范围为100Hz到20KHz

end

2'b01://三角波

begin

dds_data_reg<=tri_data;

set_f_reg<=set_f;//设置范围为100Hz到20KHz

end

2'b10:

begin

dds_data_reg<=squ_data;//方波

set_f_reg<=set_f;//设置范围为100Hz到20KHz

end

default:

begin

dds_data_reg<=sin_data;//正弦波

set_f_reg<=set_f;//设置范围为100Hz到20KHz

end

endcase;

end

/***********************设置电压幅值***************************/

assign dds_data_out=dds_data_reg*set_a/10;//设置电压幅值

endmodule