1非易失性器件的存储原理

1.1最小存储单元-浮栅晶体管

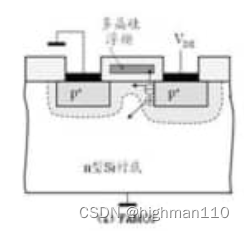

我们当前使用的非易失性存储器的基本存储单元基本都是浮栅晶体管。技术在发展,浮栅晶体管的结构也在调整演进,接下来将用系列文章中的三篇分享EPROM、EEPROM、FLASH这三种非易失存储器件的基本存储单元原理。浮栅晶体管有很多类型,基本原理类似。今天先分享EPROM所用的浮栅晶体管原理,后面再分享EEPROM和FLASH的,有了今天的基础,后面的基本类似,就很容易理解了。

1.1.1EPROM

EPROM电可编程只读存储器,是通过使用高度参杂的多晶硅(poly-Si)作为浮栅材料而制成的,它的基本存储单元被称为叠栅雪崩注入MOS晶体管(SAMOS)。下面两张截图是从郭天祥老师的B站视频中截图过来,大家有兴趣可以去看看视频。

写入:S接地,D接高电压(以前通常为25V,随着工艺的提升,这个电压的要求也再下降),G接一个25V的脉冲,此时DS之间发声雪崩击穿形成了沟道,有电子移动,此电子在G级的25V脉冲形成的电场作用下,穿过二氧化硅进入浮栅中,完成写入,这个过程叫做热电子注入(hot electron injection),这个过程在绝缘氧化层达到100nm时即可发生,工艺要求不算太高。由于浮栅处于绝缘介质二氧化硅之中,所以电子注入后,在没有合适外力的条件下,是不会流失的,这就是所谓的非易失存储。写入完成后电压去除,由于浮栅中的电子存在,形成电场排斥P衬底中的电子,吸引空穴,这时P衬底上无法形成N型反型层,也就无法形成沟道,所以当浮栅充满电时,管子时截止的。但是如果这是一个以PMOS为基底的浮栅晶体管,当浮栅充满电时,形成电场吸引N衬底中空穴,排斥电子,这时N衬底上形成P型反型层,与D、S中的P+区域连通,形成沟道,此时管子是导通的。浮栅的基底类型不一样,充满电时的管子状态是不一样的,大家注意。

擦除:无需接电源,将此浮栅结构暴露在紫外光下,由光给浮栅中的电子充能,电子获得能量后加速运动回到衬底当中,完成擦除。当然,我个人理解,这种结构下将G极和P衬底之间加一个负电压,通过电场迫使浮栅中的电子再回到衬底理论上也是可以,但是由于浮栅中的电子本身不是热电子,需要更高的场强才能使电子穿越绝缘层,这样做是不经济的,而且电压过高还可能损坏MOS管,所以干脆用紫外线长时间照射这种方式来给电子充能。

当我们拿到一片新的EPROM时,存储浮栅里是没有电荷的,默认读出来是1,而向浮栅注入电荷,就是写0的过程。即浮栅充了电表示0,没有电表示1。

读过程:如下图所示为一个存储单元示意图,Wj为字线,Yj为位线,上电后VT1导通,Yj默认为高电平。若浮栅中没有电荷时,此浮栅晶体管就相当于一个普通的MOS管(以NMOS基底为例),当要读这个存储单元时,Wj给高电平,NMOS导通,将Yj拉低,然后经反相器后输出1;若浮栅中充满了电,Wj给高电平,浮栅中的负电荷将抵消部分电场,NMOS管无法导通,Yj仍为高电平,经反相器后输出0。如果是一个以PMOS为基底的浮栅,同样想办法控制其通断就能读到有电荷和无电荷时的状态。

网上还有一种说法是EPROM的基本存储单元为浮置栅雪崩注入MOS晶体管(FAMOS),它是在p-MOSFET的基础上,只是把栅极改变为一个浮空的栅极——浮栅(用多晶硅制作);该浮栅被优质SiO2包围着,其中的电荷可较长时间地保存起来。

写入:FAMOS在常态时处于截止状态(即无沟道)。当源-漏电压VDS足够大时,漏极p-n结即发生雪崩击穿,将倍增出大量的电子-空穴对;其中空穴进入衬底,而部分高能量的热电子可越过Si/SiO2势垒(热发射)而注入到浮栅;当浮栅中积累的负电荷足够多时,即使得半导体表面反型而形成沟道,从而MOS器件导通。这就是说,器件开始时是截止的,待发生雪崩注入、浮栅中积累有电荷后才导通,因此根据MOS器件的导通与否,就可以得知浮栅中是否存储有电荷;这也就意味着FAMOS可以实现信号(电荷)的存储和检测,即具有存储器的功能。

擦除:这就结构要去除(擦除)该器件存储的电荷(信号)时就比较困难,即需要高能量光子(紫外光或者X射线)等的照射才能使得浮栅中的电子被释放出来。这要求在管壳上开孔以把光照射进去。这种结构没有控制栅,也就不可能通过加反向电场的办法将电子拉回来,电子要获取能量只能光照了。

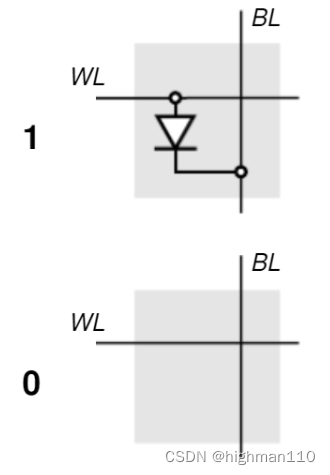

这种结构由于没有控制栅极,所以只能将这个管子当成二极管用,组成ROM的存储阵列,当浮栅中没有电荷时,管子截止,当浮栅中有电荷时,管子导通,两种状态代表两种存储内容。假设选中某单元时:字线拉高,位线拉底,当浮栅中没有电荷时,管子截止,相当于下图下,字线和位线分开,位线输出0,经反相器后输出1;当浮栅中有点荷时,管子导通,位线和字线通过管子连接,相当于下图上,位线被拉至字线的高电平,经反相器后输出0。这类是我自己的理解,具体是不是这样我尚未找到佐证的资料。

EPROM中究竟用的是以上哪种结构大家自行甄别一下,也有可能是技术在演进过程中出现了两种结构都存在的情况。

今天的分享先到这里,下篇分享EEPROM的存储单元--浮栅隧穿氧化层(FLOTOX)存储器,敬请期待!