引言

话说,小编在CSDN博客跟客服机器人聊天,突然看到有个搜索热搜“pcie最全科普贴”。小编有点似曾相识呀,我就好奇点击了一下,没想到几年前写的帖子在CSDN又火了一把。

说到这里,顺带给自己打个广告哈~

各位朋友感兴趣的话,

欢迎关注【存储随笔】CSDN博客

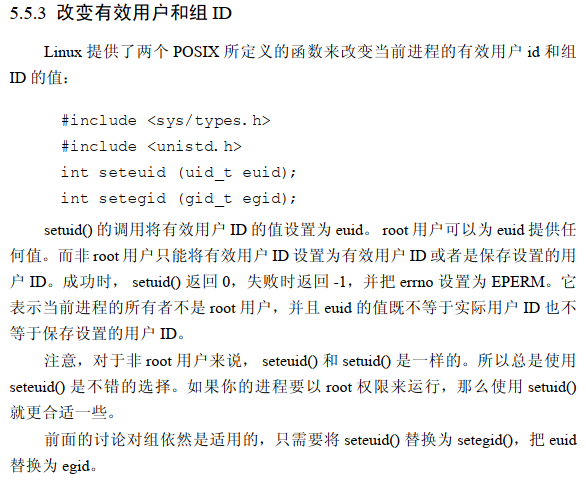

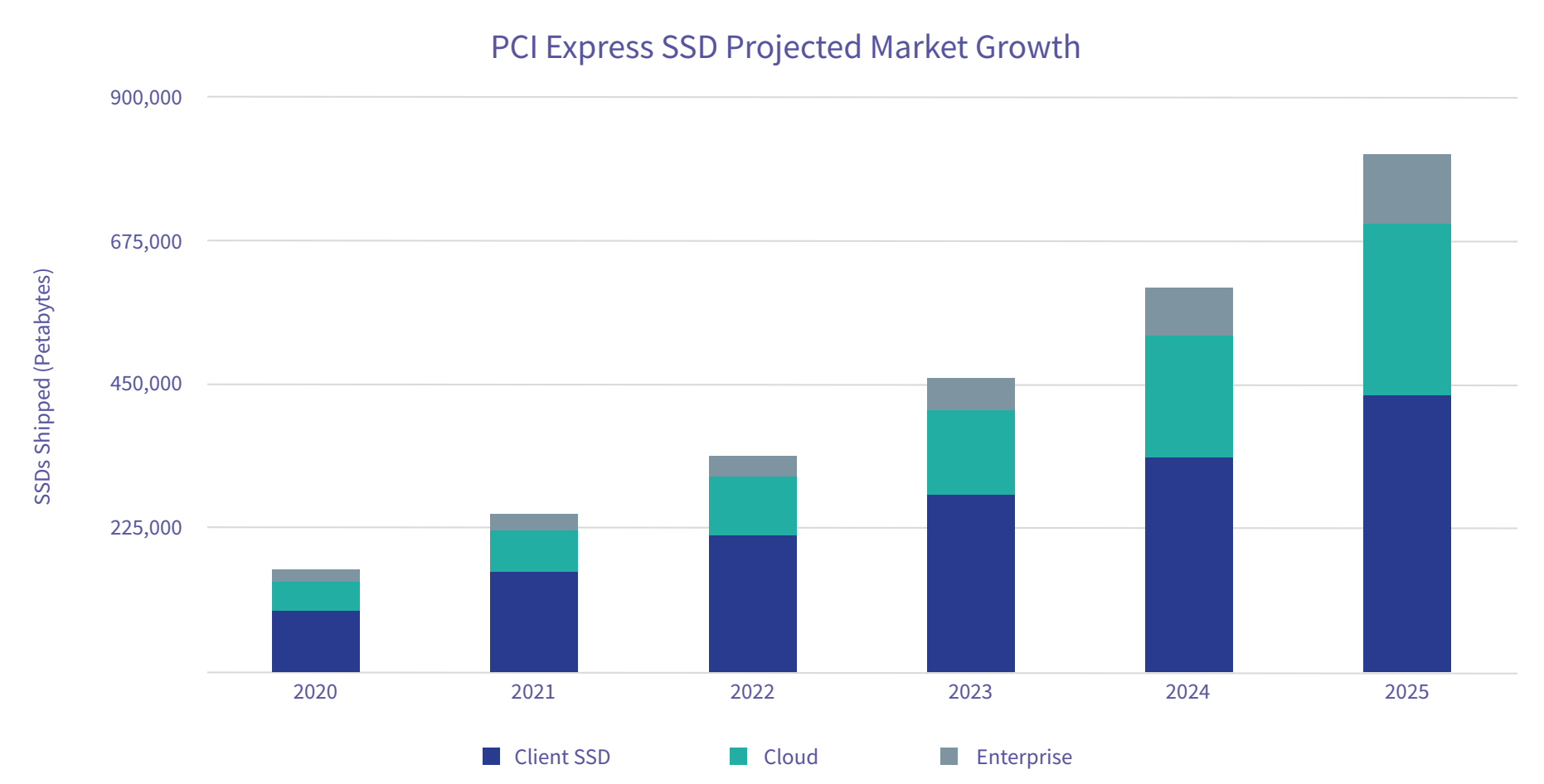

言归正传,为了追求高性能,PCIE SSD是数据中心的高性能标配,PCIE SSD在数据中心的占比还在继续攀升。

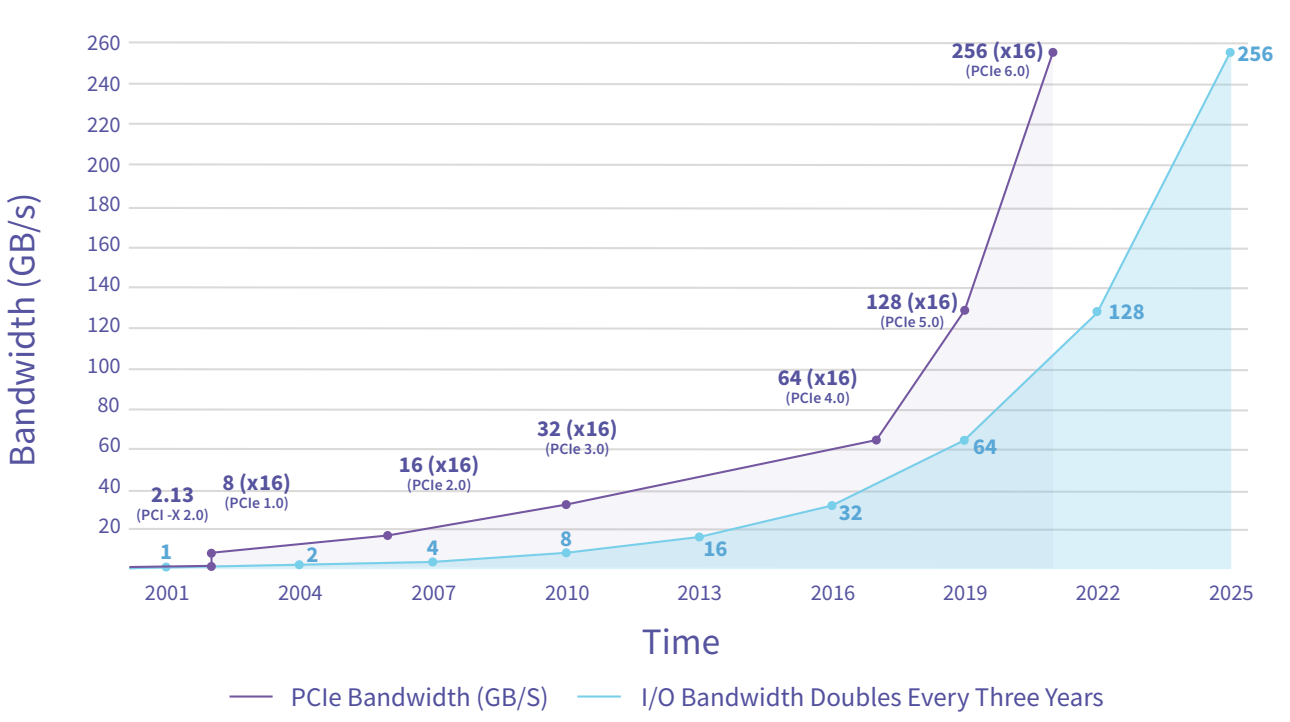

pcie协议5.0还没完全普及,pcie 6.0 spec已经发布,pcie 7.0 spec也在路上了,这个世界都在狂奔。

那么,pcie6.0/pcie7.0相对pcie 5.0有哪些重要的变化点呢,小编简单梳理一些信息,供大家参考~

当涉及到PCIe 6.0和PCIe 5.0之间的变化时,以下是一些关键点的详细介绍:

- 传输速率: PCIe 6.0的传输速率达到64 GT/s,相比PCIe 5.0的32 GT/s翻倍。这意味着PCIe 6.0可以提供更高的吞吐量和带宽,以满足高性能计算、人工智能加速器、高性能存储等快速发展的需求。这种提升可以进一步缩短数据传输时间,提高数据处理速度,同时减少延迟。

在PCIe 6.0规范中,6.0基础规范1.0版本正式发布,其速率达到64GT/s。另外,CE-Link和FLIT模式被引入以支持64GT/s的速率。CE-Link提供更高的数据吞吐量,而FLIT模式通过使用固定大小的数据包来提高效率。

- 信号和编码方式: PCIe 6.0采用了PAM4信号调制,而PCIe 5.0采用NRZ两电平调制。PAM4可以提高数据传输的效率,同时减少误码率。PAM4使用4个电压级别,相比NRZ使用2个电压级别,可以更有效地传输数据。

在PCIe 6.0规范中,PAM4信号被引入以支持64GT/s的速率。PAM4使用四个电压级别来传输数据,相比NRZ使用两个电压级别,可以更有效地传输数据。

- 前向纠错(FEC): PCIe 6.0引入了低延迟前向纠错(FEC)机制,以纠正传输过程中的错误,提高数据传输的可靠性。FEC是一种错误纠正技术,可以通过比较和纠正传输过程中的错误码,确保数据的完整性和准确性。

在PCIe 6.0规范中,FEC机制被引入以提高数据传输的可靠性。通过使用FEC,可以纠正传输过程中的错误,从而提高数据的完整性和准确性。

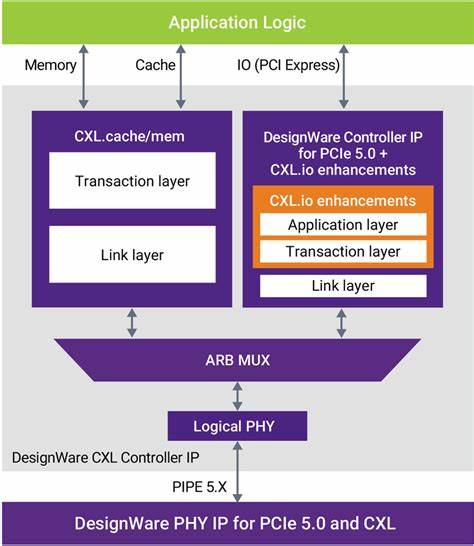

- 新的CXL规范融合: CXL 2.0是基于PCIe 5.0基础上定义,允许替代协议使用物理PCIe层的PCIe 5.0特性。当CXL加速器或者扩展卡、PCIE设备同时插入主机端口时,会优先pcie协议1.0速率协商,当双方确认支持CXL后,再激活CXL互联协议。

PCIe 6.0可能会与新的CXL规范融合,提供更高效的解决方案,以支持更高端的服务器和工作站应用。CXL是一种用于互连服务器和存储设备的开放式PCIe互连协议,可以提供更高的性能和更低的延迟。

- 新的机制和接口: PCIe 6.0增加了新的机制,如DOE、CMA、DMWr和IDE等,以支持更灵活和高效的数据传输。同时,PCIe 6.0可能会引入新的接口,如LTSSM新增加了L0p低功耗状态,允许部分 Lane Electric Idle、部分 Lane Active,以降低功耗并提高能效。

在PCIe 6.0规范中,引入了DOE(Data Ordered Exit)、CMA(Client Managed Abort)、DMWr(Destination Mailbox Write Response)和IDE(I/O Driver Enhancements)等新机制。这些机制可以提供更灵活和高效的数据传输,同时降低功耗并提高能效。此外,还引入了新的接口,如LTSSM新增加了L0p低功耗状态,允许部分 Lane Electric Idle、部分 Lane Active,以进一步降低功耗并提高能效。

DOE(Data Ordered Exit)、CMA(Client Managed Abort)、DMWr(Destination Mailbox Write Response)和IDE(I/O Driver Enhancements)是PCIe协议中的一些重要特性和机制,下面是它们的详细介绍:

- DOE(Data Ordered Exit):

-

- DOE是一种新的PCIe TLP类型,它允许设备在处理完一个请求的数据之前,主动结束该请求。

- 在传统的PCIe协议中,设备必须在处理完一个请求的所有数据后才能返回完成的消息。

- 而DOE允许设备在收到请求后,开始处理数据,并按照数据的传输顺序逐个返回完成消息,这样可以更好地利用设备的带宽和处理能力,提高性能。

- CMA(Client Managed Abort):

-

- CMA是一种用于处理PCIe传输错误的机制。

- 当一个设备检测到自己在传输过程中出现错误时,它可以主动中止当前的传输,并向请求该数据的客户端发送中止消息(Abort message)。

- 客户端在收到中止消息后,需要重新发送请求以获取正确的数据。

- DMWr(Destination Mailbox Write Response):

-

- DMWr是一种新的PCIe TLP类型,它可以用于延迟的内存写入。

- 在传统的PCIe传输中,一个设备向另一个设备发送请求后,需要等待该设备处理完数据后才能继续后续的传输。

- 而DMWr允许设备在发送请求后,立即返回一个响应消息,将处理数据的任务交给目标设备。目标设备可以根据自己的需要选择立即执行或延迟执行该任务。

- 这种机制可以更好地利用设备的带宽和处理能力,提高性能。

- IDE(I/O Driver Enhancements):

-

- IDE是一组针对I/O驱动程序的增强特性。

- IDE可以提高I/O驱动程序的开发效率,同时减少驱动程序中的错误。

- IDE提供了一组标准的API接口,可以使得驱动程序的开发更加简单和标准化。

这些特性和机制都是为了提高PCIe协议的性能、可靠性和安全性而设计的,它们在实际应用中具有重要的作用。

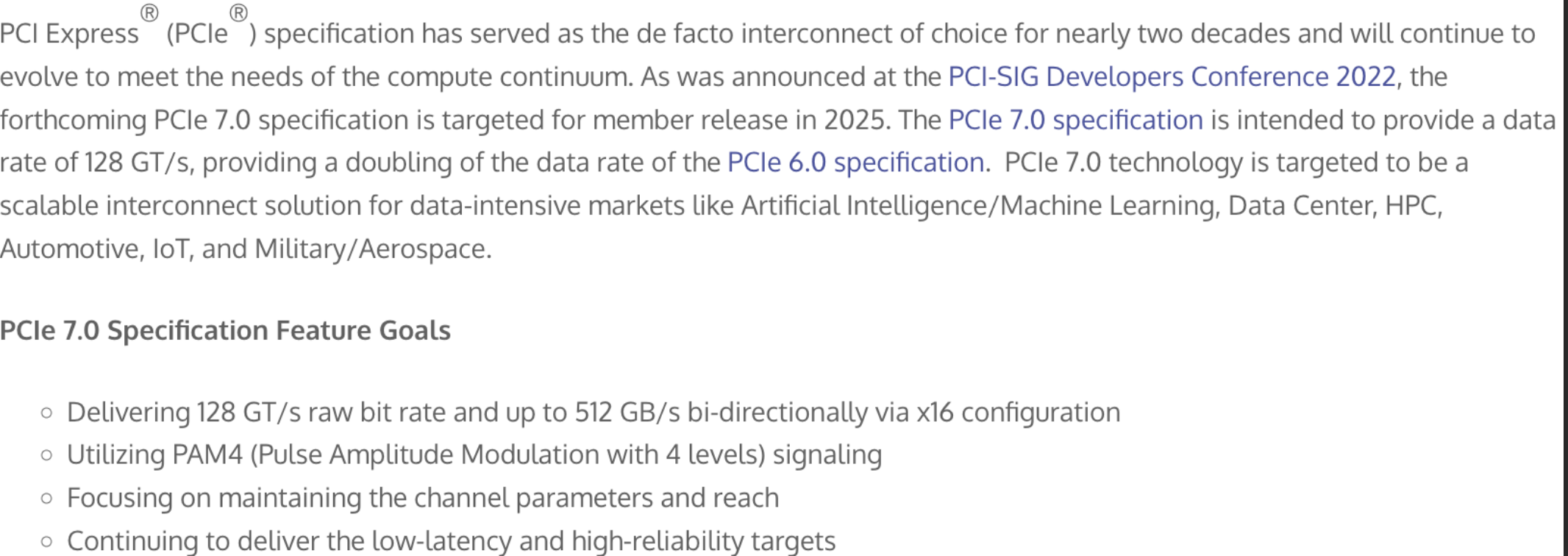

PCIe 7.0协议还未正式发布,从当前官网的信息来看,主要集中在性能的优化。PCIe 6.0/7.0相对于PCIe 5.0的挑战在于信号完整性、通道损失和复杂性等方面

预计将在2023年底或2024年的某个时候推出支持PCIe 6.0平台产品。需要注意的是,这些信息可能会随着技术的进步和市场的变化而变化,保持关注。