文章目录

- DDR4介绍

- 实验过程

- 编写XDC

- 使用IP核

- 上板验证

- TODO

- 参考

DDR4介绍

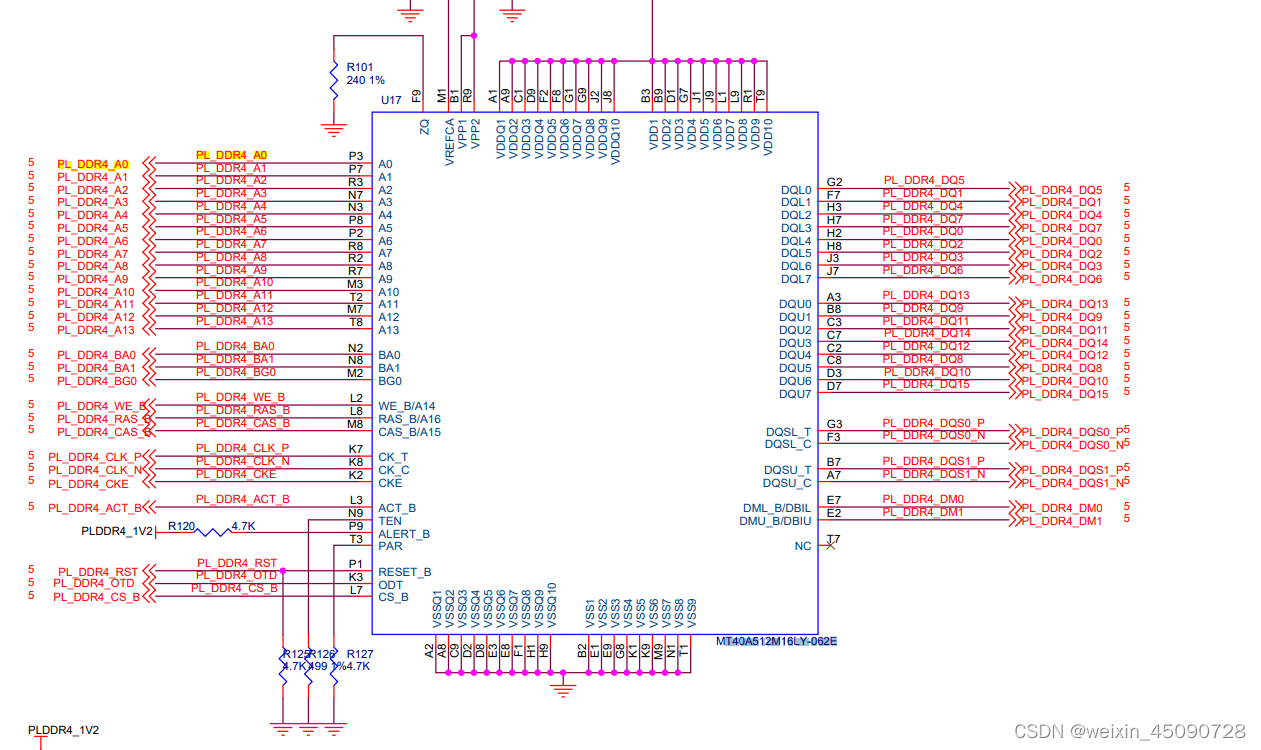

开发板PL有一颗16bit的DDR4。

先说明硬件信号(按该芯片):

| 信号名 | 说明 |

|---|---|

| DQ | Data input/output,双向数据线(这个芯片是x16的,使用DQ[15:0] ),可以看到这里芯片和ZYNQ的定义并不是一对一的,把数据线交换了,但是不会影响最终的使用 |

| DQS_t,DQS_c,UDQS_t,UDQS_c,LDQS_t,LDQS_c | Data strobe,读数据时输出,写数据时输入,x16时,LDQS对应DQ[15:8],UDQS对应DQ[7:0]。差分数据选通信号:差分信号对,作输入时与写数据同时有效,作输出时与读数据同时有效 |

| DM_n,UDM_n,LDM_n | Input data mask,写数据时的掩码信号,也是分别对应DQ的低8位和高8位,DM:Data Mask,DBI:Data Bus Inversion数据总线反转 |

| VSS | Ground,地 |

| VSSQ | DQ ground,数据线的地 |

| VDD | Power supply: 1.2V ±0.060V,供电 |

| VDDQ | DQ power supply: 1.2V ±0.060V,数据线供电 |

| VPP | DRAM activating power supply: 2.5V –0.125V/+0.250V,激活电压 |

| VREFCA | Reference voltage for control, command, and address pins,参考电压 |

| ZQ | Reference ball for ZQ calibration,ZQ校准,接一个240欧姆的参考电阻,下拉到地 |

| A[17:0] | Address inputs,地址线,A17只用到16Gb上面,A14、A15、A16还复用其他功能 |

| ACT_n | Command input |

| CS_n | Chip select |

| RAS_n/A16,CAS_n/A15,WE_n/A14 | Command inputs,一些命令设置,包含行地址、列地址有效什么的 |

| BA | Bank address inputs |

| BG | Bank group address inputs |

| CK_t,CK_c | Clock, Differential clock inputs,差分时钟输入 |

| CKE | Clock enable,时钟使能信号 |

| PAR | Parity for command and address |

| ALERT_n | Alert output |

| TEN | Connectivity test mode |

| ODT | On-die termination,片上终端电阻,把电阻做到了芯片内部 |

| RESET_n | Active LOW asynchronous reset,复位信号 |

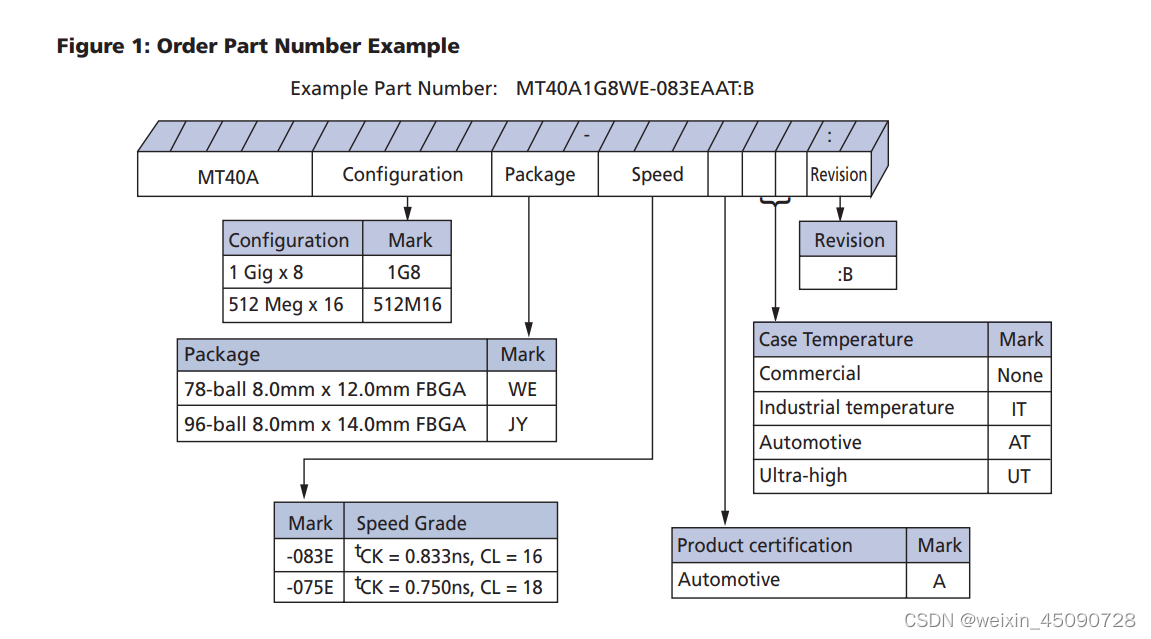

芯片信号为为MT40A512M16LY-062E,是镁光(Micron)的。从手册上看,这个型号的容量是8Gb(1GB),命名含义如下:

这里面的Meg和Gig都是一个单位,512M16表示容量是512Megx16,后面的16bit是位宽度。

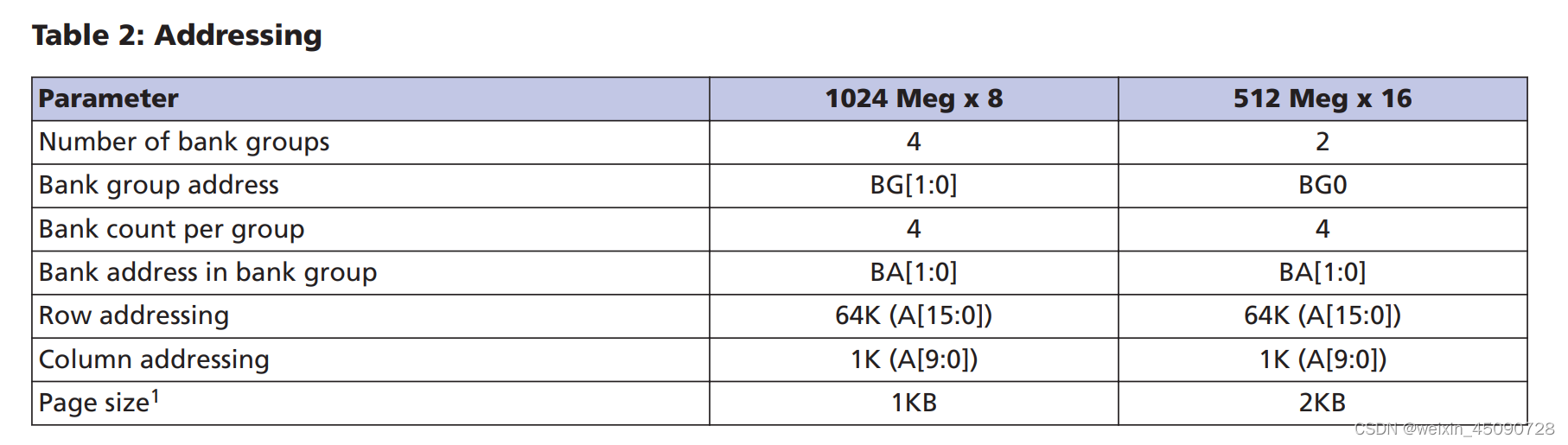

然后是一些参数,DDR4引入了bank group的概念,一个bank group包含多个bank。MT40A512M16LY有两个bank group,使用1根地址线BG0(BG:bank group)即可进行寻址,每个bank group包含4个bank,使用两根地址线BA[1:0](BA:bank address)即可进行寻址。除了bank的地址,DDR4还用有17根地址线A[16:0],设计时选择分两次使用定位一个地址的方案,行列公用这些地址线,第一次是行地址,第二次是列地址。MT40A512M16LY使用行寻址使用了A[15:0]的16根地址线,列寻址使用了A[9:0]的10根地址线。

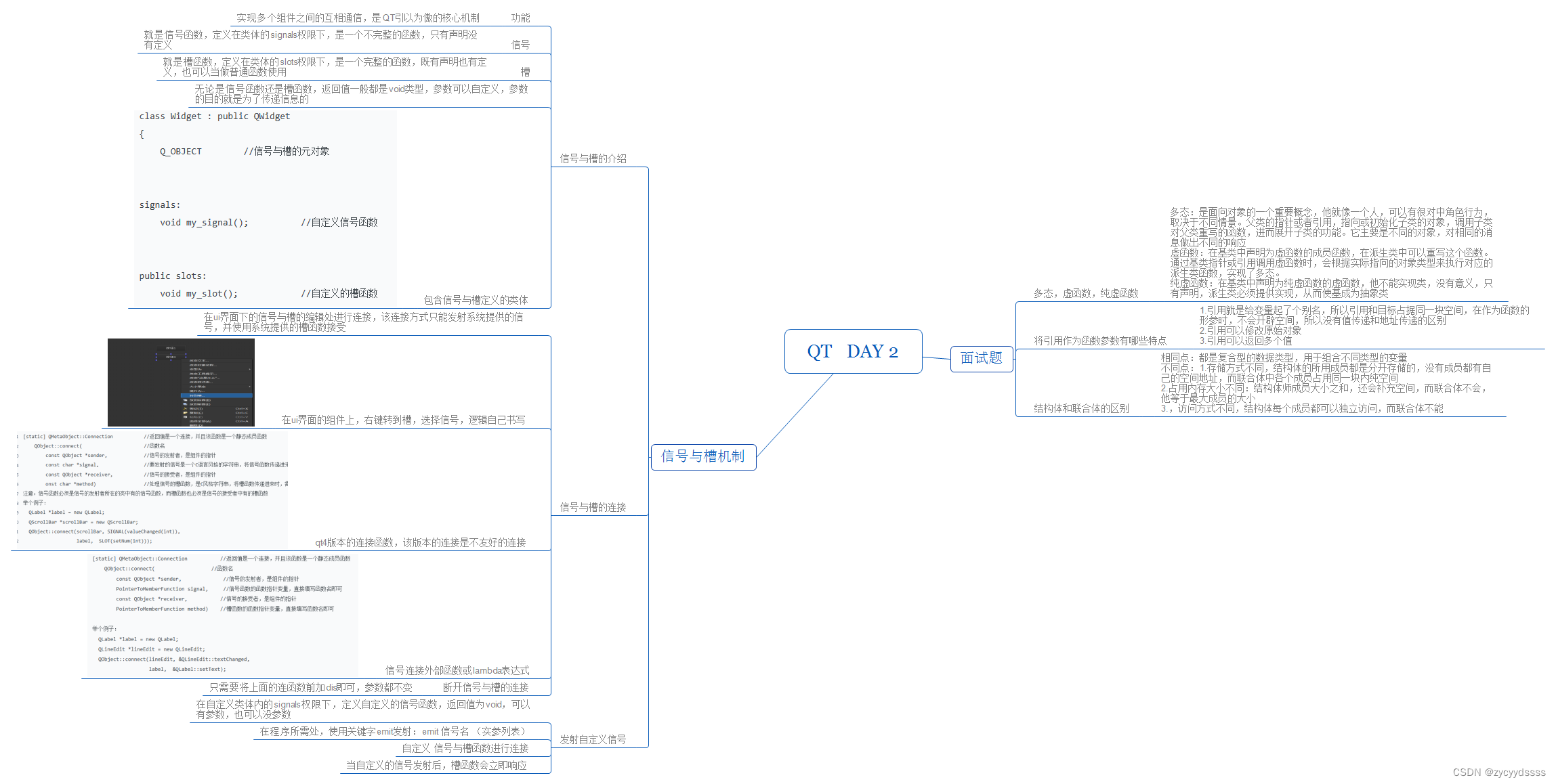

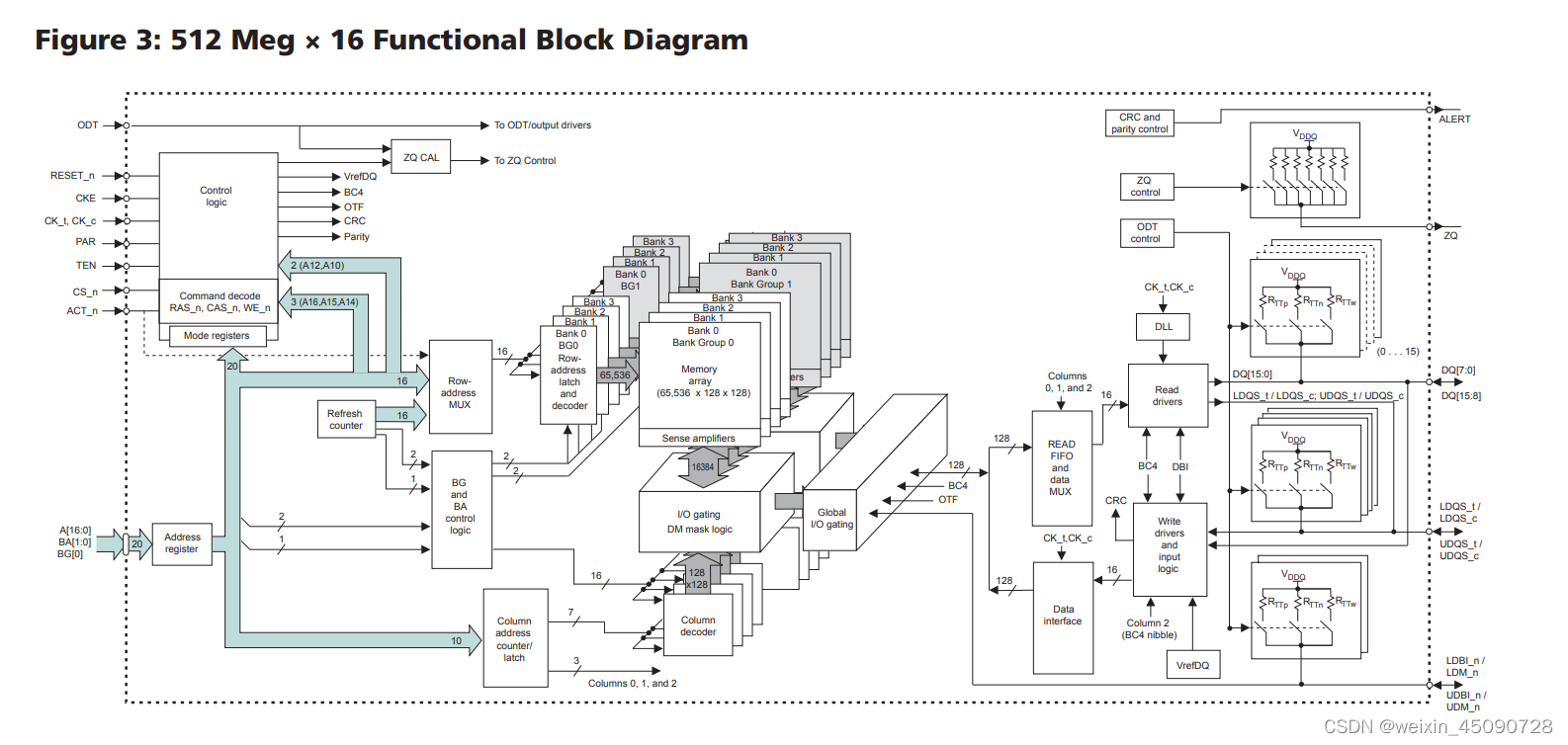

下面是芯片的内部结构图,也要配合前面管脚定义去理解。左下角是地址寄存器,包含A[16:0],BA,BG,BA和BG用于控制选择到具体的哪一个bank,A[16:0]同时被连接到行地址和列地址选择寄存器,是复用,因为读取的时候是分两次的,一次行地址,一次列地址。

实验过程

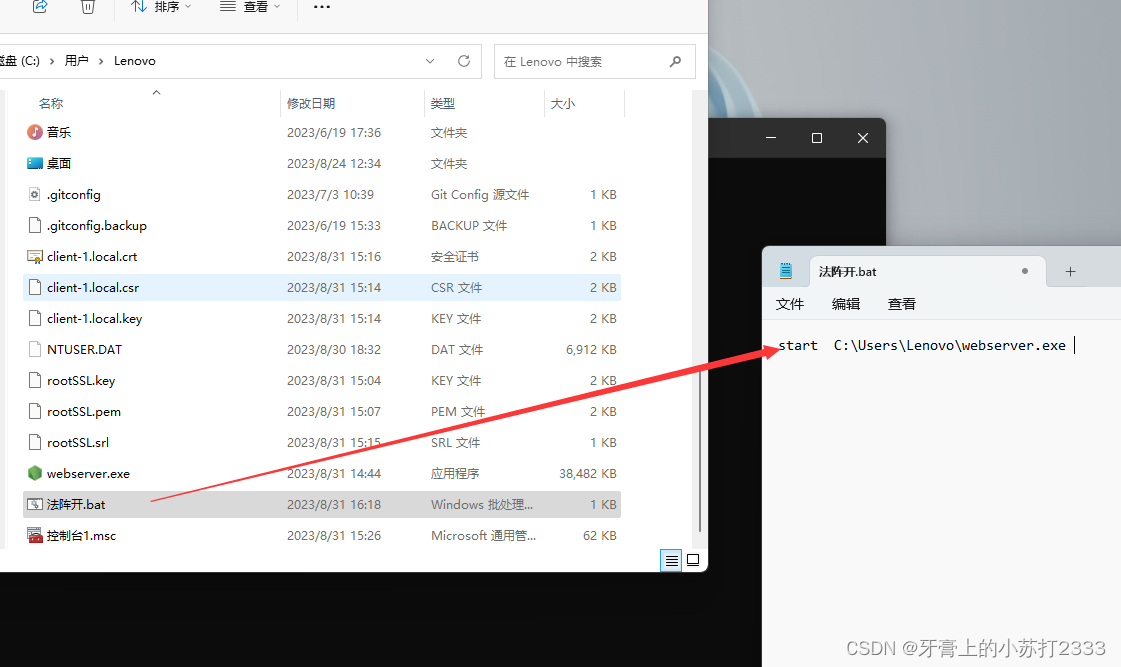

编写XDC

对着原理图,使用图形界面或者代码的方式进行设置即可。要一个管脚一个管家的去设置。

DDR4的管脚。

系统时钟的管脚。

使用IP核

Vivado提供了操作了DDR的IP核,主要是创建工程和IP和的添加和使用。

- 在“IP Catalog”的搜索框搜索“mig”,快速找到“Memory Interface Generator”,选择DDR4 SDRAM。

- 设置DDR参考时钟、内存类型、位宽,主要是硬件决定的一些信息。Component Name 可以修改,Controller/PHY Mode 选择“Controller and physical layer”,参考时钟选择 200MHz,即 5003ps,Momory Part 选择”MT40A512M16HA-083E”,Data Width 选择 16,其他设置保持默认,点击 OK。

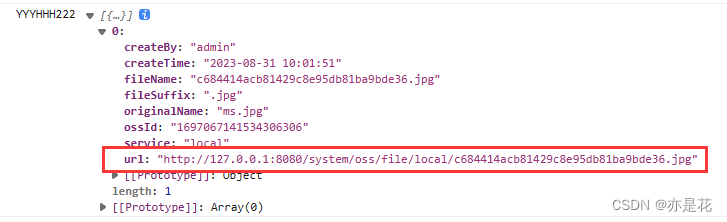

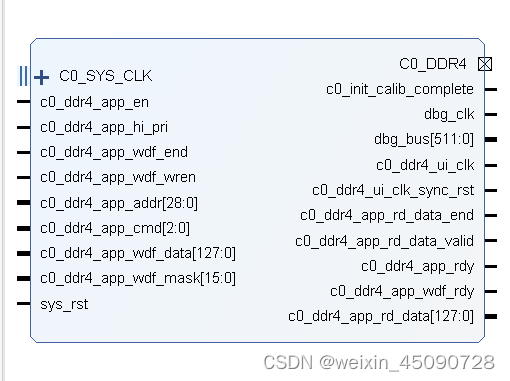

这个IP和相当于一个DDR4的控制器,经过设置之后的IP和接口如下。

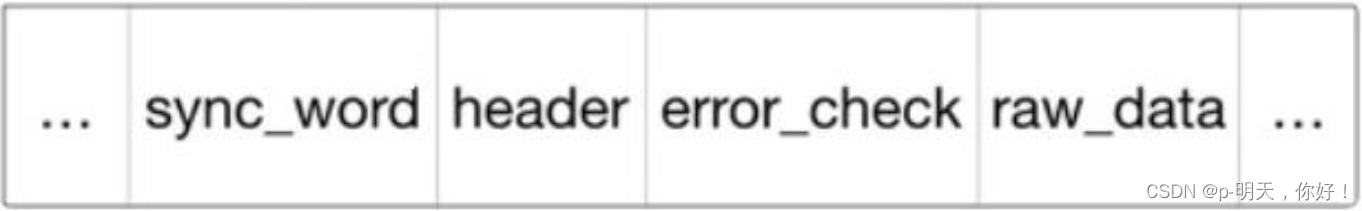

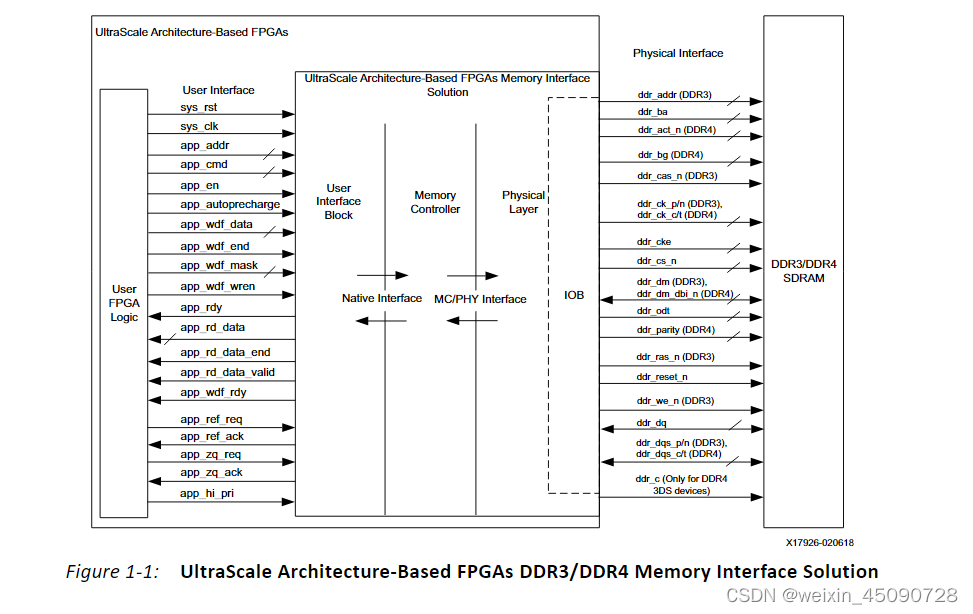

官方文档的结构描述,右边是物理的接口,直接连接到DDR,左边接口是用户接口即读写ddr需要操作的接口:

wdf 是 write data fifo?写数据的时候,ip核内部先把数据放到FIFO里?

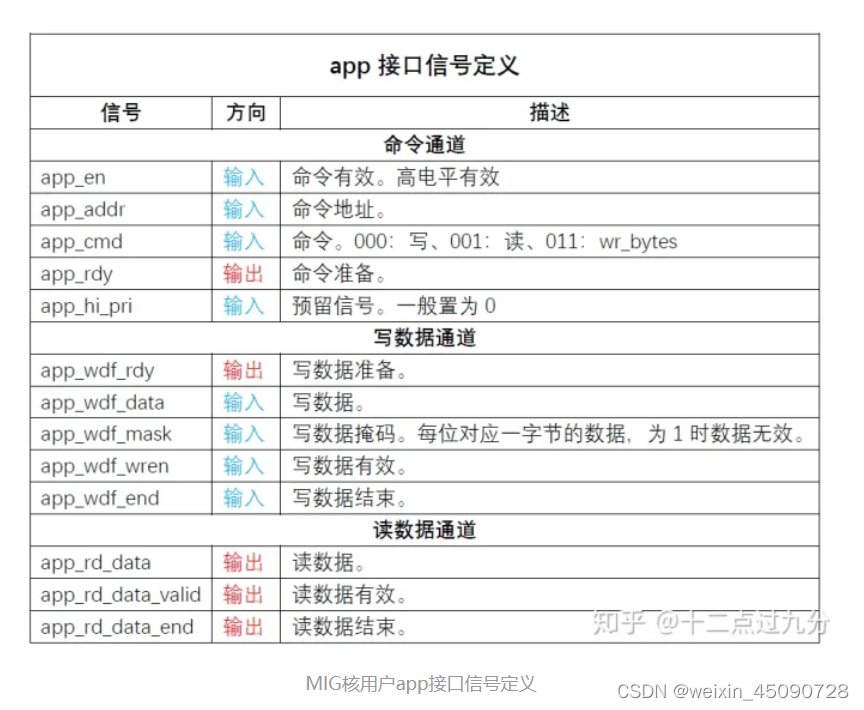

| 信号 | 描述 |

|---|---|

| app_addr[APP_ADDR_WIDTH – 1:0] | 当前请求的地址 |

| app_cmd[2:0] | 当前请求的命令 |

| app_en | 使能信号,地址和命令有效 |

| app_autoprecharge | set the A10 autoprecharge bit on the DRAM |

| app_wdf_data[APP_DATA_WIDTH – 1:0] | 写命令的数据 |

| app_wdf_end | 表示写入数据的结束 |

| app_wdf_mask[APP_MASK_WIDTH – 1:0] | app_wdf_data的掩码 |

| app_wdf_wren | 写数据有效 |

| app_rdy | 表示用户可口可以接收命令 |

| app_rd_data[APP_DATA_WIDTH – 1:0] | 读命令读取数据 |

| app_rd_data_end | 读出数据的结束 |

| app_rd_data_valid | app_rd_data有效 |

| app_wdf_rdy | 写数据FIFO准备好接收数据,当使能信号和该信号一起有效时,数据被接收 |

| app_ref_req | 用户刷新请求 |

| app_ref_ack | 用户刷新请求完成 |

| app_zq_req | User ZQCS command request |

| app_zq_ack | User ZQCS command request completed |

| app_hi_pr | This input is reserved and should be tied to 0 保留,下拉到0 |

| ui_clk | This user interface clock must be one quarter of the DRAM clock |

| init_calib_complete | PHY asserts init_calib_complete when calibration is finished,校准完成后输出 |

| ui_clk_sync_rst | This is the active-High user interface reset,复位 |

| addn_ui_clkout | Additional clock outputs provided based on user requirement |

| dbg_clk | Debug Clock. Do not connect any signals to dbg_clk and keep the port open during instantiation,调试时钟 |

上板验证

代码的ila没设置成功,弹出来一个这个窗口。

TODO

看不下去了,等提升下能力后再来看。

- 读写时序没进行分析。

- ila为什么没设置成功。

- 再分析下代码。

参考

- DDR的型号问题

- DDR4 SDRAM基础介绍

- DDR4实战教学(一):DDR4寻址原理

- 地址\数据总线在走线时互换

- DDR4读写测试(一):MIG IP核配置

- DDR4读写测试(二):基本读写测试

- DDR一些引脚说明

- DR4读写测试实验 摘自【正点原子】DFZU2EG/4EV MPSoC 之FPGA开发指南V1.0