文章目录

- 前言

- 一、DVP 接口时序逻辑设计

- 二、基本数据流接收

- 三、像素位置输出

- 四、舍弃前 N 张图像

- 五、系统异常状态恢复控制

- 六、完整代码展示

- 七、仿真代码展示

- 八、仿真波形展示

前言

上一节,我们已经完成了 OV5640 初始化逻辑的介绍。接下来,将要开始完成 DVP 接口的时序设计。

提示:以下是本篇文章正文内容,下面案例可供参考

一、DVP 接口时序逻辑设计

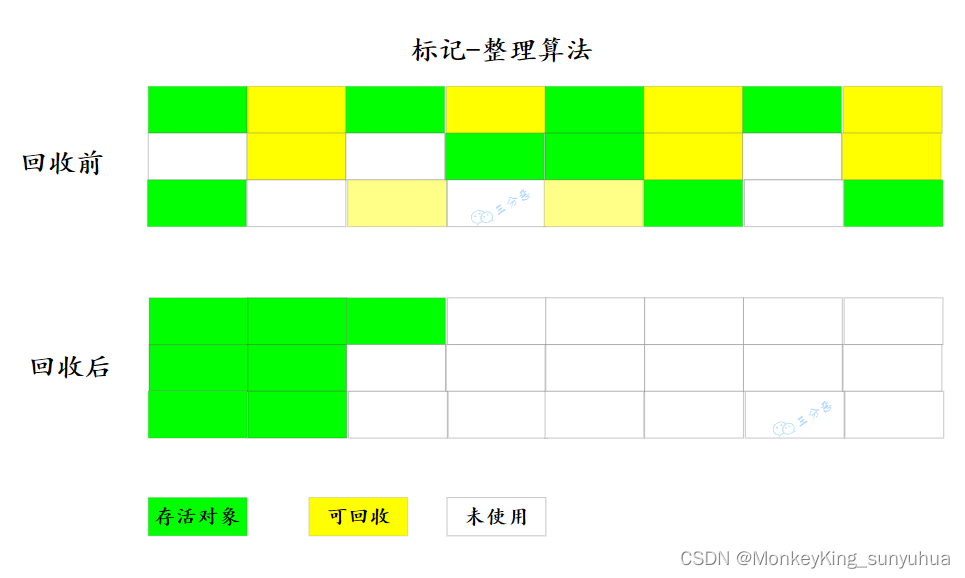

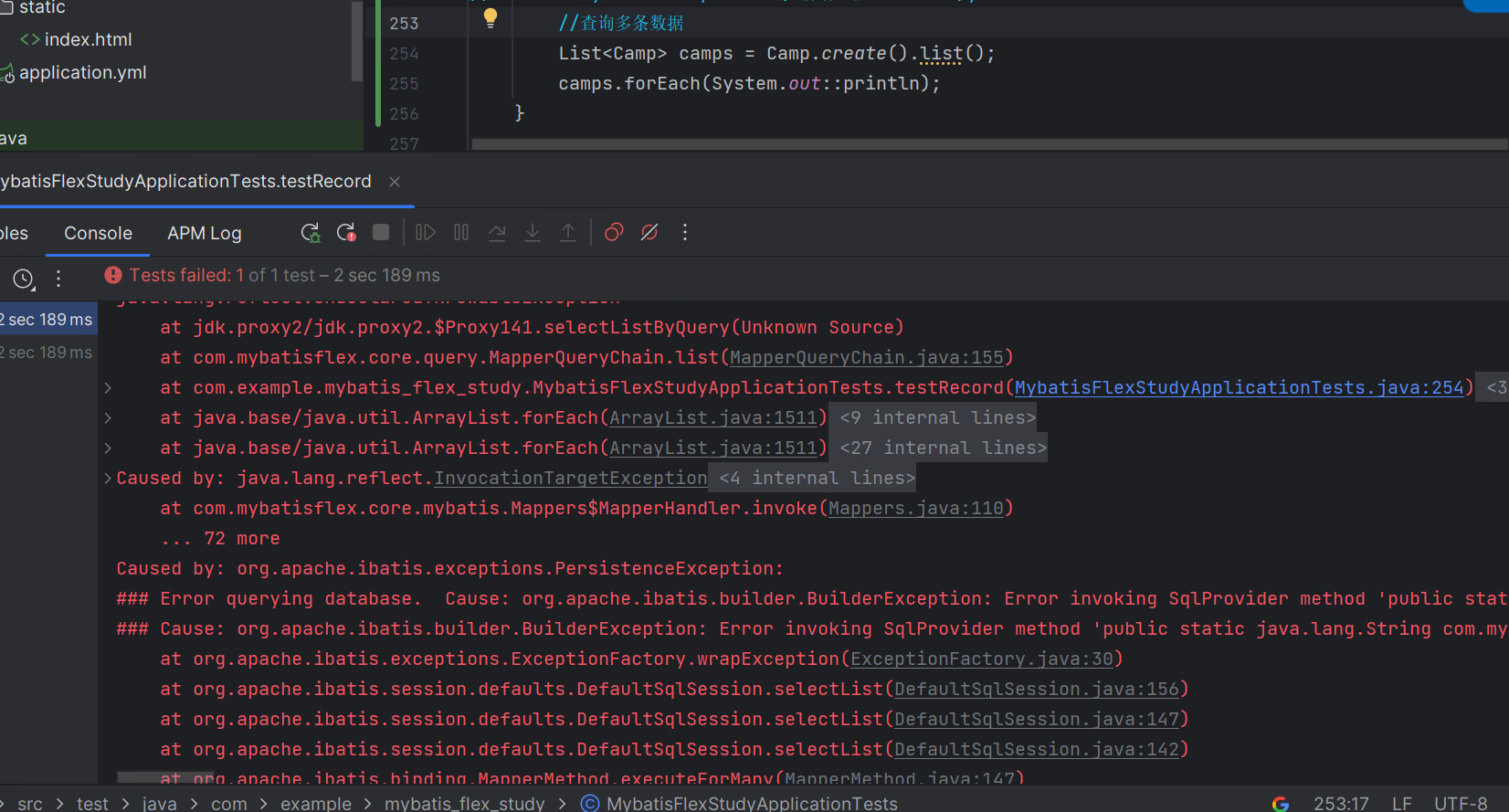

为了便于分析 DVP 接口。这里以 OV5640 输出 3*3 像素的图像大小矩阵为例绘制时序图,介绍 DVP 接口的时序,并分析接口逻辑设计方法。

特别说明:上图仅为时序示意图,其中 VSYNC 的高电平脉冲宽度,VSYNC 下降沿到 HREF

上升沿之间的间隔时钟个数,HREF 下降沿到下一个 HREF 的上升沿之间的高电平之间的时钟个数,以及最后一个 HREF 下降沿到 VSYNC 上升沿之间的间隔时钟个数实际上远大于图中所绘制,绘制时为了保证画幅大小和进行了精简,这些差异不影响我们分析 DVP 接口时序。

VSYNC 的高脉冲标志着新一帧图像数据的即将到来。所以当 VSYNC 高脉冲出现之后,第一个 HREF 高电平期间 DATA 端口上传输的就是整幅图像的第一行数据,紧接着第二行,直到最后一行输出完成,再产生 VSYNC 的高脉冲开始新一帧图像数据的输出。

HREF 上升沿后的第一个时钟时刻的数据为该行图像的第一个像素数据的高字节(P0H),第二个时钟时刻的数据为第一个像素数据的低字节(P0L),以此类推,直到第 2N 个数据为第 N 个像素数据的低字节,然后一行数据输出完成,HREF 变为低电平。间隔一定时钟周期后再开始下一行图像数据的输出。

Data 数据线上,PxH 和 PxL 两个 8 位的数据拼接为一个 RGB565 像素的图像数据。

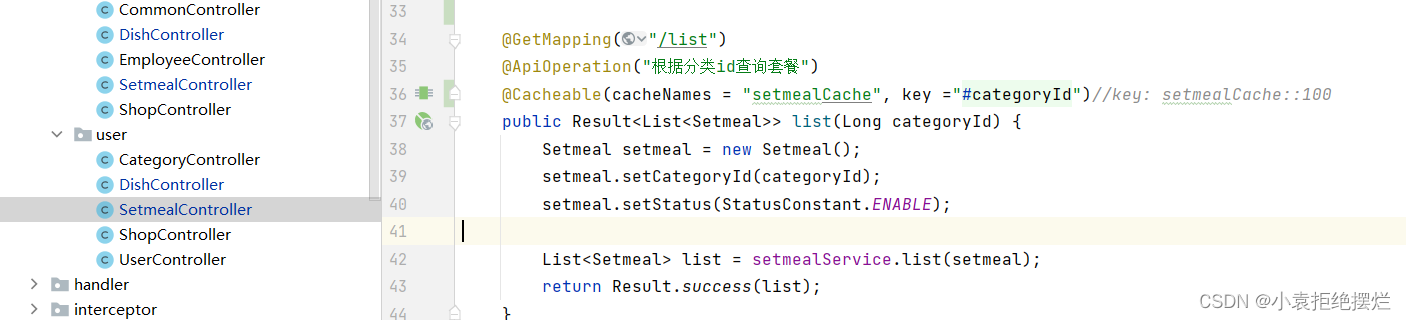

二、基本数据流接收

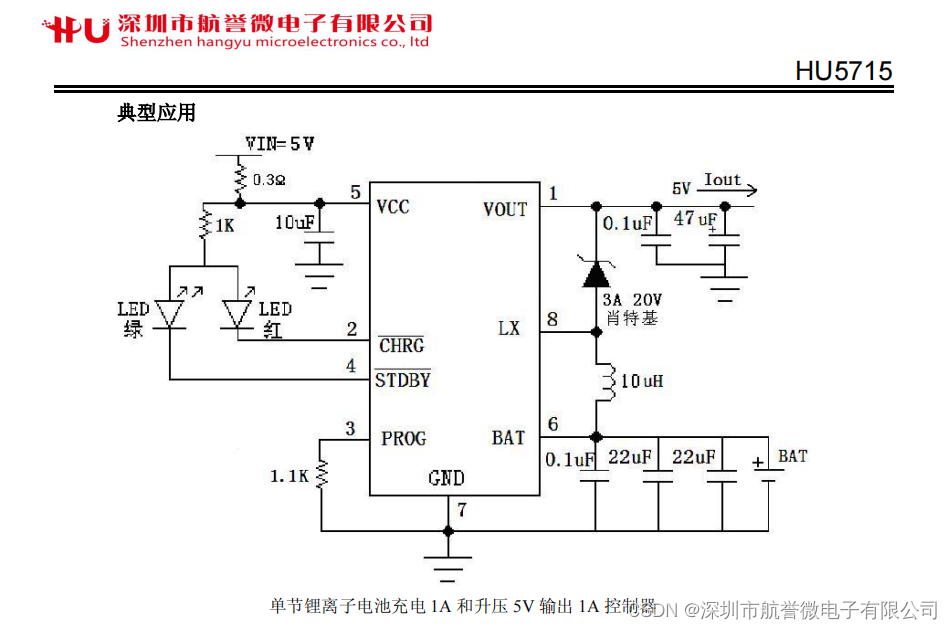

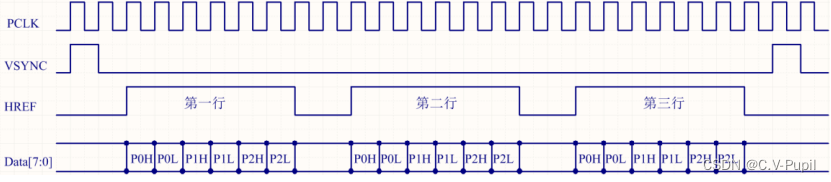

根据应用需求,整个 DVP Capture 模块的设计目的就是要实现每两个数据拼接为 1 个 16位的数据并按照写 RAM 或 FIFO 的接口形式输出,模块设计框图如下图所示:

模块中,DataPixel 为 16 位的 RGB565 格式的像素数据,由连续的 2 个 Data 数据拼接而来。DataValid 为 DataPixel 数据有效标志信号,由于 DATA 端口需要 2 个时钟才能传输一个像素所需的 16 位数据,所以 DataPixel 端口上的数据理论来说应该是每 2 个时钟周期只有一个时钟周期是真正有效的,所以 DataValid 在连续的两个时钟周期中,只有一个时钟周期为高电平,一个时钟周期为低电平,来确保下一级在使用 DataPixel 时,每两个时钟周期内只使用一次,使用时,如果是数据直接写入 FIFO 或者 RAM,可以直接将 DataValid 信号当做 wrreq信号使用。下图为该模块的时序图:

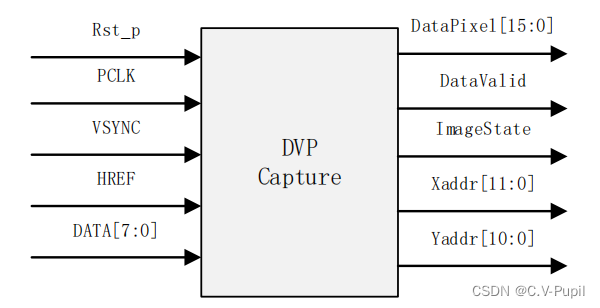

从图中可以看到,DataPixel 的数据在 DataValid 信号为高电平的时候,输出的是前两个时钟周期的值拼接成的。如 C1 和 C2 组成一个 16 位的数据,在 C2 之后延迟两个数据输出在 DataPixel 端口上。这样就完成了 DVP 接口数据流转 RGB565 数据流的功能。

//在HREF为高电平时,计数输出数据个数

always@(posedge PCLK or posedge Rst_p)

if(Rst_p)

Hcount <= 0;

else if(r_Href)

Hcount <= Hcount + 1'd1;

else

Hcount <= 0;

//-----------------------------------------------------------------------------------------

//-----------------------------------------------------------------------------------------

/*根据计数器的计数值奇数和偶数的区别,在计数器为偶数时,将DVP接口数据端口上的数据存到输出

像素数据的高字节,在计数器为奇数时,将DVP接口数据端口上的数据存到输出像素数据的低字节*/

always@(posedge PCLK or posedge Rst_p)

if(Rst_p)

r_DataPixel <= 0;

else if(!Hcount[0])

r_DataPixel[15:8] <= r_Data;

else

r_DataPixel[7:0] <= r_Data;

//-----------------------------------------------------------------------------------------

三、像素位置输出

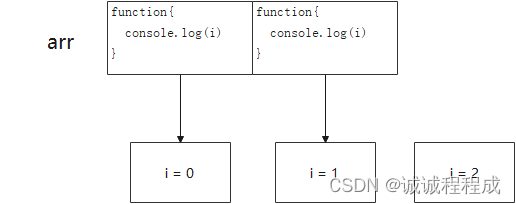

在有些应用中,需要实时知道当前输出的图像数据在输出像素矩阵中的绝对位置,以便于根据不同的位置进行不同的处理。最典型的如使用图像处理技术定位图像中某个点的具体位置。则需要用到该信息,因此,该 DVP Capture 模块也将每个像素对应的位置通过 Xaddr和 Yaddr 两个端口输出。在上图中以 C1C2 这个数据为例,可以看到,在 DataValid 为高电平的时候,数据位 C1C2,而此时的 Xaddr 也为 1。每当 DataValid 高电平信号到来时,Xaddr 的值加 1。当一行图像数据输出完成之后,Xaddr 清零。

Xaddr 和 Yaddr 的生成非常简单。对于 Xaddr 来说,只要设计一个 Hcount 计数器,在HREF 为高电平期间持续计数即可,然后舍去将 Hcount 的最低位得到的值就刚好可以与像素输出时刻一一对应。而对于 Yaddr,则只需要使用一个 Vcount 计数器对 HREF 的上升沿进行计数即可。关于该部分实现的具体细节详见提供的设计代码的完整内容。需要关注的是,在模块中,Xaddr 和 Yaddr 都是从 1 开始算的,并非从 0 开始,也就是说,输出的每行最开头的一个像素对应的 Xaddr 的值为 1,输出的每帧图像的第一行数据,其 Yaddr 的值也为 1。

//-----------------------------------------------------------------------------------------

/*在行计数器计数值为奇数,且HREF高电平期间,产生输出数据有效信号*/

always@(posedge PCLK or posedge Rst_p)

if(Rst_p