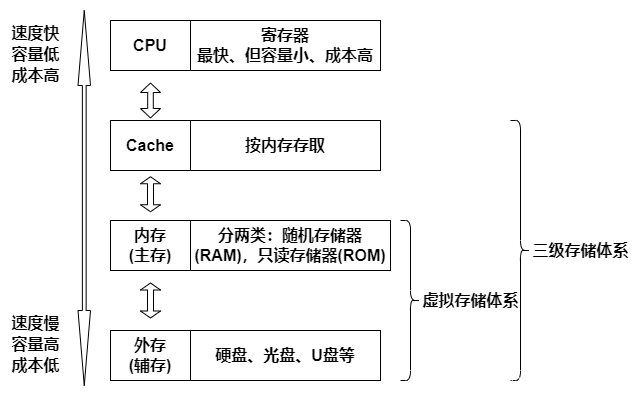

1.层次化存储体系

1.1层次化存储结构

局部性原理是层次化存储结构的支持

时空局部性:刚被访问的内容,立即又被访问(eg: 循环体 )

空间局部性:刚被访问的内容,临近的空间很快被访问(eg:数组)

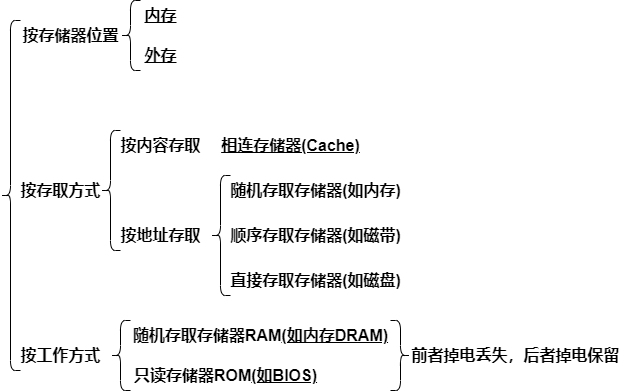

1.2层次化存储结构的分类

DRAM:动态随机存取存储器

SRAM:静态随机存取存储器

Cache:高速缓存

EEPROM:电可擦可编程只读存储器

2.Cache

2.1概念

(1)在计算机的存储系统体系中,Cache是访问速度最快的层次(若有寄存器,则寄存器最快)

注:前者是对于三级存储体系而言,后者是对于整个存储体系而言

(2)使用Cache改善系统性能的依据是程序的局部性原理(时间局部性和空间局部性)

2.2映像

2.2.1概念

(1)地址映像是将主存与Cache的存储空间划分为若干大小相同的页(或称为块)。

例如,某机的主存容量为I GB,划分为2048页,每页512 KB;Cache容量为8 MB,划分为16页,每页512 KB。

(2)如果以h代表对Cache的访问命中率,t 1表示Cache的周期时间,t 2表示主存储器周期时间,以读操作为例,使用"Cache+主存储器”的系统的平均周期为t 3,则:

t3=h * t1+(1-h) * t2

其中,(1-h)又称为失效率(未命中率)。

2.2.2分类

直接相联映像:硬件电路较简单,但冲突率很高。

全相联映像:电路难于设计和实现,只适用于小容量的cache,冲突率较低。

组相联映像:直接相联与全相联的折中。

注:主存与Cache之间的地址映射由硬件直接完成。

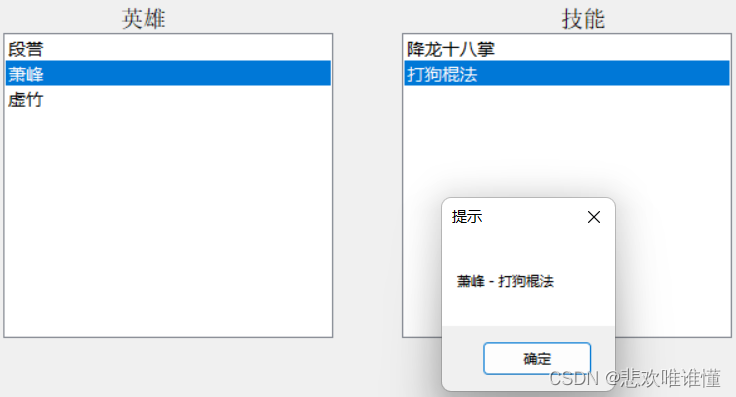

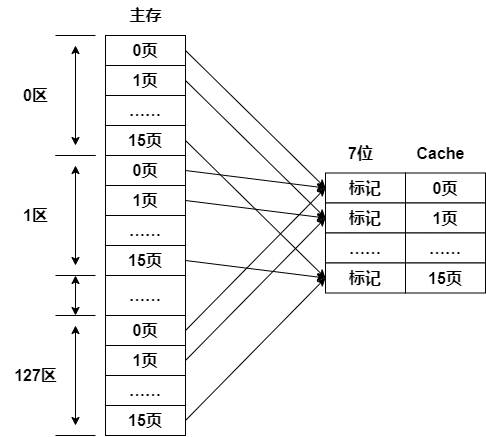

2.2.3不同映像的图解(帮助理解,不考)

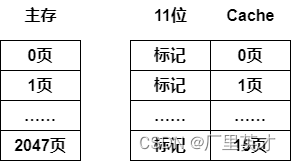

(1)直接相联映像

其中主存中的每个区中的x页只能对应Cache中的x页,一旦Cache中的x页被主存中某一区的x页占据,那么其它区的x页就会与之冲突,所以冲率很高,结构简单

(2)全相联映像

主存中任意页可以与Cache中任意页对应,所以冲突率低,但电路复杂

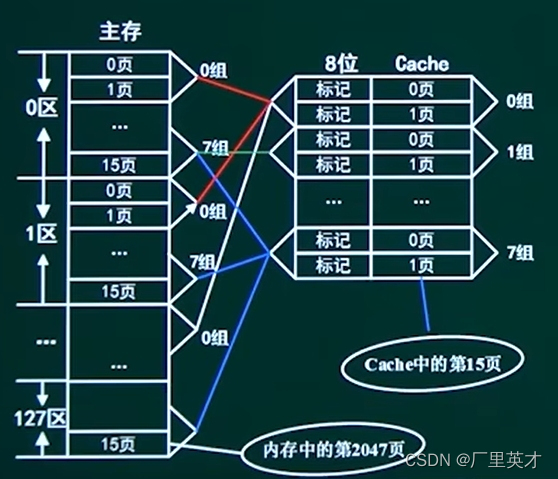

(3)组相联映像

该图片来自希赛软考

对主存和Cache都进行了分组,每个区的x组只能与Cache中的x组对应,但是一个组的页可以任意对应。就是前两者的缝合怪,冲突率和复杂性都属于中庸

3.主存编址方法

3.1计算公式

(1)存储单元

存储单元个数 = 最大地址 - 最小地址 + 1

(2)编址内容

按字编址:存储体的存储单元是字存储单元,即最小寻址单位是一个字(该字的字长题目会给出)

按字节编址(默认):存储体的存储单元是字节存储单元,即最小寻址单位是一个字节(字节的字长固定为8个bit)

(3)总容量 = 存储单元个数 * 编址内容

(4)总片数 = 总容量/每片容量

3.2补充内容

1 K = 2 ^ 10

1 M = 2 ^ 20

1 G = 2 ^ 30

声明:笔记内容参考自希赛软考

上一篇:软件设计师学习笔记5-流水线技术