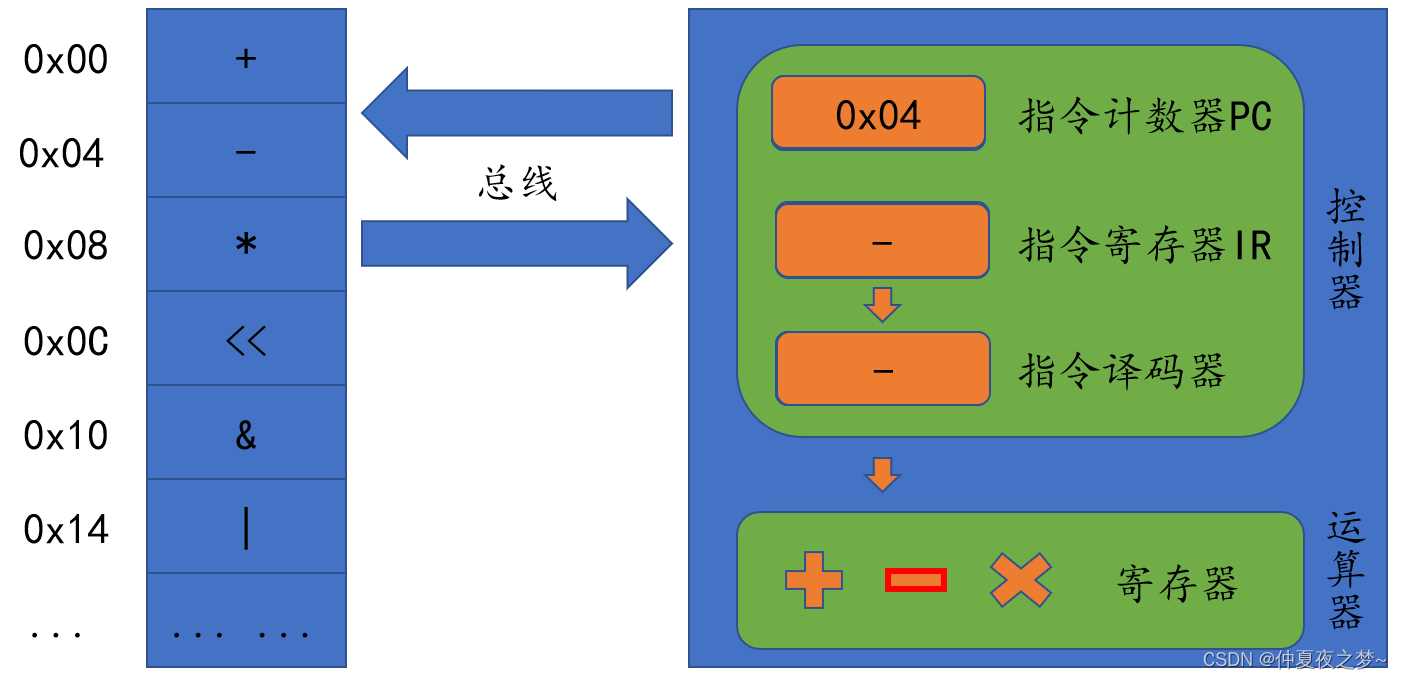

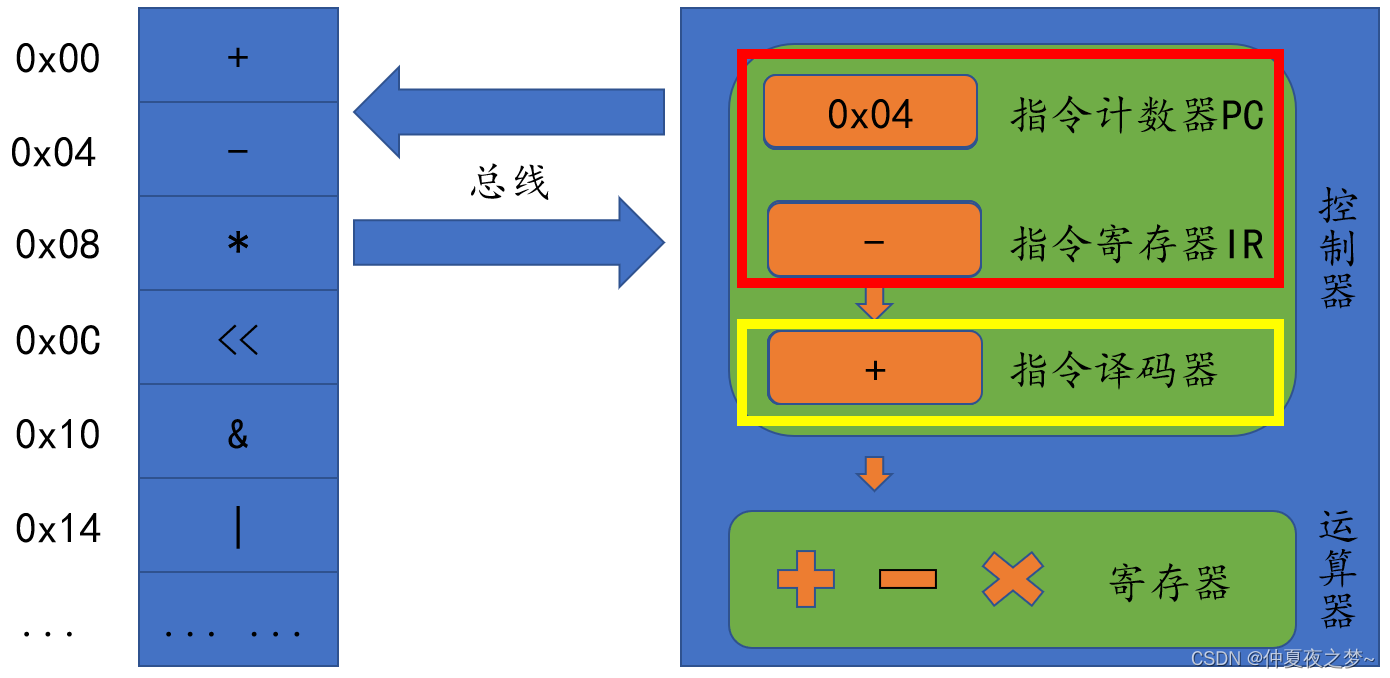

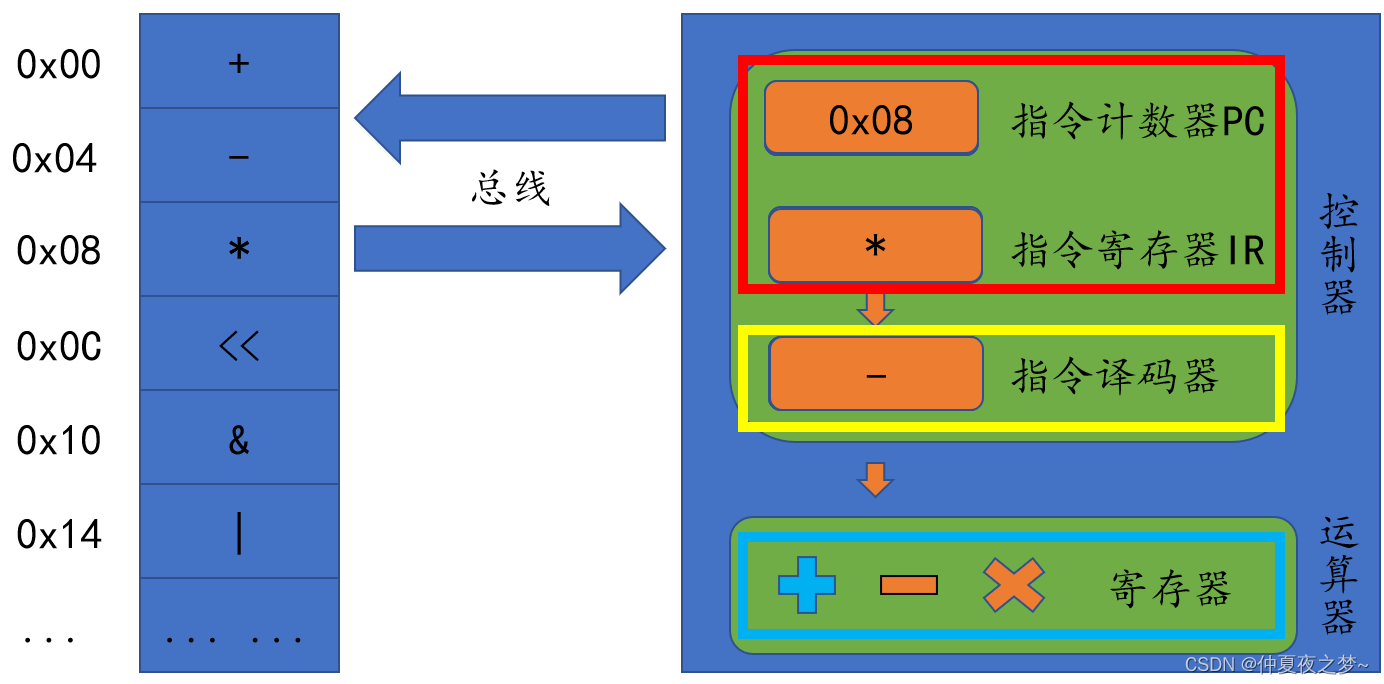

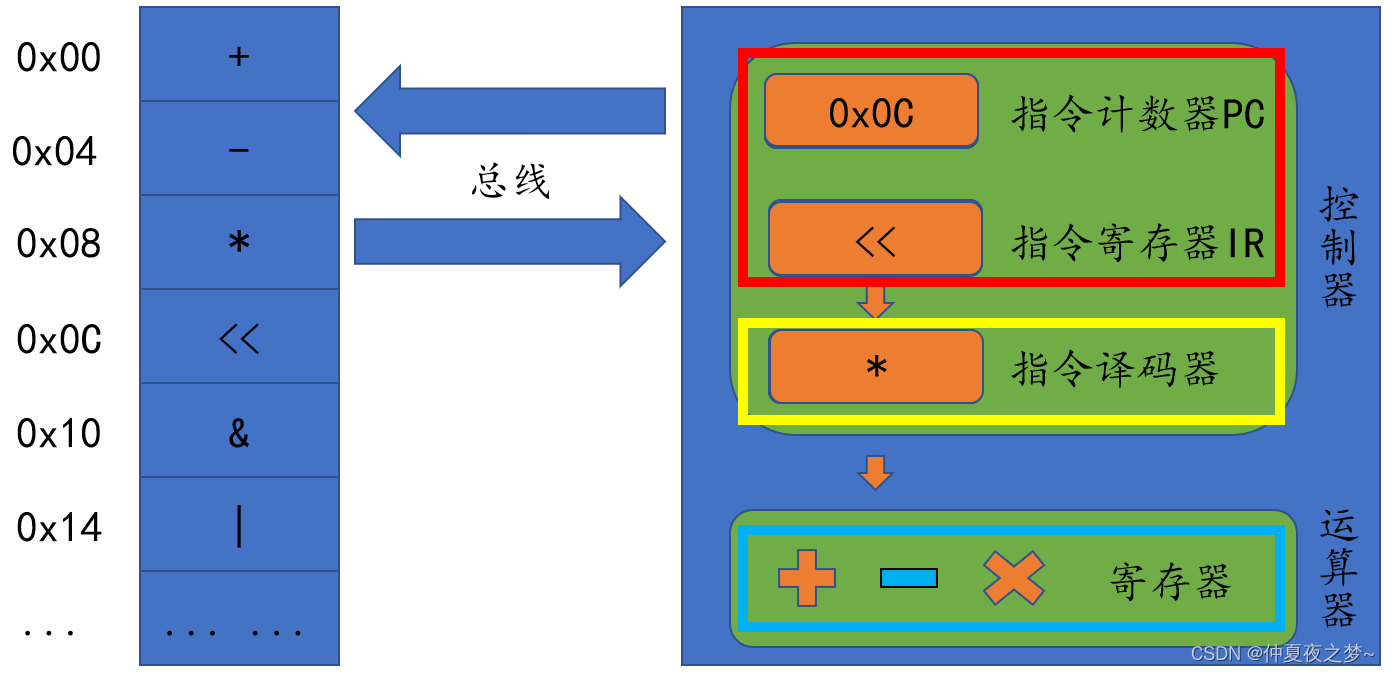

CPU要执行某一个指令,第一步,PC给内存发送地址,IR接收内存返回的指令;第二步,指令译码器解析IR中的指令;第三步,寄存器执行译码结果对应的运算单元。

实际上,译码器在译码的时候,PC就啥都不干吗,很显然不是,这个时候PC就会自增4来准备取下一条指令。下面我们先通过工厂流水线运作的例子,来初步理解流水线的运作过程。

目录

一、工厂多级流水线理解

1、一级流水线

2、 三级流水线

二、指令流水线

1、三级指令流水线的运作流程

2、指令流水线的发展以及存在的局限性

一、工厂多级流水线理解

每一个货物的处理包含了三个步骤:组装、包装、装箱

1、一级流水线

一级流水线其实就是只有一个工人,那就说明一个工人要干三个工作,这个时候只能按照组装、包装、装箱的步骤来进行。

第1s,工人组装第一个货物;

第2s,工人包装第一个货物;

第3s,工人装箱第一个货物;

第4s,工人开始组装第二个货物;

... ...

无论哪个时刻,每1s都只能干一件事。

2、 三级流水线

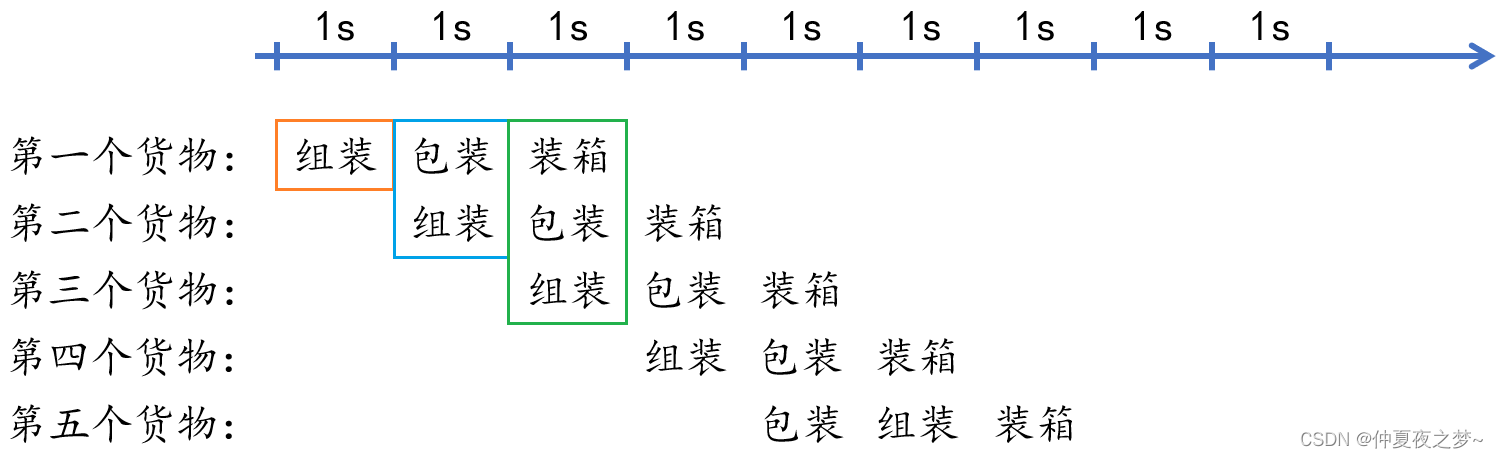

三级流水线其实就是每一步都分配了一个工人,工人A负责组装,工人B负责包装,工人C负责装箱

第1s,工人A先组装第一个货物;

第2s,工人B接着包装第一个货物,这时工人A开始组装第二个货物;

第3s,工人C装箱第一个货物,工人B开始包装第二个货物,工人A开始组装第三个货物;

第4s,工人C装箱第二个货物,工人B开始包装第三个货物,工人A开始组装第四个货物;

... ...

大概2s以后,每1s的时间里都有三件事在同时处理,这就是流水线的基本理念。

二、指令流水线

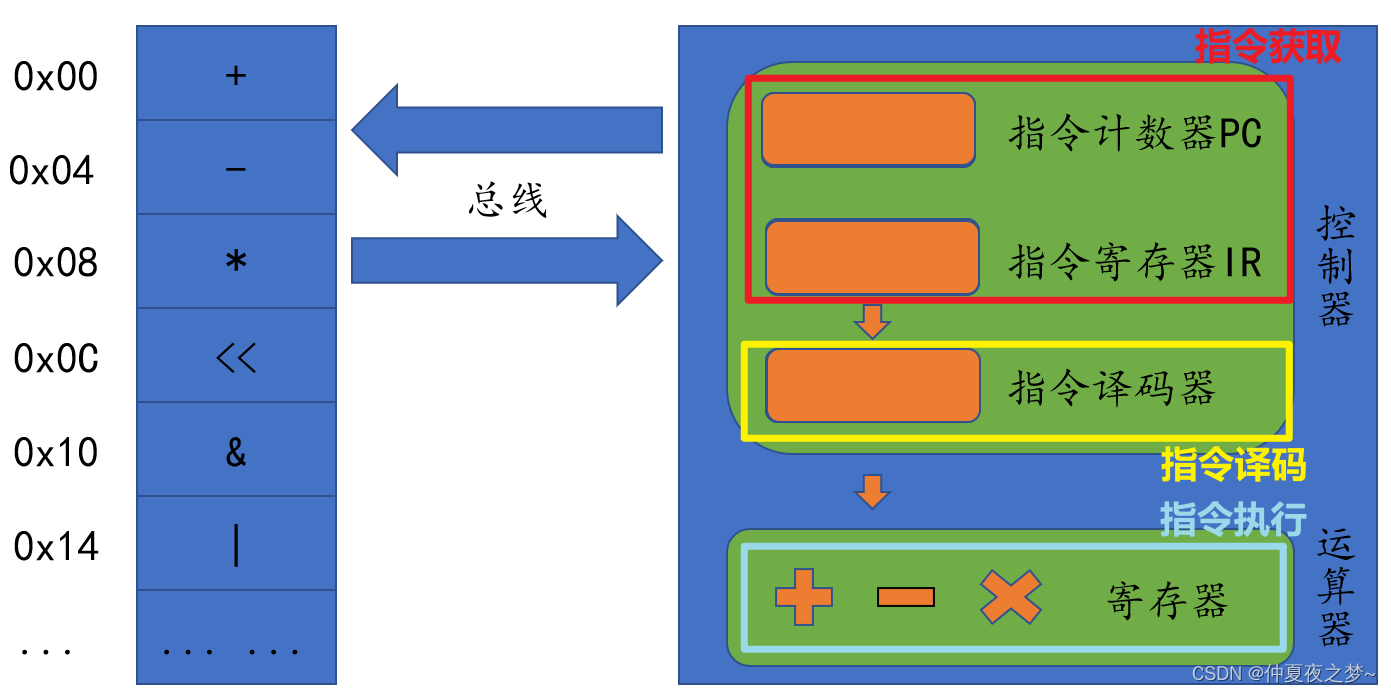

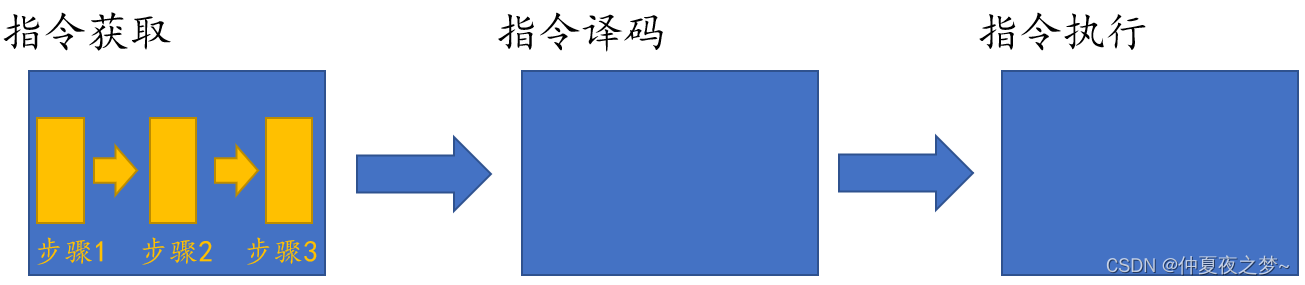

类比上面的工厂流水线,CPU处理指令也可以大致分成三步,指令获取、指令译码、指令执行。下面我们直接介绍指令三级流水线。

1、三级指令流水线的运作流程

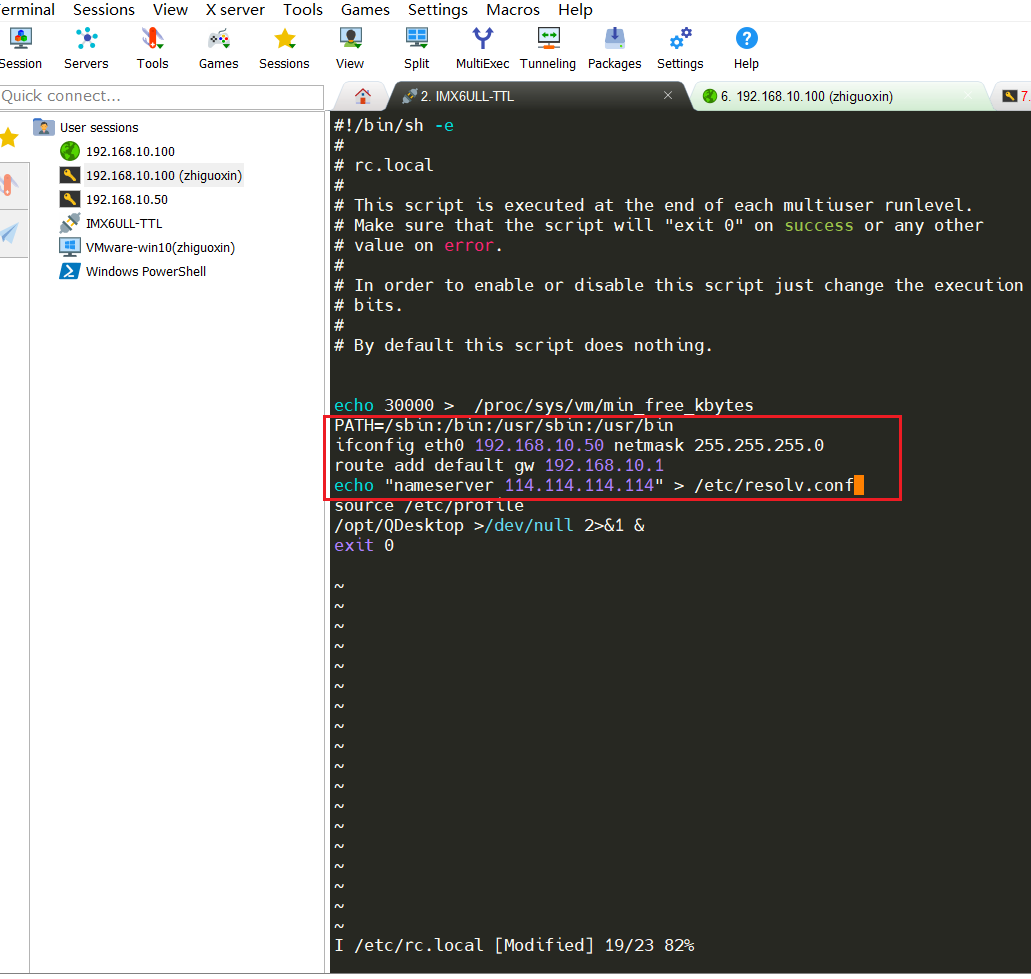

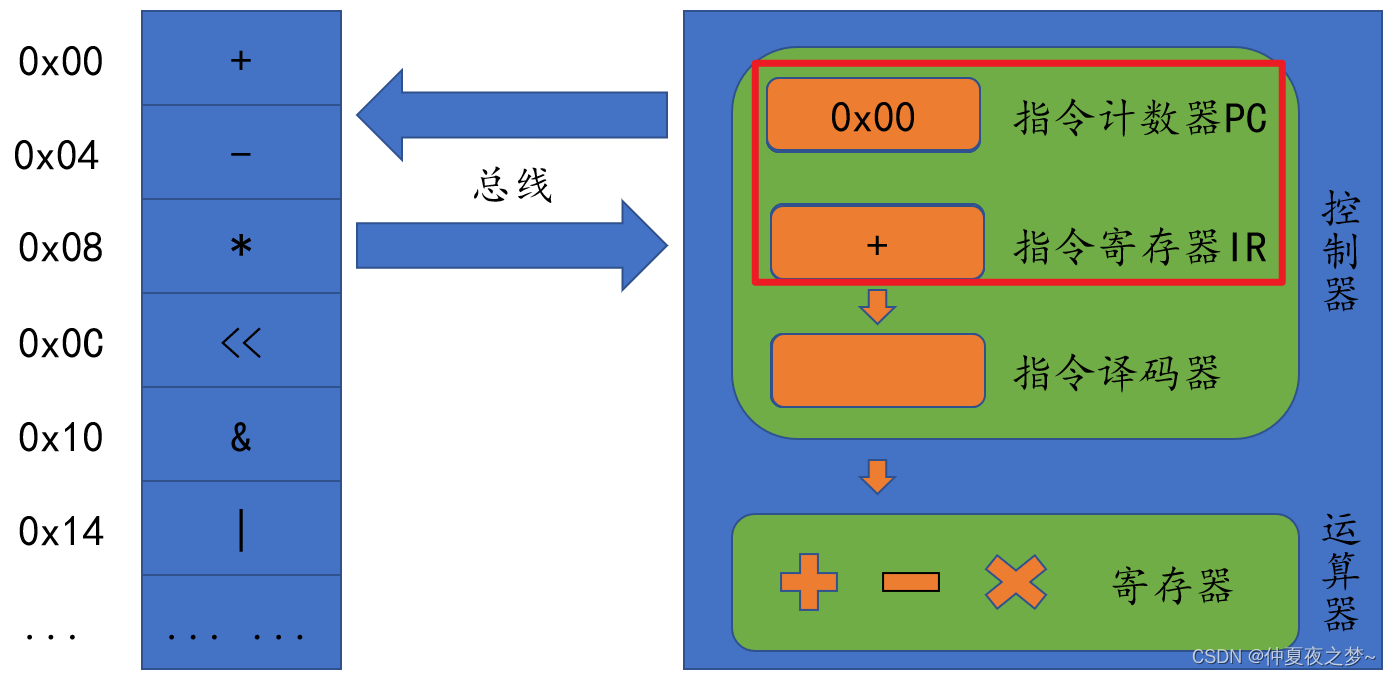

第1s,PC发送0x00地址,获取到的地址保存到IR。

第2s,指令译码器解析第一条指令,此时PC开始获取第二条指令。

第3s,运算器执行第一条指令,译码器解析第二条指令,PC获取第三条指令。

第4s,运算器执行第二条指令,译码器解析第三条指令,PC获取第四条指令。

2、指令流水线的发展以及存在的局限性

(1) 流水线的发展

ARM7采用 3 级流水线

ARM9采用 5 级流水线

Cortex-A9采用 8 级流水线

注意:虽然流水线的级数越来越多,本质还是三级流水线,只不过是在三级流水线的基础上进行了细分。

(2) 流水线的局限性

指令流水线机制的引入确实可以大大提升指令执行的速度,但是在实际执行程序的过程中,很多情况下流水线是无法形成的。比如异常发生时,处理器要切换模式,保存上下文内容,然后跳转异常处理程序,在开始执行处理程序之前,流水线都无法正常运作。

因此,流水线的引入只能是优化了原本的流程,流水线的级数也不能太多,流水线级数越多,芯片设计的复杂程度也越高,芯片的功耗也越高。