目录

- 概述

- 实现方法

- GPIO 及其复用功能

- AFIO 的寄存器实现

- 重映射的功能限制

概述

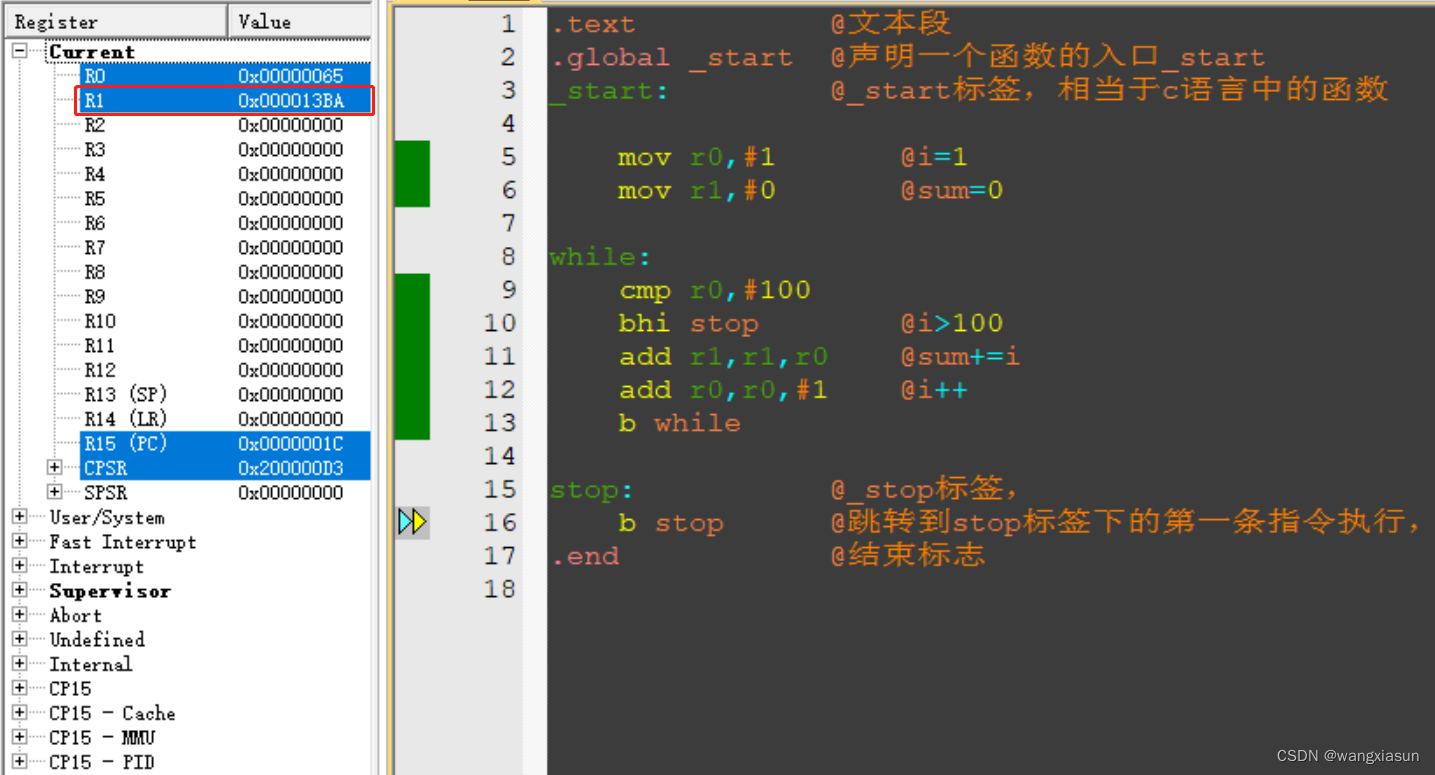

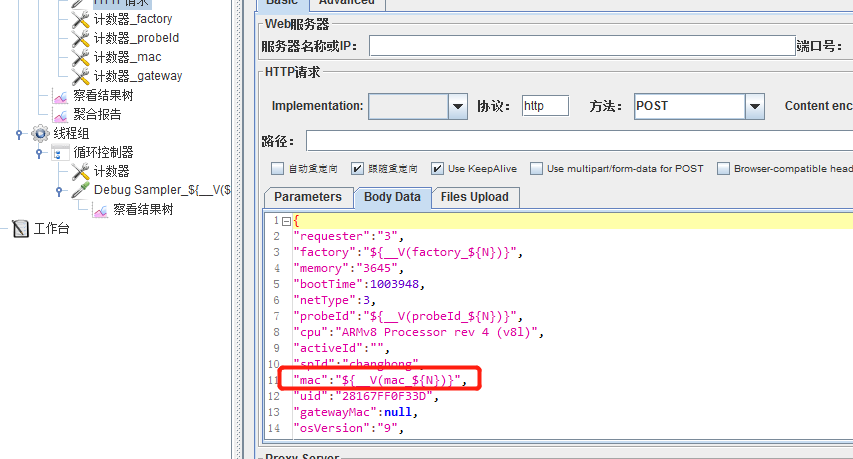

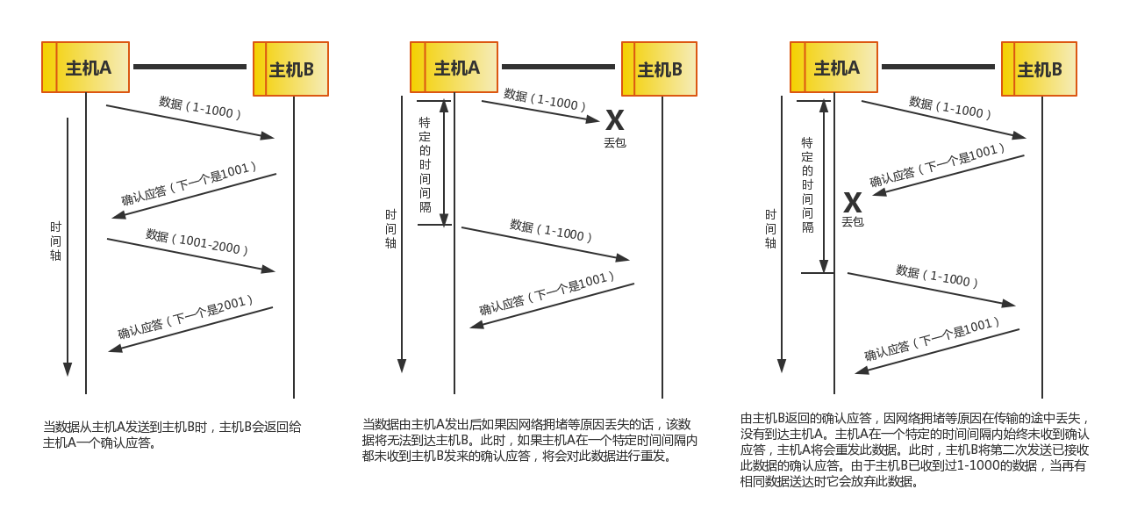

在ch32V2xx系列处理器中,芯片引脚数从28到68不等,分为几个系列,不同型号之间外设资源有差异,所以,引脚复用和重映射功能 也不一样,在前文的USARTx_CFG(void)函数中,对串口USART1的初始化中,我们已经使用了映射功能,方式为:

GPIO_PinRemapConfig(GPIO_Remap_USART1, ENABLE);

该变量复位后默认的串口管脚配置,就是一个典型的重映射应用。比较常用的adc,定时器和USART 为例,ch32V2xx系列处理器的映射关系如下:

实现方法

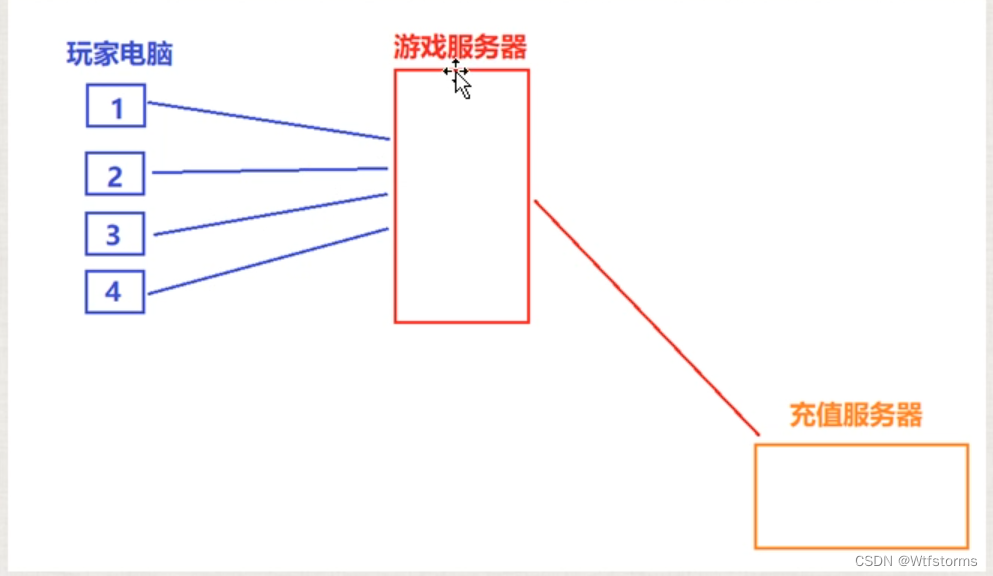

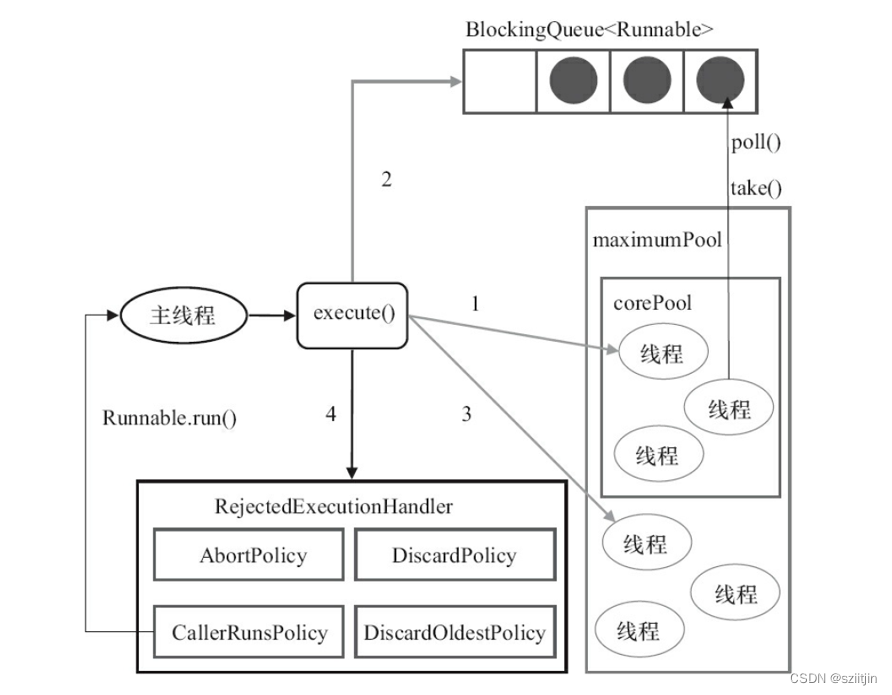

ch32V2xx系列处理器许多引脚拥有复用功能,很多其他的外设把自己的输出和输入通道映射到这些引脚上,实现方法有:

GPIO 及其复用功能

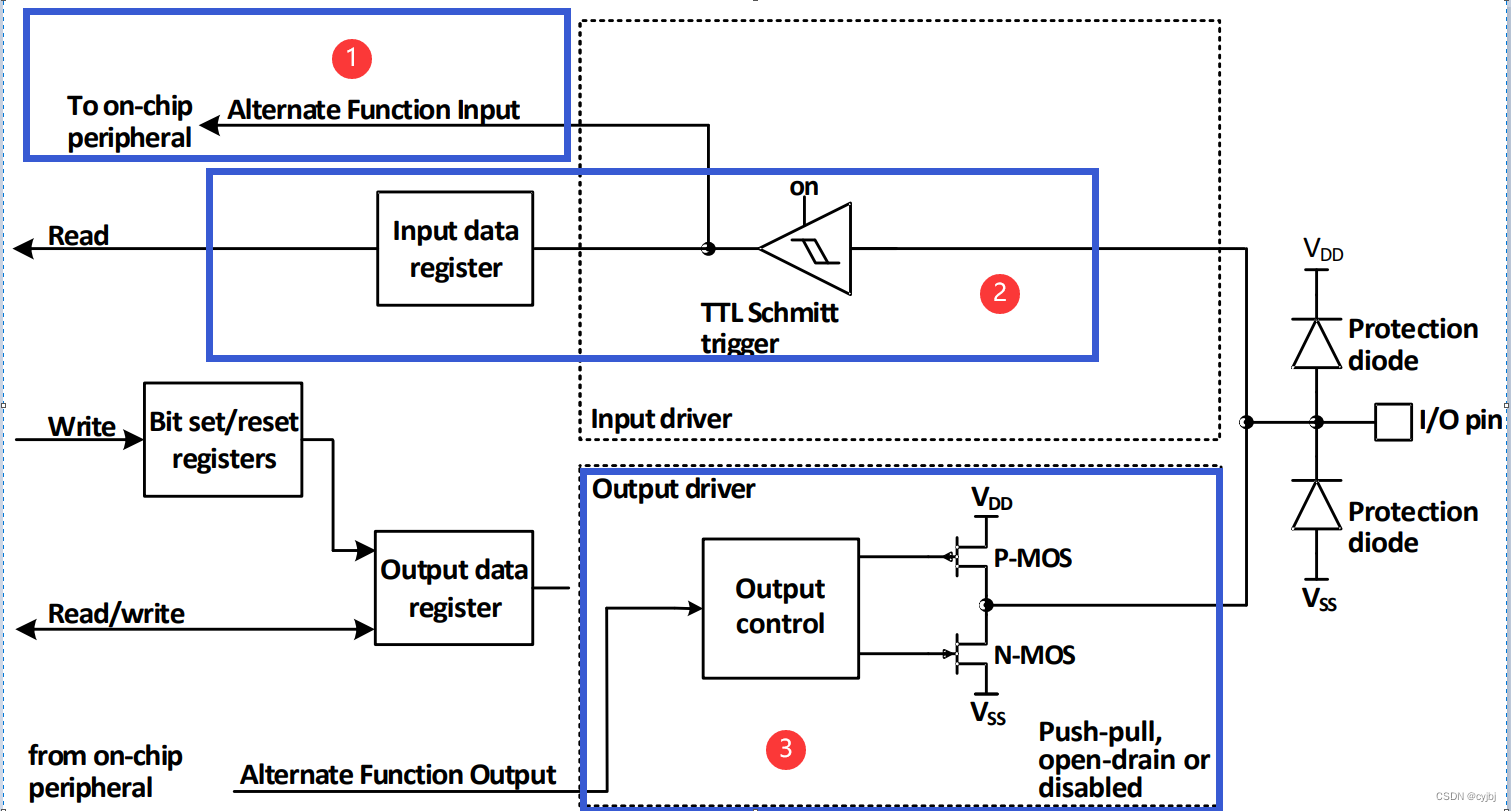

为了丰富处理器的功能,增强设计的灵活性,GPIO 模块被设计成兼容输入(包括模拟和数字)和输出复用功能,复用被其他外设复用时的结构框图如下:

其中,1为模拟输入,2为逻辑输入,3为逻辑输出功能,启用输出的复用功能时,输出驱动器被使能,可以进一步按需要被配置成开漏或推挽模式,施密特触发器也被打开。

其中,1为模拟输入,2为逻辑输入,3为逻辑输出功能,启用输出的复用功能时,输出驱动器被使能,可以进一步按需要被配置成开漏或推挽模式,施密特触发器也被打开。

复用为输入是,输出数据寄存器被断开,出现在 IO 引脚上的电平将会在每个 APB2 时钟被采样到输入数据寄存器,在开漏模式下,读取输入数据寄存器将会得到 IO 口当前状态;在推挽模式下,读取输出数据寄存器将会得到最后一次写入的值。启用模拟输入时,不仅输出缓冲器被断开,输入驱动中施密特触发器的输入被禁止以防止产生 IO口上的消耗,上下拉电阻也会被禁止。

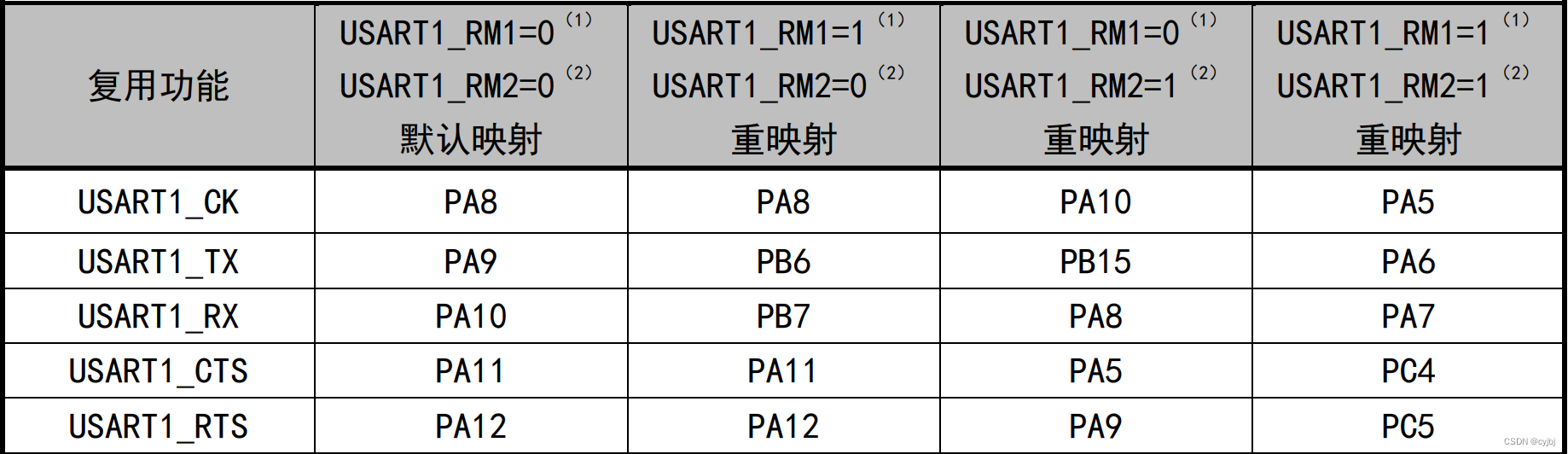

通过这些复用功能,GPIO就可以灵活配置为通用IO,模拟输入、定时器输出、捕获输入,USART的rx或tx等。例如,对USART的TX,RX,RTS,CTS,CK等,对应的GPIO重映射配置为:

以USAET1为例,对应的可以重映射后服用的管脚见下表:

以USAET1为例,对应的可以重映射后服用的管脚见下表:

通过配置USART1_RM1 和USART1_RM2 为 AFIO_PCFR2 即可USART配置不同的映射管脚。

通过配置USART1_RM1 和USART1_RM2 为 AFIO_PCFR2 即可USART配置不同的映射管脚。

AFIO 的寄存器实现

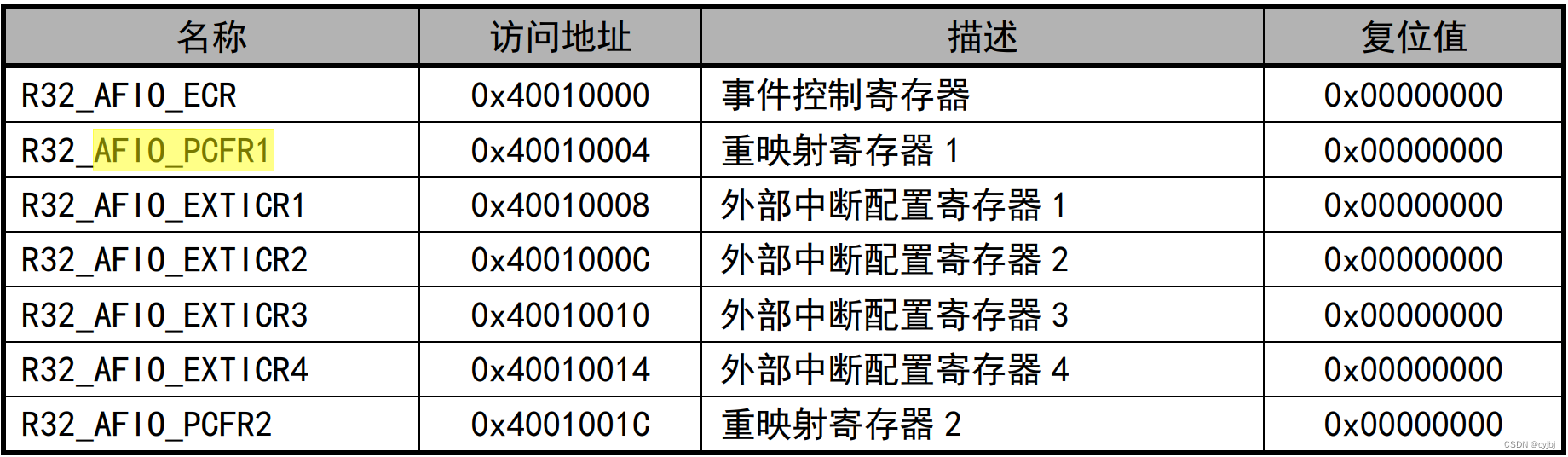

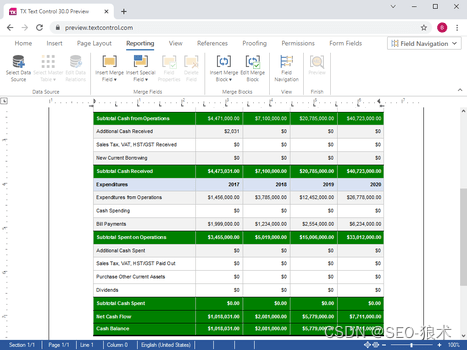

前面我们知道了,usart1的复用配置是通过USART1_RM1 和USART1_RM2 为 AFIO_PCFR2来实现的,ch32V2xx系列处理器对重映射都是通过AFIO 相关寄存器实现的,列表如下:

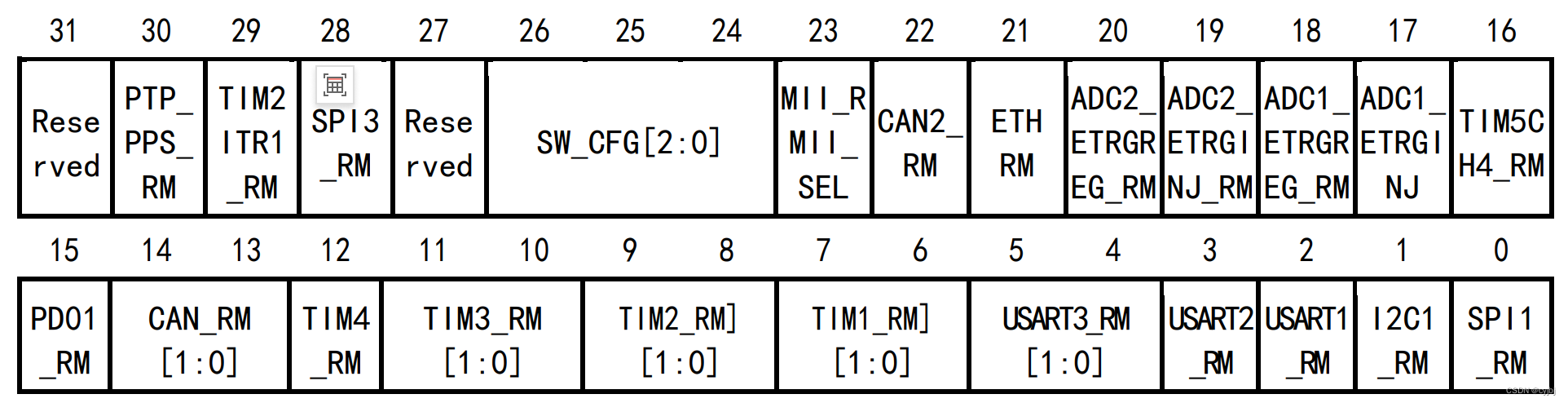

其中,AFIO_PCFR1的定义如下:

其中,AFIO_PCFR1的定义如下:

可以看到,bit2正是USART1_RM1的位置,再配合 AFIO_PCFR2 寄存器 bit26 USART1_RM2 使用,实现了对usart1的复用配置,指令如下:

可以看到,bit2正是USART1_RM1的位置,再配合 AFIO_PCFR2 寄存器 bit26 USART1_RM2 使用,实现了对usart1的复用配置,指令如下:

GPIO_PinRemapConfig(GPIO_Remap_USART1, ENABLE);

重映射的功能限制

需要注意的是,重映射关系受限于管脚资源,封装管脚资源越少的规格,重映射越少,甚至不能重映射,例如OSC_IN/OSC_OUT 可以用做 GPIO 的 PD0/PD1,通过设置重映射寄存器 1(AFIO_PCFR1)实现。 这个重映射只适用于 20、32、48 和 64 脚的封装,但 CH32V203RBT6 只有 OSC_IN 和 OSC_OUT 功能脚,不支持映射(对于 LQFP100 封装,由于 PD0 和 PD1 为固有的功能引脚,因此没有必要 再由软件进行重映像设置。)

在定时器复用功能重映射的TIM1_RM=11 完全映射,仅 LQFP100 封装,支持该位重映射功能。TIM3_RM=11 完全映射,对64 脚以下封装不支持该位映射,等等不止这些,用户在使用对应封装的cpu处理器之前,需要对照datasheet仔细确认,以免造成设计失误。

![NLP文本匹配任务Text Matching [无监督训练]:SimCSE、ESimCSE、DiffCSE 项目实践](https://img-blog.csdnimg.cn/img_convert/44d419b05793d534eec259bf37dde5f9.png)