引言

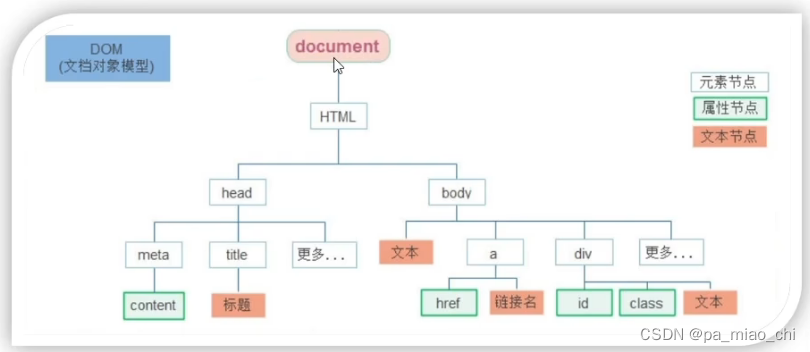

FPGA(现场可编程门阵列)是一种可编程逻辑器件,具有灵活性和可重构性,广泛用于数字电路设计和嵌入式系统开发。在FPGA中,FIFO(First-In, First-Out)是一种常见的存储器结构,用于在不同的时钟域之间进行数据传输和缓冲。FPGA中的FIFO通常由双端口内存实现,其中一个端口用于读取数据,另一个端口用于写入数据。FIFO内部有一个读指针和一个写指针,用于指示下一个要读取或写入的位置。当数据被写入FIFO时,写指针向前移动;当数据被读取时,读指针向前移动。这样,保证了先进先出的数据顺序。FIFO在FPGA中的应用非常广泛,特别是在数据流处理、通信接口、高速数据采集等领域。它可以解决不同时钟域之间的数据传输问题,同时还可以提供缓冲功能,使得数据传输能够以合适的速度进行,从而避免数据丢失或过载。FPGA厂商通常提供了各种类型和大小的FIFO IP核(知识产权核),可以方便地集成到设计中。此外,FPGA开发工具也提供了相应的设计工具和资源,以简化FIFO的使用和配置。

原理

-

内部存储器:FIFO由一个内部存储器组成,通常是一个双端口的存储器。一个端口用于写入数据,另一个端口用于读取数据。

-

写指针和读指针:FIFO内部有两个指针,一个是写指针,用于指示下一个要写入数据的位置;另一个是读指针,用于指示下一个要读取数据的位置。

-

写入数据:当有新的数据要写入FIFO时,写指针会向前移动到下一个可用的位置,并将数据写入该位置。

-

读取数据:当需要读取FIFO中的数据时,读指针会向前移动到下一个要读取的位置,并将该位置的数据输出。

-

先进先出:由于写指针和读指针的移动顺序是固定的,FIFO保证了写入FIFO的数据按照它们的顺序被读取,即先进先出。

-

缓冲和流量控制:FIFO提供了临时存储功能,可以用于缓冲数据,以适应不同时钟域之间的数据传输速率差异。它还可以用于流量控制,当写入方和读取方的速率不匹配时,FIFO可以缓冲数据以平衡传传输。

软核开发

module fifo_core(

input wire clk,

input wire rst,

input wire wr_en,

input wire rd_en,

input wire [DATA_WIDTH-1:0] data_in,

output wire [DATA_WIDTH-1:0] data_out,

output wire fifo_empty,

output wire fifo_full

);

parameter DEPTH = 16; // FIFO深度

parameter DATA_WIDTH = 8; // FIFO数据宽度

reg [DATA_WIDTH-1:0] fifo[DEPTH-1:0];

reg [DEPTH-1:0] wr_ptr, rd_ptr;

reg [DATA_WIDTH-1:0] data_out_reg;

reg fifo_empty_reg, fifo_full_reg;

always @(posedge clk) begin

if (rst) begin

wr_ptr <= 0;

rd_ptr <= 0;

fifo_empty_reg <= 1;

fifo_full_reg <= 0;

data_out_reg <= 0;

end else begin

if (wr_en && !fifo_full_reg) begin

fifo[wr_ptr] <= data_in;

wr_ptr <= wr_ptr + 1;

if (wr_ptr == DEPTH - 1)

wr_ptr <= 0;

if (wr_ptr == rd_ptr)

fifo_full_reg <= 1;

fifo_empty_reg <= 0;

end

if (rd_en && !fifo_empty_reg) begin

data_out_reg <= fifo[rd_ptr];

rd_ptr <= rd_ptr + 1;

if (rd_ptr == DEPTH - 1)

rd_ptr <= 0;

if (rd_ptr == wr_ptr)

fifo_empty_reg <= 1;

fifo_full_reg <= 0;

end

end

end

assign data_out = data_out_reg;

assign fifo_empty = fifo_empty_reg;

assign fifo_full = fifo_full_reg;

endmodule

以上示例是一个简单的FIFO软核程序,具有16深度(DEPTH)和8位数据宽度(DATA_WIDTH)。它包含了时钟(clk)和复位(rst)输入信号,以及写使能(wr_en)和读使能(rd_en)输入信号。数据输入(data_in)和数据输出(data_out)信号用于写入和读取数据。此外,还有fifo_empty和fifo_full信号用于指示FIFO是否为空或已满。在always块中,根据时钟上升沿进行FIFO的写入和读取操作。当rst为1时,FIFO被复位,指针和状态寄存器被重置为初始值。当wr_en为1且FIFO不满时,将数据写入FIFO并更新写指针。当rd_en为1且FIFO不为空时,从FIFO读取数据并更新读指针。同时更新FIFO的空和满状态。最后,使用assign语句将data_out_reg、fifo_empty_reg和fifo_full_reg分配给对应的输出信号。

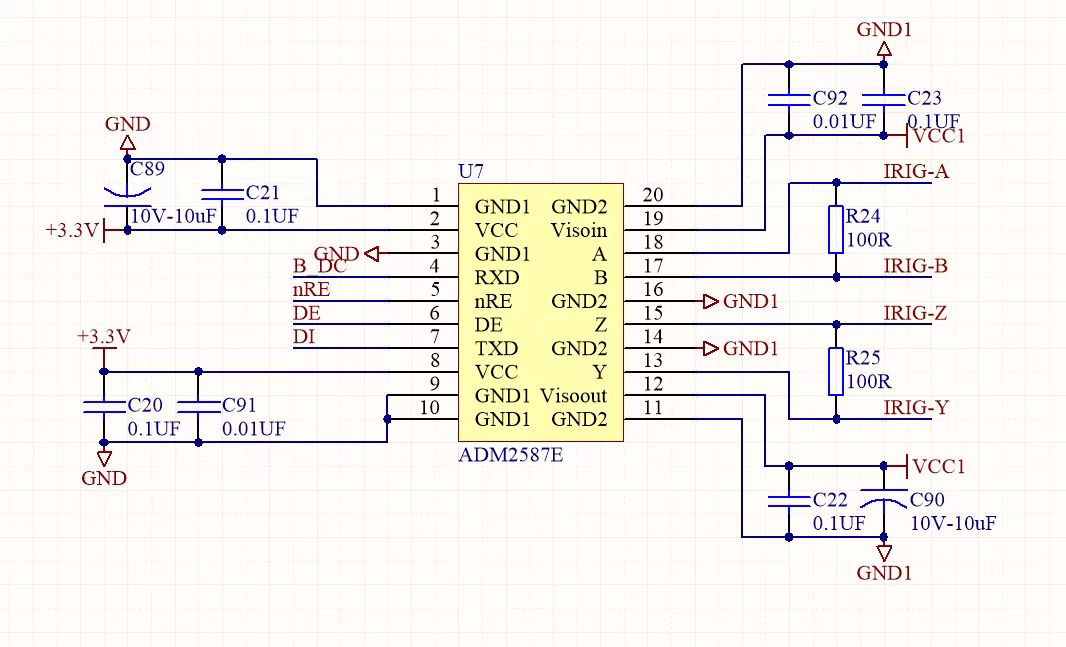

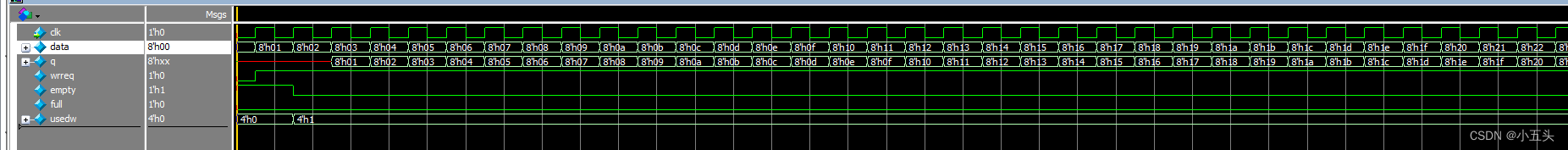

eLinx工具开发

module FIFO_TOP(

input wire clk

);

reg [7:0] data=0;

reg wrreq=0;

wire empty;

wire full;

wire [3:0] usedw;

wire [7:0] q;

always @ (posedge clk) begin

data <= data + 1'b1;

wrreq <= 1'b1;

end

fifo_1 u_fifo_1(

.clock (clk),

.data (data),

.rdreq (1'b1),

.wrreq (wrreq),

.empty (empty),

.full (full),

.usedw (usedw),

.q (q)

);

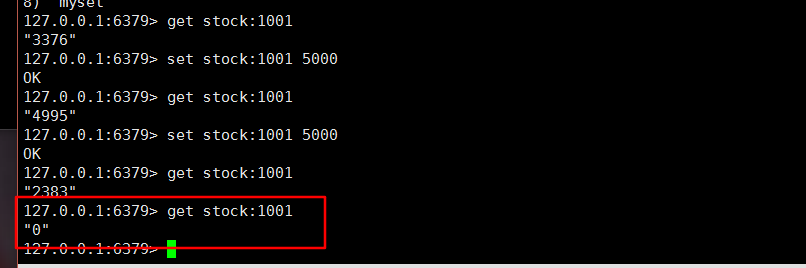

endmodule实验结果

结论

FIFO大小:根据应用需求选择适当的FIFO大小。如果FIFO太小,可能会导致数据丢失或溢出。如果FIFO太大,可能会浪费资源。因此,根据应用的数据流量和延迟要求选择合适的FIFO深度。时钟和复位:确保FIFO的时钟和复位信号正确连接。时钟信号必须是稳定的,并满足FIFO的最小时钟频率要求。复位信号应在系统启动时对FIFO进行复位,以确保其处于已知状态。数据宽度匹配:确保FIFO的输入和输出数据宽度匹配。如果数据宽度不匹配,可能会导致数据损坏或不正确的数据传输。读写控制:正确控制FIFO的读写操作。确保只在FIFO非满时写入数据,并在FIFO非空时读取数据。使用合适的读写使能信号来控制FIFO的读写操作。状态检测:使用FIFO的状态信号(如fifo_empty和fifo_full)来检测FIFO的状态。这些信号可以用于判断FIFO是否为空或已满,以避免数据丢失或溢出。时序约束:在设计中,确保对FIFO的读写操作满足正确的时序约束。这可以通过设置适当的时序约束或使用时序分析工具来验证。时钟域处理:确保FIFO的读写操作在正确的时钟域进行。如果涉及多个时钟域,需要使用合适的时钟域划分技术(如时钟域交叉点或异步FIFO)来处理时钟域间的数据传输。异步复位:如果FIFO的复位信号来自于异步复位源(如外部复位信号),需要考虑异步复位的时序和影响,并确保正确处理异步复位。同步/异步接口:根据系统需求,选择合适的FIFO接口类型。可以使用同步接口(如双时钟同步FIFO)或异步接口(如双端口异步FIFO)。时序和资源约束:在FPGA设计中,根据具体的FPGA型号和工具要求,设置适当的时序和资源约束,以确保FIFO的正确功能和性能。

参考文献

-

Smith, J. G., & Franzon, P. D. (1997). The designer's guide to VHDL. Morgan Kaufmann.

本书介绍了FIFO的基本概念和设计方法,并提供了用VHDL实现FIFO的示例。 -

Chu, P. (2000). FPGA prototyping by Verilog examples: Xilinx Spartan-3 version. Wiley-Interscience.

本书提供了使用Verilog实现FIFO的示例代码和详细说明。 -

Bhasker, J. (2005). A VHDL primer. Pearson Education India.

本书介绍了FIFO的基本原理,并提供了VHDL代码实现示例。 -

Gajski, D. D., Dömer, R., Abdi, S. A., & Gerstlauer, A. (2009). Embedded system design: Modeling, synthesis and verification. Springer Science & Business Media.

本书介绍了FIFO在嵌入式系统设计中的应用,包括建模、综合和验证等方面的内容。 -

Palnitkar, S. (2003). Verilog HDL: A guide to digital design and synthesis. Prentice Hall.

本书详细介绍了Verilog HDL语言,包括FIFO的设计和实现。