文章目录

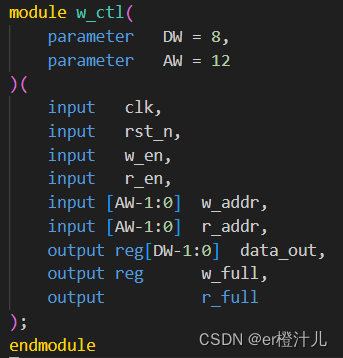

- Verilog端口文件(仅做示范用)

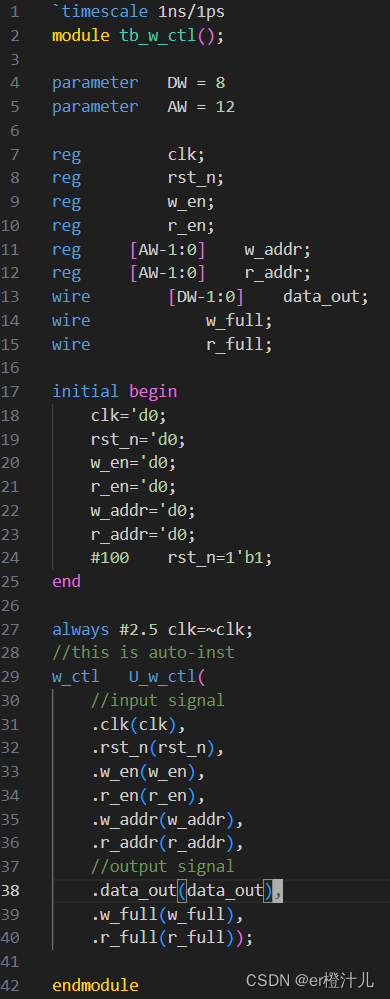

- 对应的tb文件

- 相应代码

在数字IC设计过程中,根据顶层生成testbench时存在很多重复性工作,因此为了提高工作效率,特地开发此脚本。

相应的python脚本见链接: 【效率提升—Python脚本】根据Verilog文件自动生成tb文件

Verilog端口文件(仅做示范用)

对应的tb文件

相应代码

use strict;

open R_FILE,"w_ctl.v" or die "can't open file:$!";

open W_FILE,"> tb.v" or die "can't touch tb file:$!";

my @in;

my @in_reg;

my @ou;

my @ou_wire;

my @par;

my $mo;

while(<R_FILE>){

if(/module\s+(\w+)/){

$mo=$1;

}elsif(/(parameter\s+\w+\s?=\s?\d+)/){

push(@par,$1);

}elsif(/input\s+(\[\S+:\d+\])?\s+(\w+)/){

push(@in_reg,$1);

push(@in,$2);

}elsif(/output\s+\S*?(\[\S+:\d+\])?\s+(\w+)/){

push(@ou_wire,$1);

push(@ou,$2);

}else{

next;

}

}

print W_FILE "`timescale 1ns/1ps\n";

print W_FILE "module tb_$mo();\n\n";

foreach(@par){

print W_FILE "$_\n";

}

print W_FILE "\n";

foreach(0..$#in_reg){

print W_FILE "reg\t\t$in_reg[$_]\t$in[$_];\n";

}

foreach(0..$#ou_wire){

print W_FILE "wire\t\t$ou_wire[$_]\t$ou[$_];\n";

}

print W_FILE "\n";

print W_FILE "initial begin\n";

foreach(@in){

print W_FILE "\t$_='d0;\n";

}

foreach(@in){

if(/rst_n/){

print W_FILE "\t#100\t$_=1'b1;\n";

}else{

next;

}

}

print W_FILE "end\n\n";

foreach(@in){

if(/clk$/){

print W_FILE "always #2.5 $_=~$_;\n";

}else{

next;

}

}

print W_FILE "//this is auto-inst\n";

print W_FILE "$mo\tU_$mo(\n";

print W_FILE "\t//input signal\n";

foreach(@in){

print W_FILE "\t.$_($_),\n";

}

print W_FILE "\t//output signal\n";

foreach(0..$#ou-1){

print W_FILE "\t.$ou[$_]($ou[$_]),\n";

}

print W_FILE "\t.$ou[-1]($ou[-1]));\n\n";

print W_FILE "endmodule";

close R_FILE;

close W_FILE;

学习更多IC知识,请关注