Why Test?

可测试性(testability)是一种设计的属性,衡量了全面测试制造设计的正确性的难易程度。原始的设计和测试过程是分开的,只有在设计周期的结尾考虑测试。而DFT将测试和设计融合在一起。

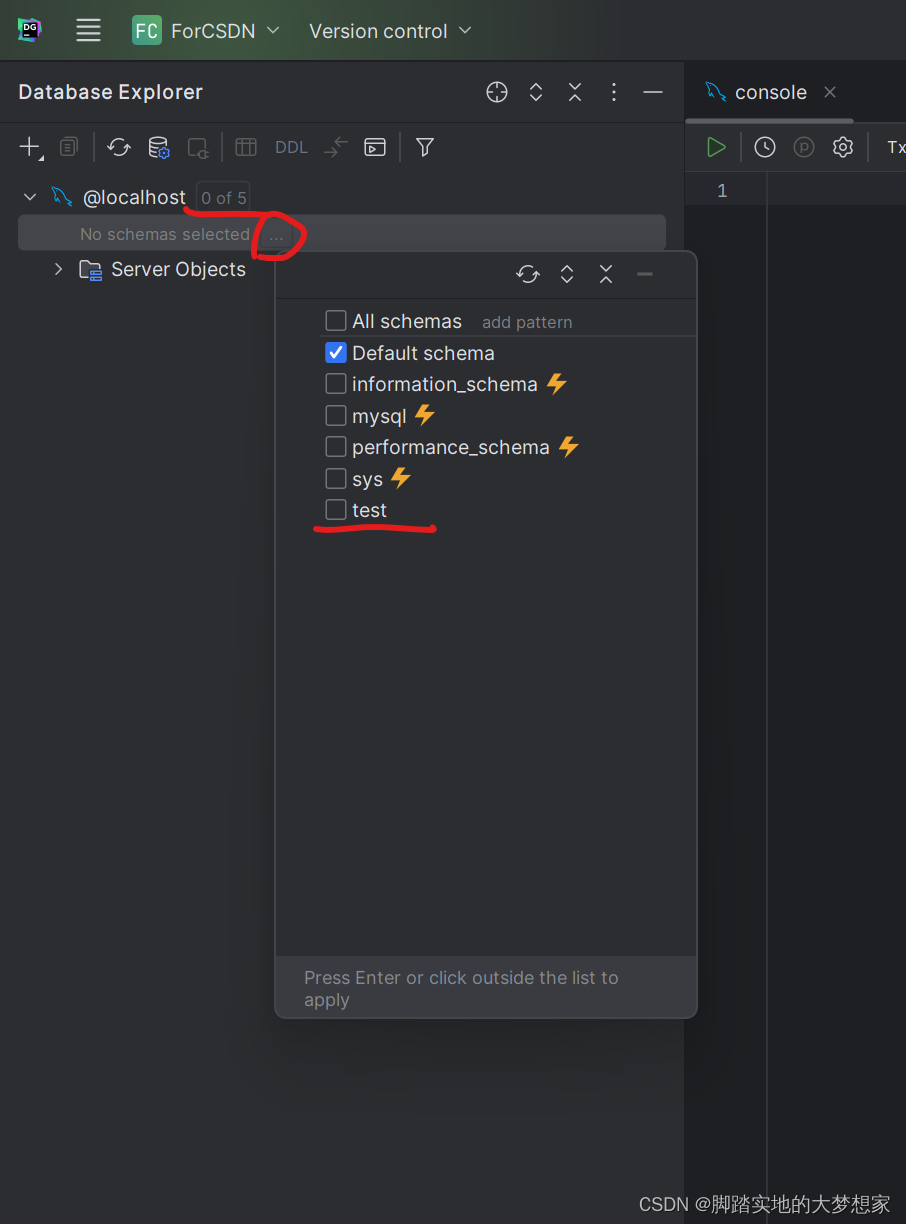

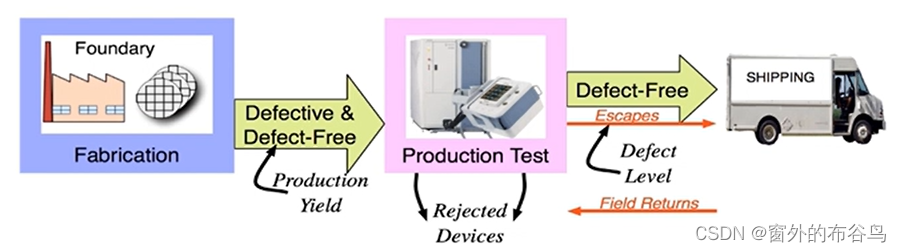

来自foundary的devices需要被测试以识别出有缺陷的devices。通过插入scan来增加芯片本身的可测试性,并且使用ATPG生成patterns以识别这些缺陷。没有缺点的devices被销售给顾客,有时有缺陷的devices通过了所有的应用测试——这被称为测试逃避(test escapes)。在顾客手中出现失败的devices会被返回。

缺陷是发生在silicon上的物理问题,可能会导致silicon的性能与设计不同。制造问题能够造成各种缺陷,例如:

1. hard tie到电源或地,节点总是stuck-at 1或stuck-at 0。当创建test pattern以force节点到相反值是,该defect容易被检测到。

2.两个连接之间短路,或桥接。节点在周围的net状态下,有条件的出现stuck-at 1或stuck-at 0;在一个path上的数据会带给不同path上的数据不利影响。

3.capacitive或resistive节点。慢的0->1 transition,或1->0 transition。可以被扩展到查找沿着关键路径的精确时间延迟。或者是path延迟比期望延迟更长。

有不同类型的测试尝试捕获可能出现在device中的任意缺陷。过去,在使用scan testing和ATPG之前,应用的是功能测试。功能或工程测试应用激励到设计上为了证明在测试下device满足工程规格。

manufacturing tests是为了确保device被正确制造。能够验证设计没有制造缺陷,但是不能验证silicon满足预期的行为,电路可能通过测试,但是设计可能功能不正确(例如,不能像功能规格描述的那样操作)。

manufacturing测试的类型:

- scan test

- 具有压缩的scan test

- BIST:Memorytest和Logic test

- Functional test:效率低;难以确定测试覆盖率

Introduction to Scan Test and ATPG

测试是一个控制和观测问题。

control:能够使用test pattern有目的地激励目标位置?

observe:能够观察激励地效应?

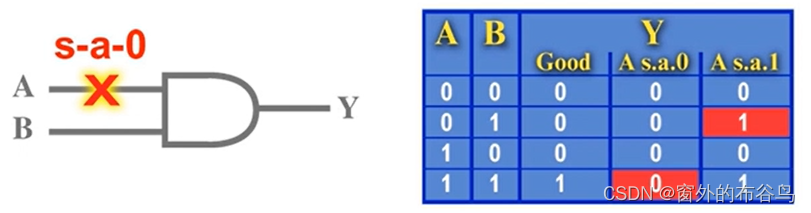

fault models提供模拟defects的一种缺陷,为了可以生成patterns来识别defects。当在good behavior和faulty behavior之间观测到差异时能够检测到故障。最常见的fault model是stuck-at。

test patterns伴随两件事:fault activation(control)和fault propagation (observe)。

fault activation在故障模型位置建立一个信号值,与故障模型产生的值相反。fault propagation通过敏化从故障位到PO或scan cell的path,将产生的结果信号值或故障效应向前移动。

test patterns,有时被称为test vectors,是在测试过程期间放置在PI引脚上的一系列1s或0s。当应用test pattern时,ATE确定电路是否存在制造缺陷。

ATPG process的基础流程:

- 从user-selected故障集中选择故障。

- 创建pattern以control和observe故障。

- pattern是被仿真的故障以确定在good和faulty机制仿真之间时候存在差异。

- 如果目标故障被检测到,则保存pattern。

- 如果其他故障偶然也被检测到,这些故障也会被划分为detected。

Basic Scan Test Process

scan test的流程:

- 通过使用scan cells取代flip-flops来创建control和observation点。

- 将scan flops连接在一起创建扫描链。

- 利用这些扫描链,生成测试patterns:在指定节点(control)设置指定值;传播结果,为了它能够被测试到(observe)。