Verilator简介与使用_Hwang_shuo的博客-CSDN博客

Verilator是一种开源的Verilog/SystemVerilog仿真器,可用于编译代码以及代码在线检查,Verilator能够读取Verilog或者SystemVerilog文件,并进行lint checks(基于lint工具的语法检测),并最终将其转换成C++的源文件.cpp和.h。

Verilator不直接将Verilog HDL转换为C++或者SystemC,反之Verilator将代码编译成更快的优化过的并且支持多线程的模型,该模型被依次包装在(wrapped)在C++/SystemC模型中。这样就生成一个编译的Verilog模型,其功能和Verilog是一致的,但效率由于基于C++即使是单线程模型也可以10倍快于SystemC,100倍快于基于解释Verilog的仿真器,并且通过多线程可以进一步加速。

Verilator的作用是将某些Verilog或System Verilog代码翻译成可编译的C++或System C代码,或者库,之后再编写合适的驱动代码也就是sim_main.cpp,一同使用C编译器进行编译,由此得到可执行的程序,来对Verilog或System Verilog代码进行仿真,得到波形图等仿真结果。

其详细的执行过程如下:

Verilator通过读取指定的 Verilog 或 System Verilog 代码、对其执行 lint 静态代码检查以及可选地插入断言检查和覆盖分析点。它可以输出单线程或多线程的 .cpp 和 .h 文件,即“Verilated(经过验证的)”代码。

用户需要编写的一个C++ / System C Wrapper file 封装文件,这个文件会定义main()函数,它会将“Verilated”模型实例化为C++/System C对象。

用户的Wrapper file、Verilator创建的文件、Verilator提供的“运行时的库”和System C库,这些 C++ / System C 文件之后会由 C++ 编译器 (gcc / clang / MSVC++) 统一进行编译。生成的可执行文件来执行设计仿真。Verilator 还支持将其生成的库(可选加密)链接到其他模拟器。

生成的可执行文件将在“模拟运行”期间执行实际的模拟。还可以生成可查看的设计波形轨迹。

Verilator 并非简单地将 Verilog HDL 转换为 C++ 或 System C。Verilator会将代码编译成一个优化更快的和可选的线程分区模型,该模型又包装在 C++/ System C 模块中。结果就是一个编译好的 Verilog 模型,即使在单线程上的执行速度也比独立的System C快10倍以上,在单线程上的执行速度比解释过的Verilog模拟器(如Icarus Verilog)快100倍左右。多线程可能会带来2-10倍的加速(比解释的模拟器快200-1000倍)。 Verilator 通常具有与闭源 Verilog 模拟器(Carbon Design Systems Carbonator、Modelsim、Cadence Incisive/NC-Verilog、Synopsys VCS、VTOC 和 Pragmatic Cver /CVC)相似或更好的性能。

pre-install:

sudo apt install clang iverilog gtkwave help2main git perl python3 make autoconf g++ flex bison ccache libgoogle-perftools-dev numactl perl-doc libfl2 libfl-dev zlibc zlib1g zlib1g-dev

clone:

$ git clone https://github.com/verilator/verilator

正克隆到 'verilator'...

remote: Enumerating objects: 74926, done.

remote: Counting objects: 100% (222/222), done.

remote: Compressing objects: 100% (139/139), done.

remote: Total 74926 (delta 105), reused 150 (delta 83), pack-reused 74704

接收对象中: 100% (74926/74926), 31.84 MiB | 30.00 KiB/s, 完成.

处理 delta 中: 100% (63697/63697), 完成.

zlcao@zlcao-Vostro-3268:~/sim$ cd verilator/

zlcao@zlcao-Vostro-3268:~/sim/verilator$ git checkout stable

分支 'stable' 设置为跟踪来自 'origin' 的远程分支 'stable'。

切换到一个新分支 'stable'

$ autoconf

$ unset VERILATOR_ROOT

$ autoconf

$ ./configure

$ make -j8

$ make install testing:

testing:

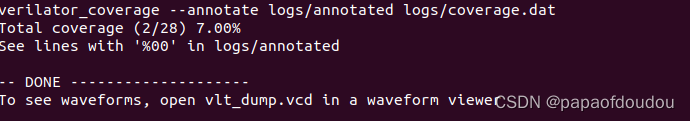

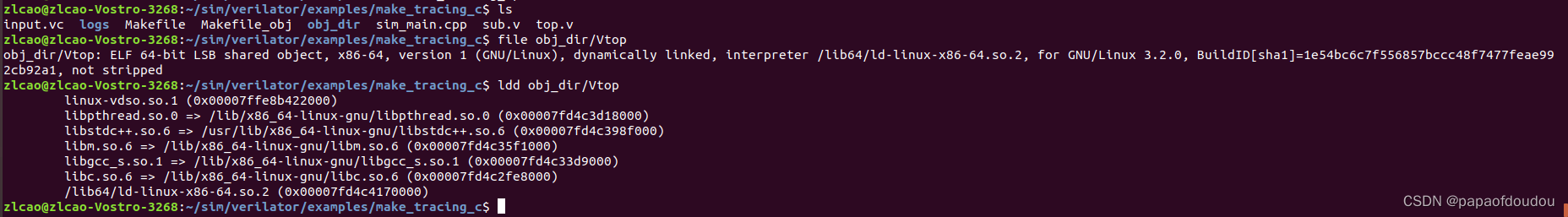

cd /home/zlcao/sim/verilator/examples/make_tracing_c && make

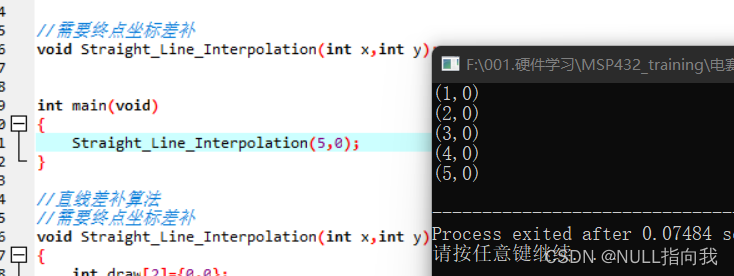

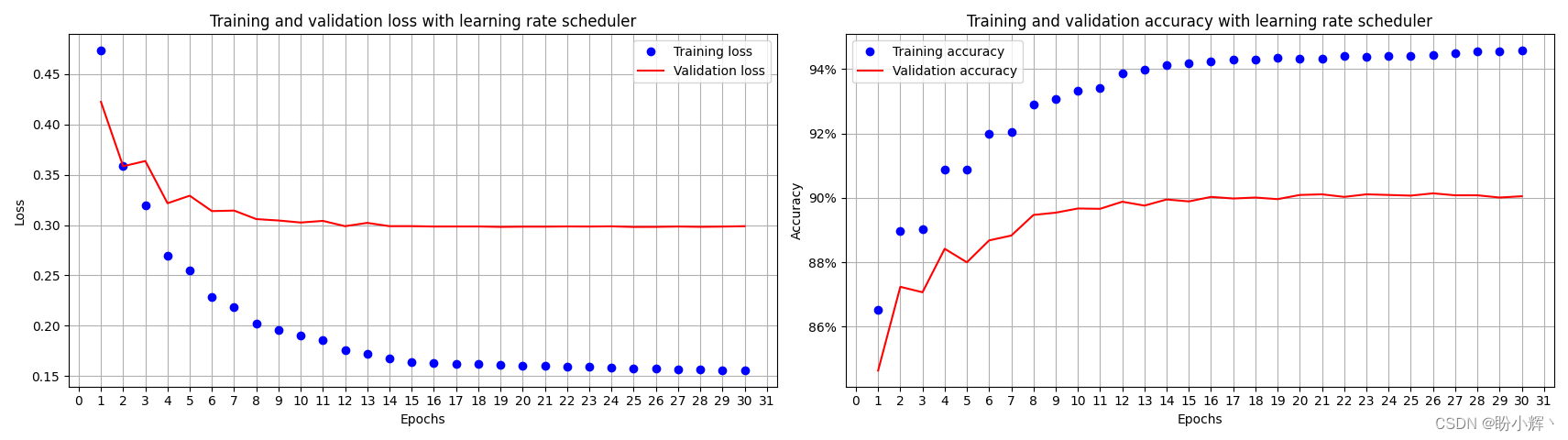

see waveform

![]()

Reference

Installation — Verilator 5.014 documentation