2023年8月5日

- HDBits/Cs450/counter 2bc状态机

- 异步复位

- note

- HDBits/Cs450/history shift

- HDBits/Cs450/gshare

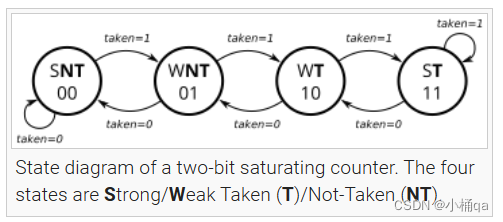

HDBits/Cs450/counter 2bc状态机

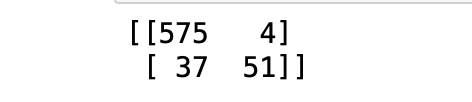

Cs450/counter 2bc

LSB最低有效位

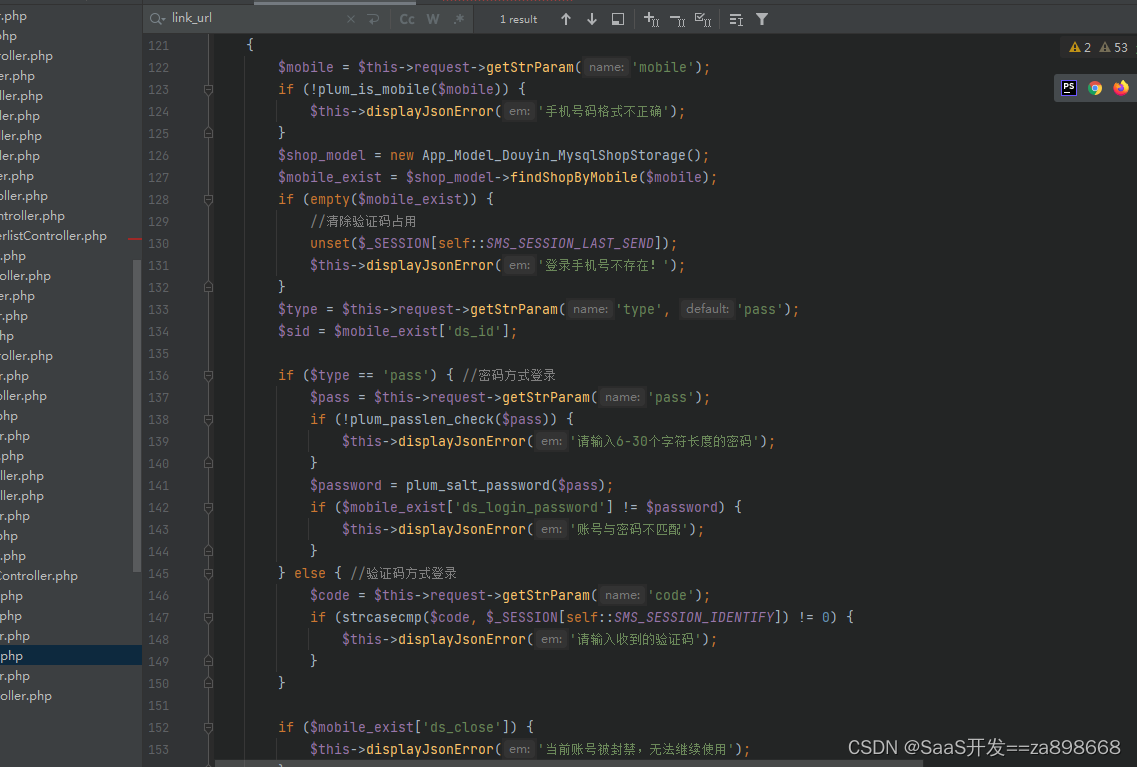

module top_module(

input clk,

input areset,

input train_valid,

input train_taken,

output reg[1:0] state

);

reg [1:0]next_state;

always@(*)

case(state)

0:next_state=train_valid?(train_taken?1:0):0;

1:next_state=train_valid?(train_taken?2:0):1;

2:next_state=train_valid?(train_taken?3:1):2;

3:next_state=train_valid?(train_taken?3:2):3;

endcase

always@(posedge clk or posedge areset)

if(areset)

state<=2'b1;

else

state<=next_state;

endmodule

异步复位

always @(posedge clk or posedge areset)

if(areset)低电平有效

always @(posedge clk or negedge areset)

if(!areset)高电平有效

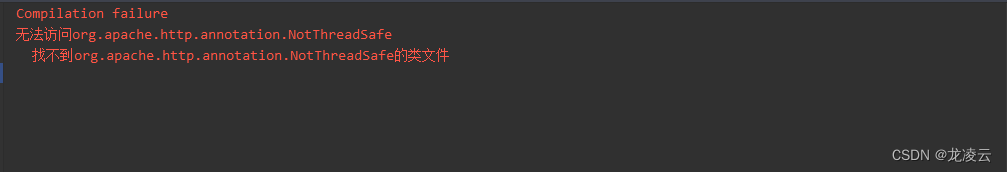

note

无语住了,之前relaunch仿真就会更新,几天没用vivado,relaunch就不更新仿真,没办法打开以前工程操作

没几句的代码,就是找不到原因,shit,搞了半天是复位问题

HDBits/Cs450/history shift

module top_module(

input clk,

input areset,

input predict_valid,

input predict_taken,

output reg [31:0] predict_history,

input train_mispredicted,

input train_taken,

input [31:0] train_history

);

always @(posedge clk or posedge areset)

if(areset)

predict_history<=0;

else begin

if(train_mispredicted)

predict_history = {train_history[30:0],train_taken};

else begin

if(predict_valid)

predict_history = {predict_history[30:0],predict_taken};

else

predict_history = predict_history;

end

end

endmodule