牛客网Verilog刷题——VL47

- 题目

- 答案

题目

实现4bit位宽的格雷码计数器。 电路的接口如下图所示:

输入输出描述:

| 信号 | 类型 | 输入/输出 | 位宽 | 描述 |

|---|---|---|---|---|

| clk | wire | Intput | 1 | 时钟信号 |

| rst_n | wire | Intput | 1 | 异步复位信号,低电平有效 |

| gray_out | reg | Output | 4 | 输出格雷码计数 |

注意:牛客中很多题目与答案不符,本题要求设计一个格雷码计数器,没有说明具体设计要求。实际上本题的设计要求是:初始化格雷码计数器输出为0值,然后将格雷码转为二进制码,然后二进制码计数器加以后再转为格雷码进行输出,要求格雷码计数器输出两个时钟周期发生一次变化。所以格雷码计数器设计中应该包含三个部分:格雷码转二进制、二进制计数器、二进制转格雷码。

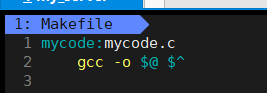

答案

`timescale 1ns/1ns

module gray_counter(

input clk,

input rst_n,

output reg [3:0] gray_out

);

genvar i;

reg [3:0] bin_cnt ; //二进制计数器

wire [3:0] gray2bin; //格雷码转二进制

//格雷码转二进制

generate

for (i=0; i<=3; i=i+1) begin: gray2bin_block

if (i==3)

assign gray2bin[i] = gray_out[i];

else

assign gray2bin[i] = gray_out[i] ^ gray2bin[i+1];

end

endgenerate

//二进制计数器

always @(posedge clk or negedge rst_n)

if(!rst_n)

bin_cnt <= 4'd0;

else

bin_cnt <= gray2bin + 1'b1;

//二进制转格雷码

always @(posedge clk or negedge rst_n)

if(!rst_n)

gray_out <= 4'd0;

else

gray_out <= bin_cnt ^ (bin_cnt>>1);

//备注:本题实际上要求的是初始化格雷码输出为0值,然后将格雷码转为二进制码,二进制码加一,

// 然后再转为格雷码输出,所以应该包括三个部分:格雷码转二进制、计数器和二进制转格雷码

endmodule

![[计算机入门] 回收站](https://img-blog.csdnimg.cn/635ac290b1664de68a5ad97208d75901.png)