微信公众号上线,搜索公众号小灰灰的FPGA,关注可获取相关源码,定期更新有关FPGA的项目以及开源项目源码,包括但不限于各类检测芯片驱动、低速接口驱动、高速接口驱动、数据信号处理、图像处理以及AXI总线等

2、AXI interconnect互联组件的使用及仿真

由于AXI interconnect互联组件只支持Block Design模式下使用,因此介绍Block Design开发过程以及顶层工程文件调用BD文件开发

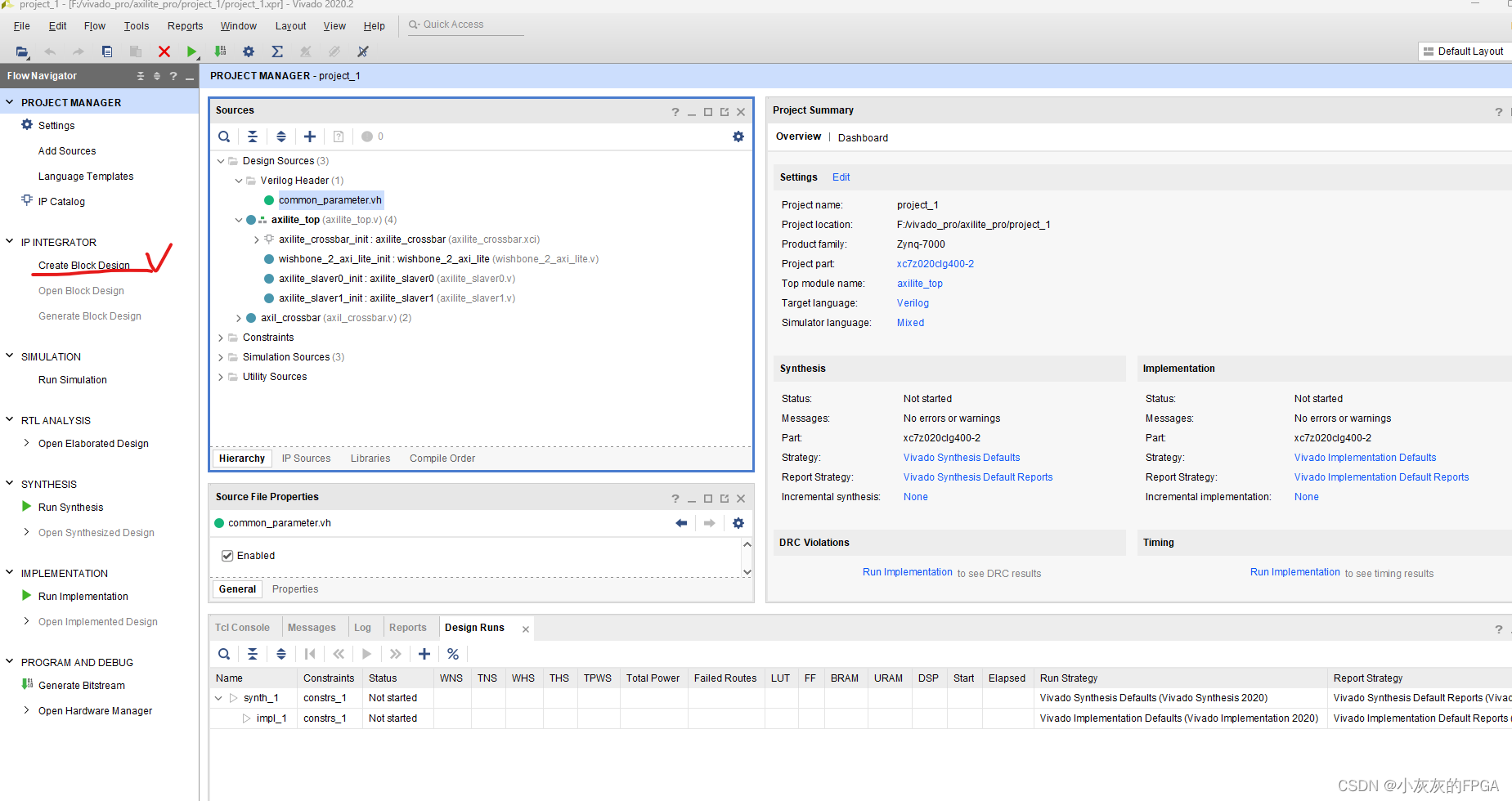

(1)点击Create Block Design

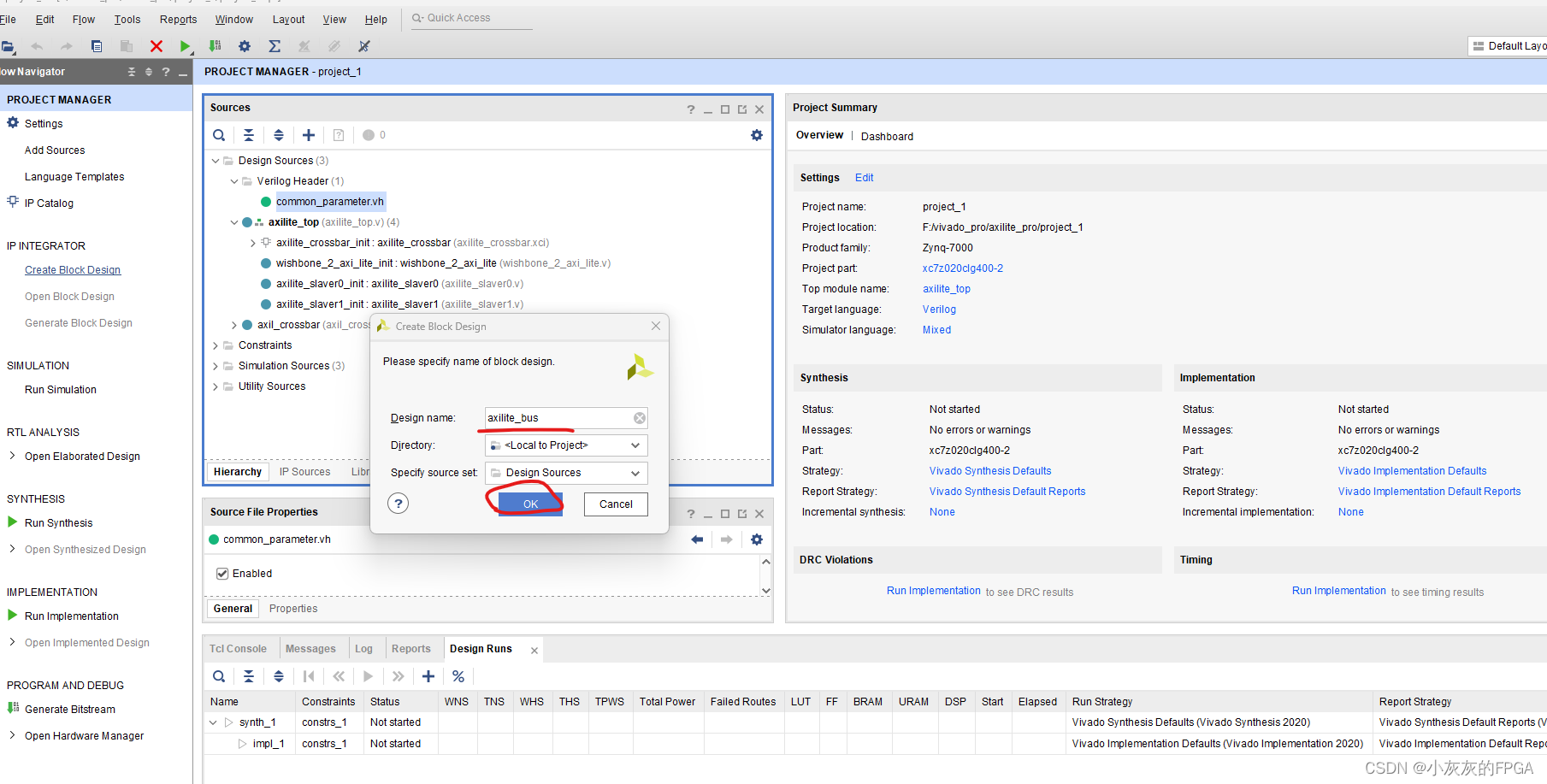

(2)自定义BD名称,修改Design name,并点击OK

(2)自定义BD名称,修改Design name,并点击OK

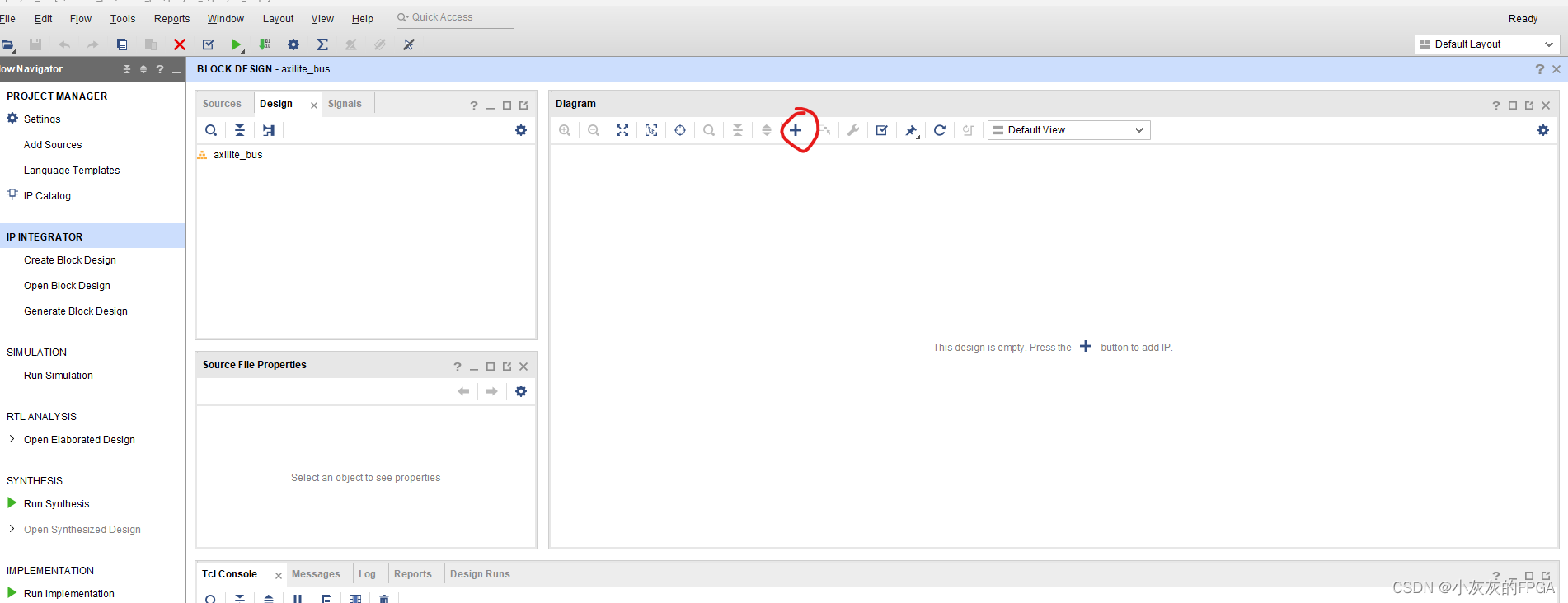

(3)点击“+”,add ip

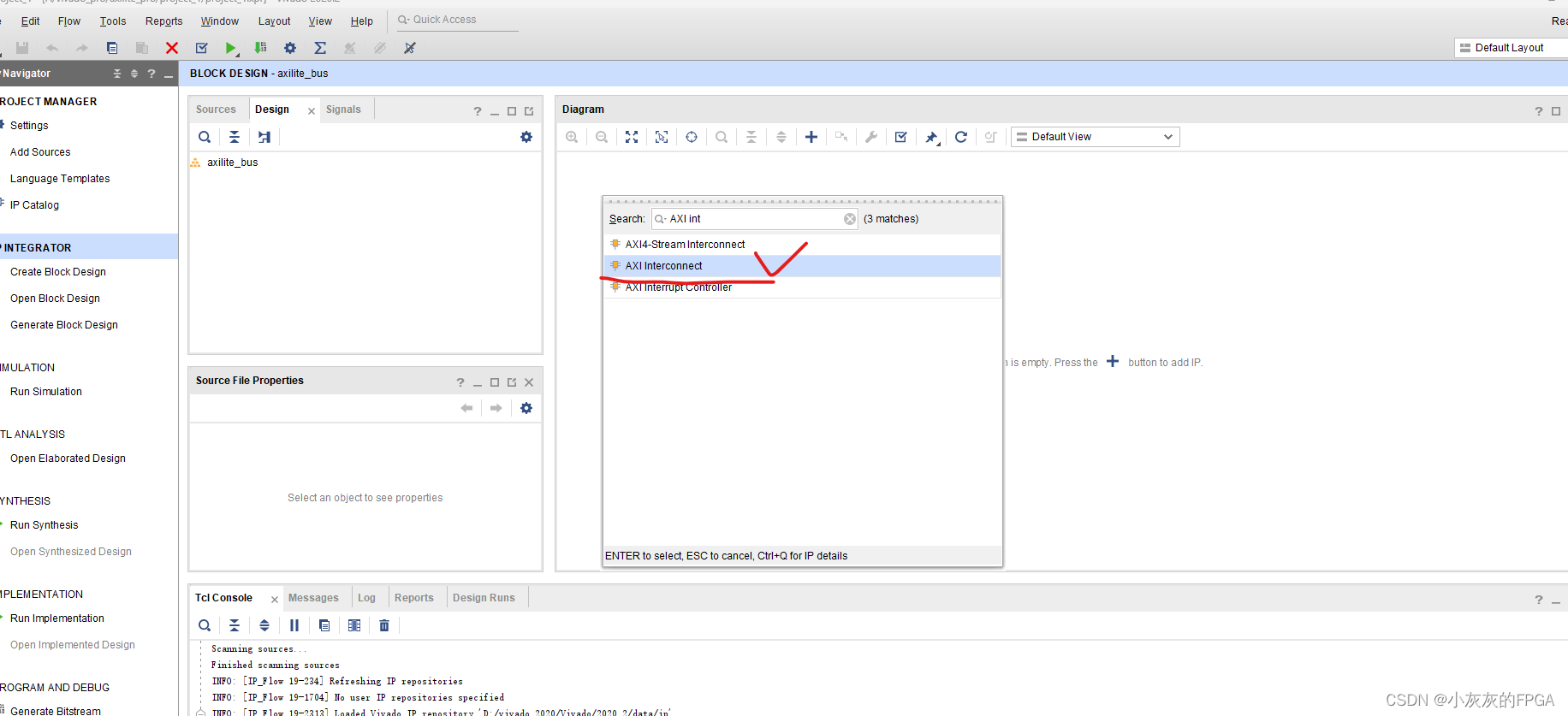

(4)搜索并添加AXI interconnect至Block Design中

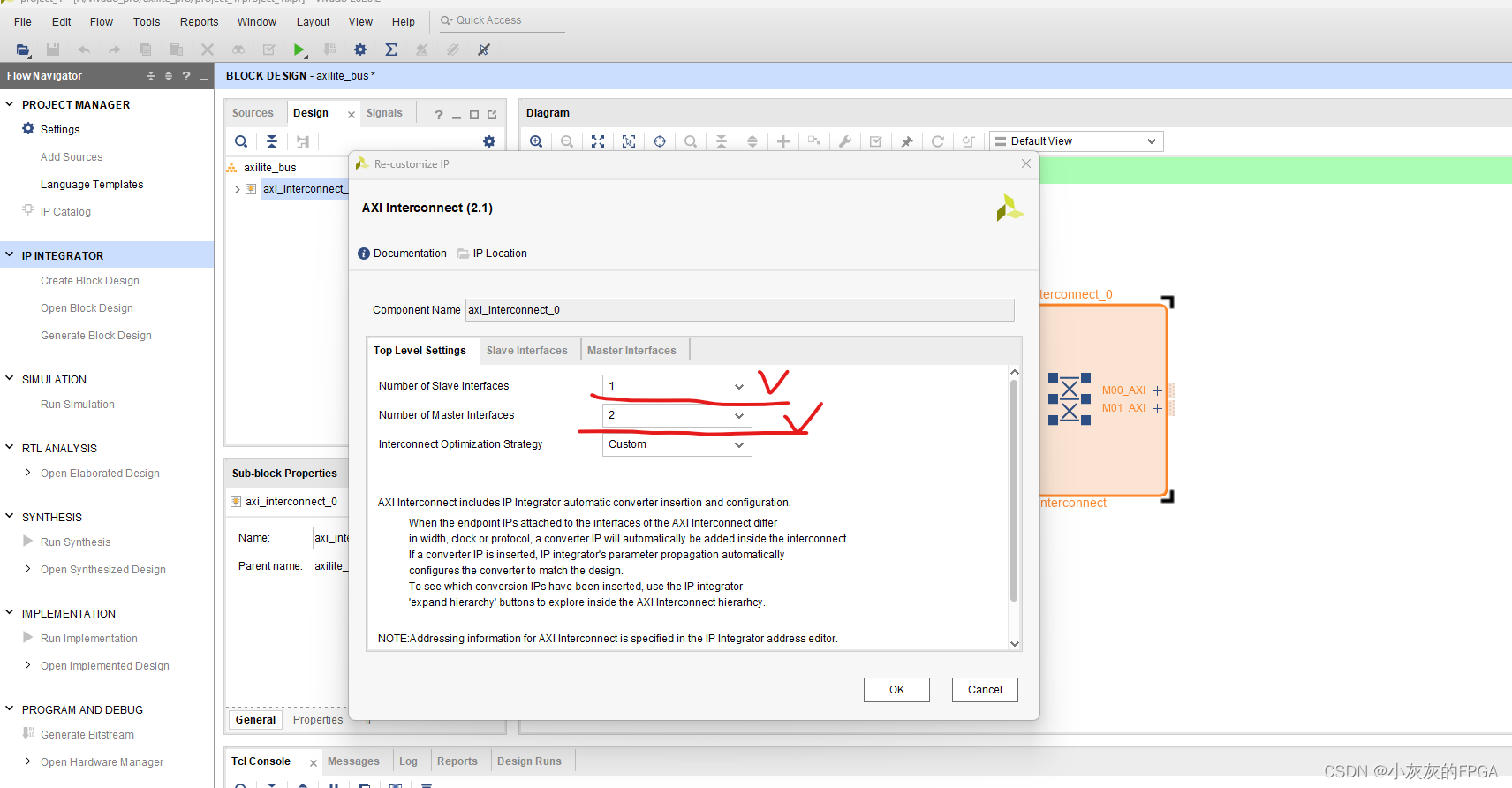

(5)双击AXI interconnect,修改slaver和master num个数,适配工程应用场景,本文用例采用1Master-2Slaver应用,因为对应互联模块应该设置为1Slave和2Master,才能适配成功

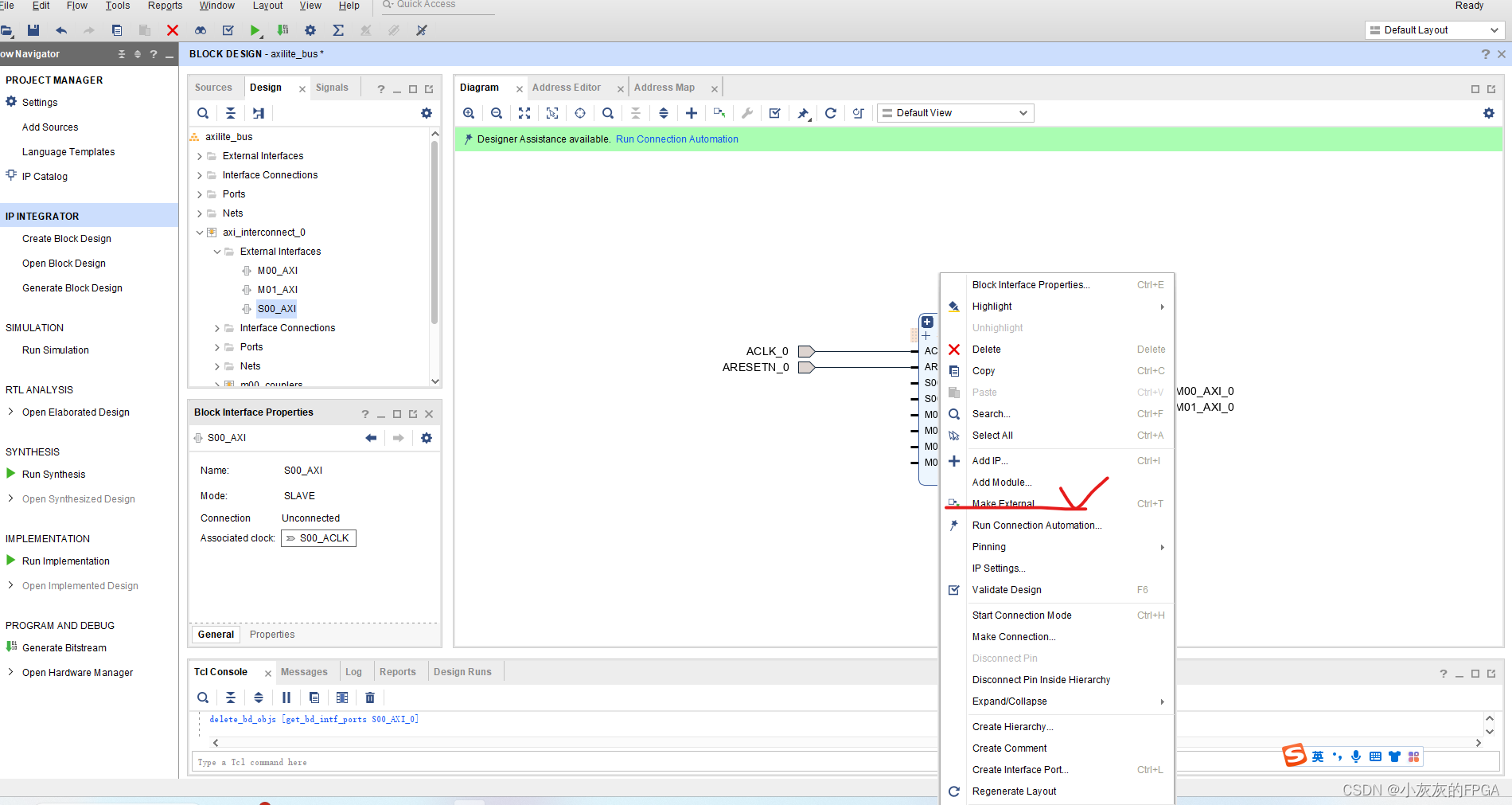

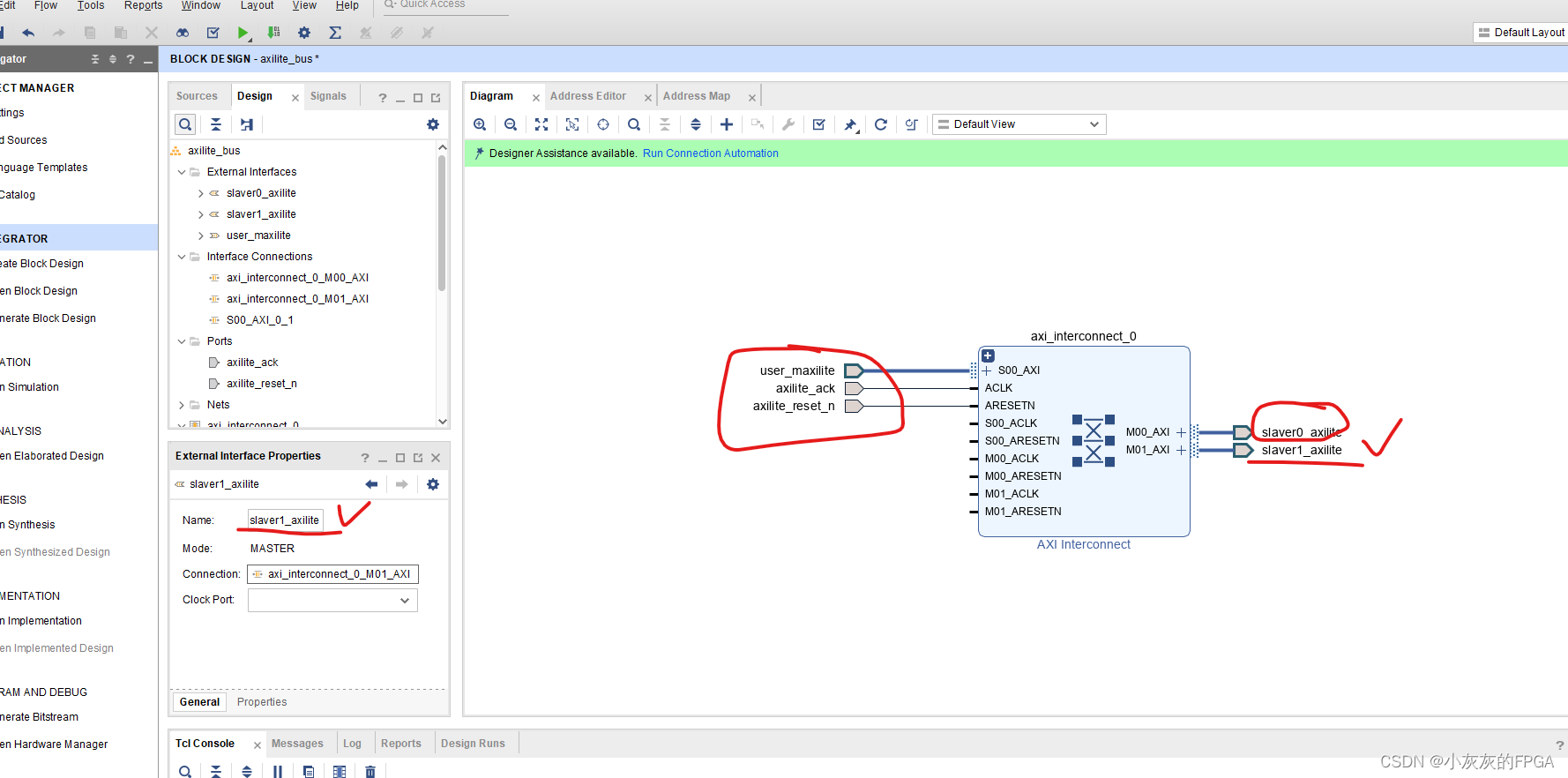

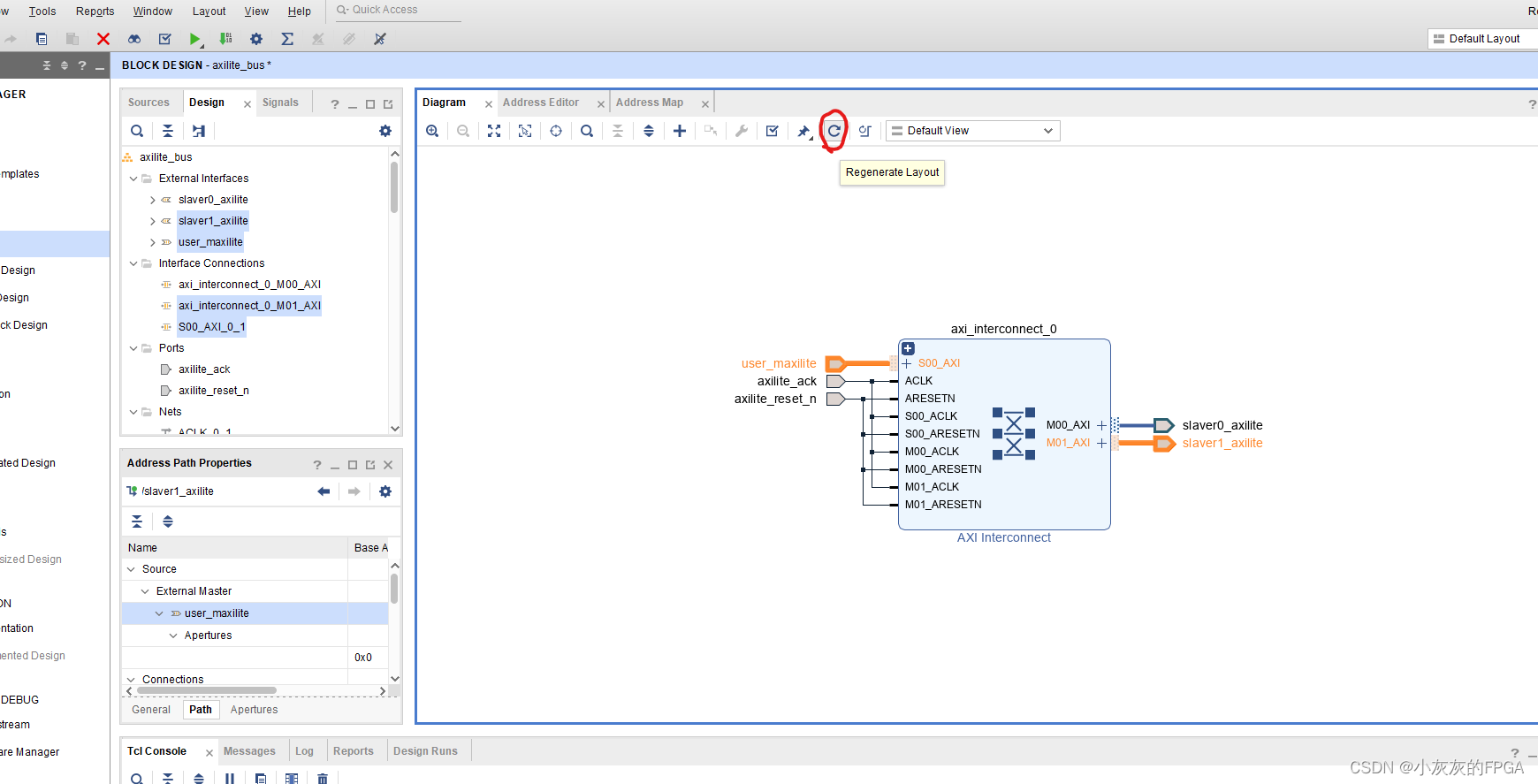

(6)将各个管脚通过Make External,引出至BD设计界面,并自定义名称使用

(7)通过External Interface Properties修改各个扩展接口的自定义名称,与项目适配,便于理解和维护

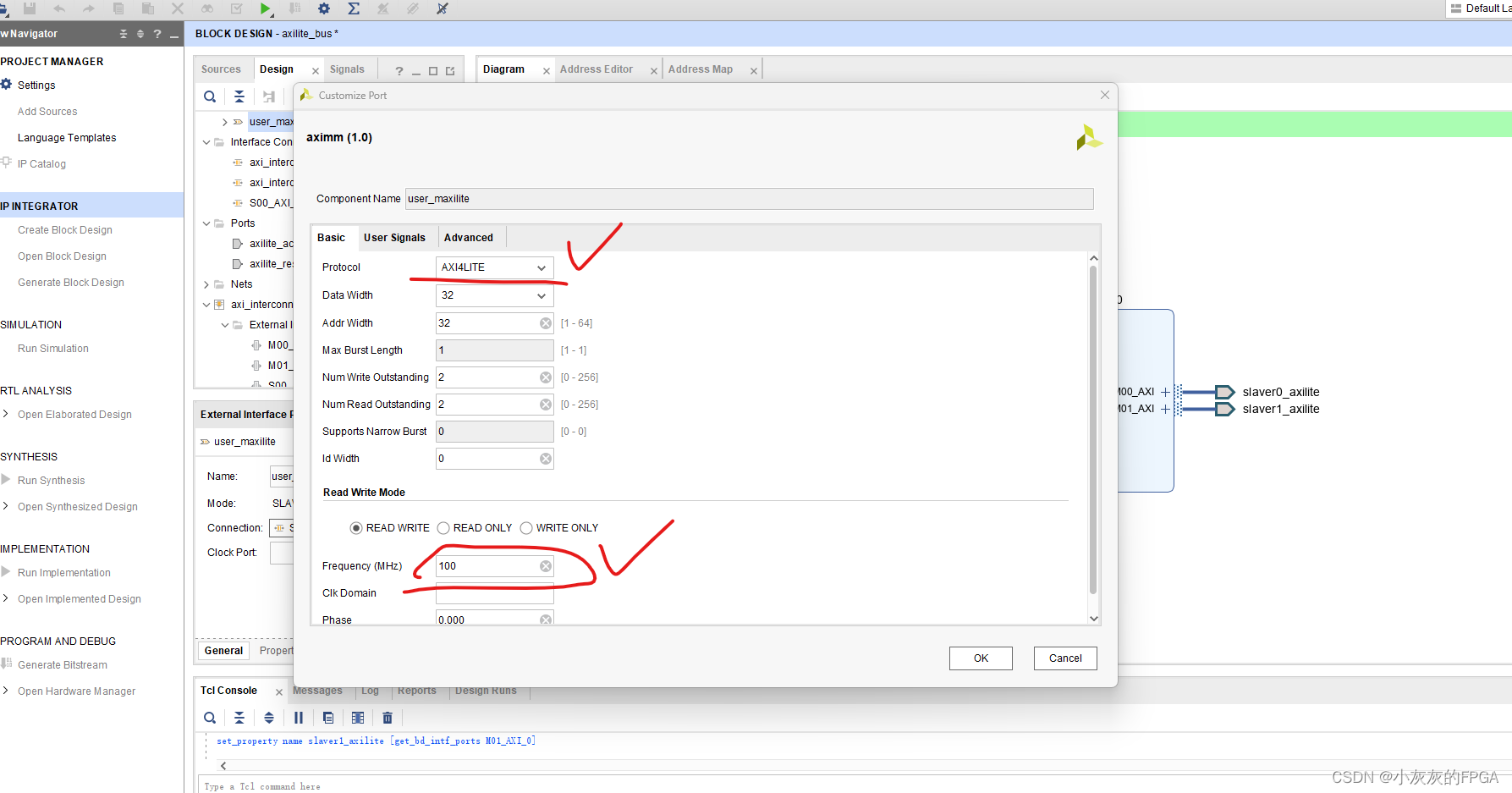

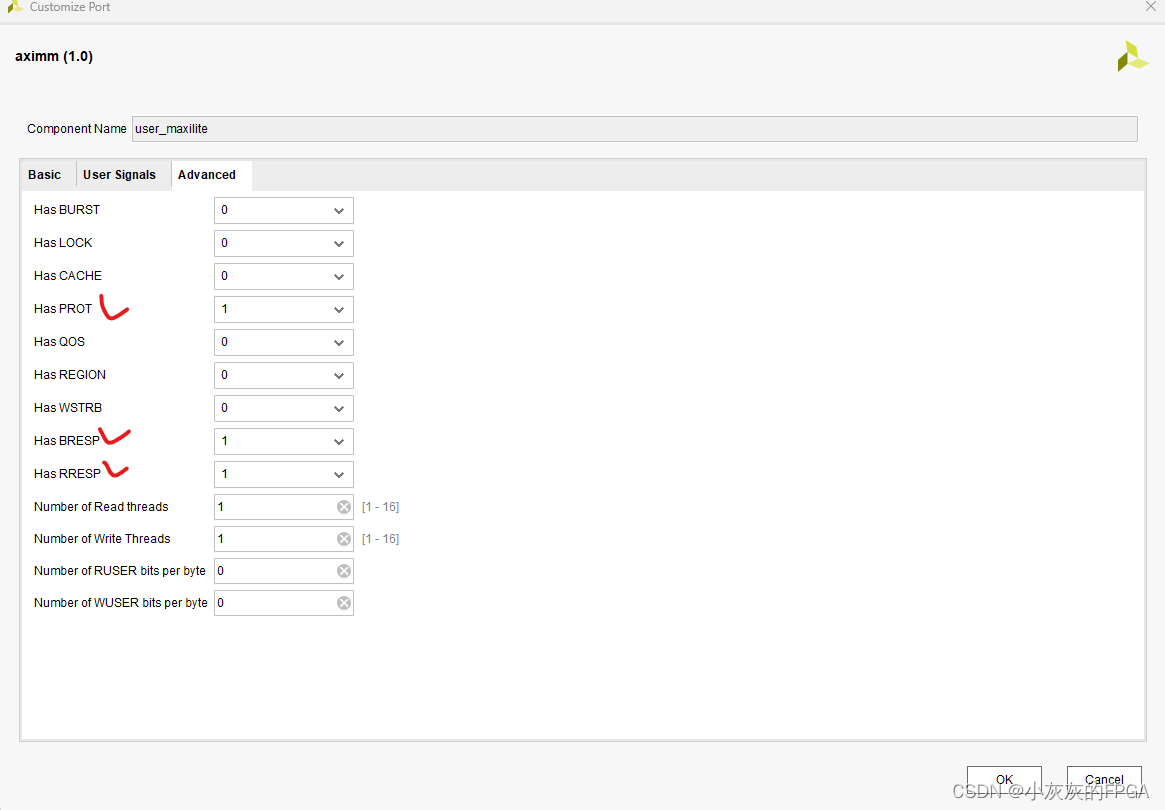

(8)点击扩展接口修改接口的配置,修改Protocol至使用的AXI4LITE,注意将三个接口均修改至对应协议;同时将时钟频率设置为工程系统所用时钟,此处使用100M

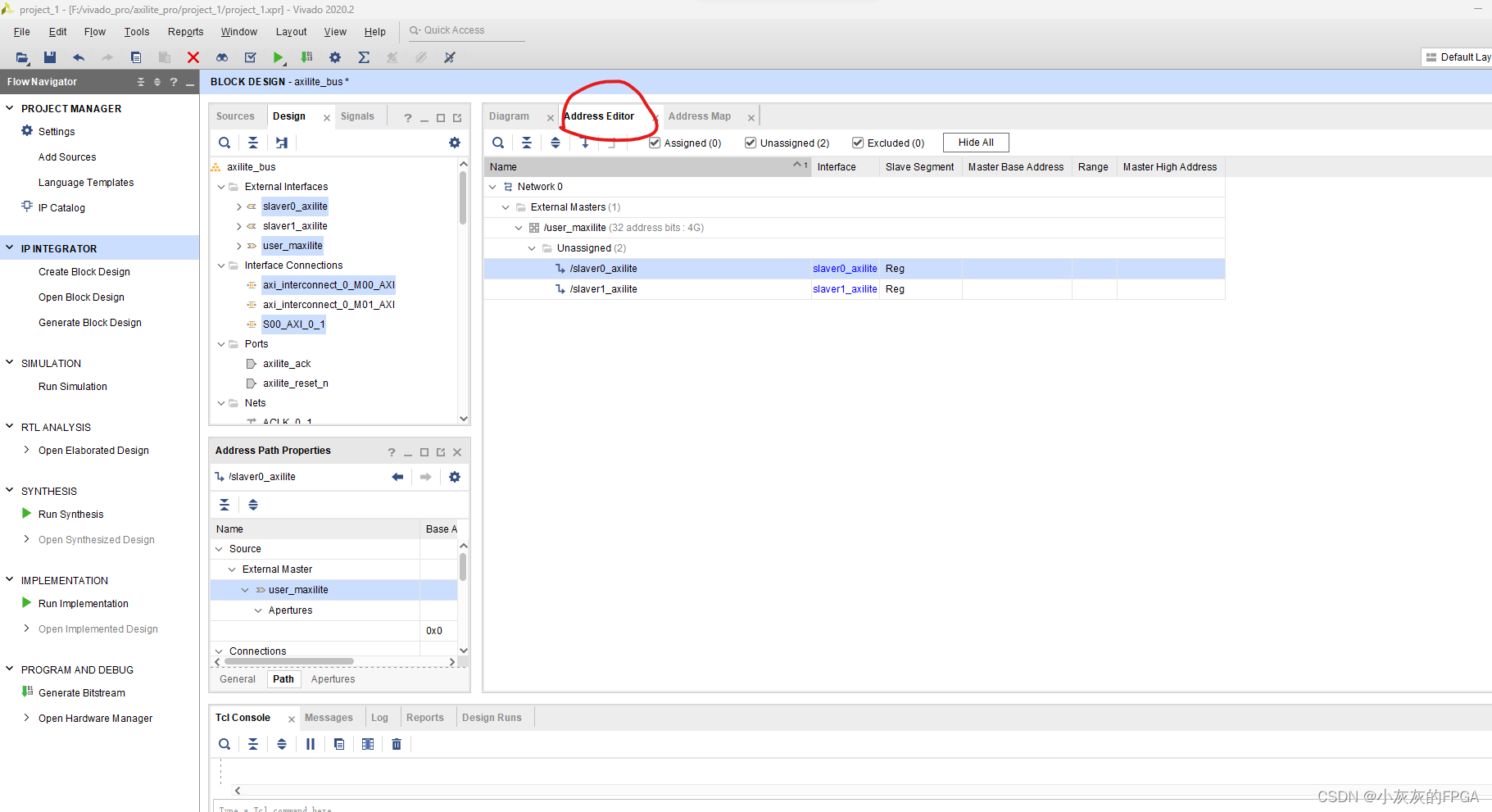

(9)点击Address Editor,设置AXI4lite寄存器分配

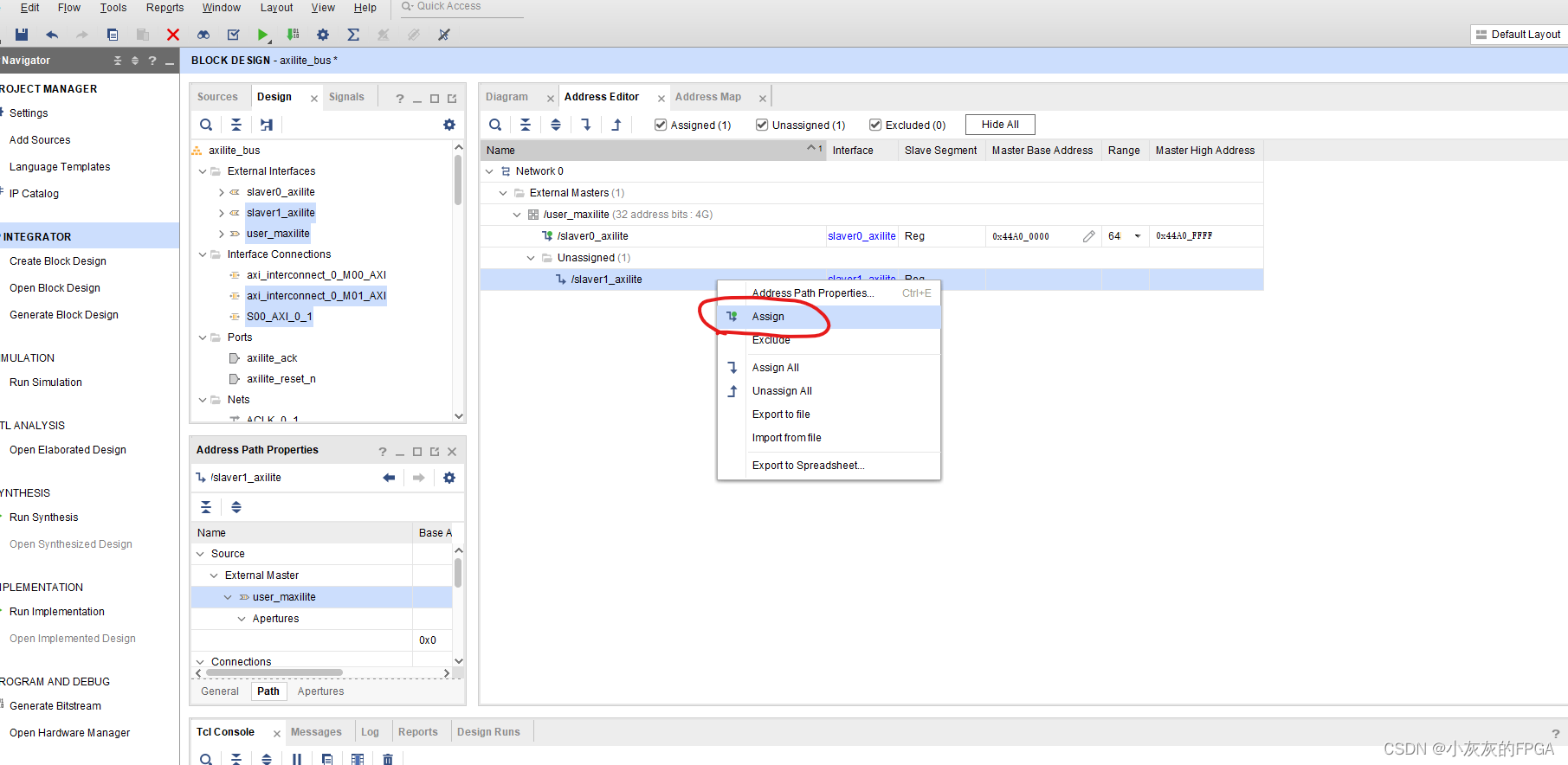

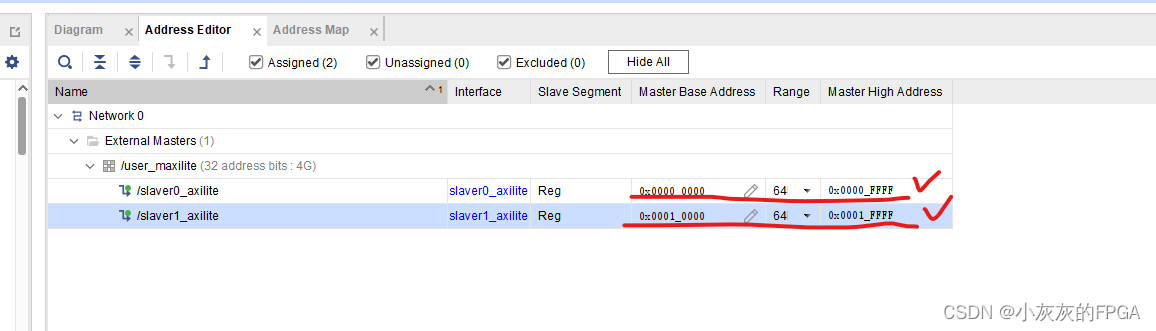

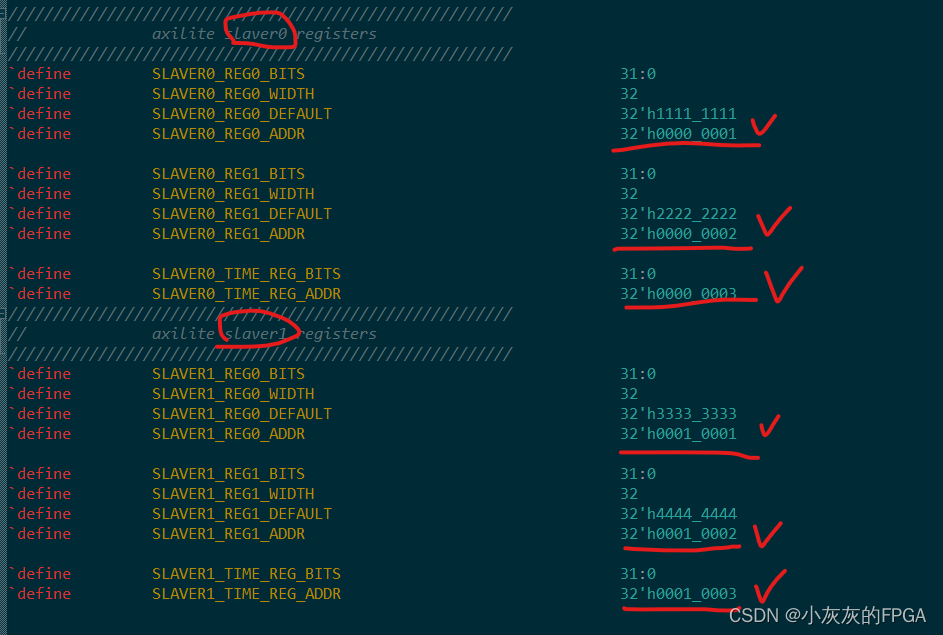

(10)先右键assign后,按系统要求,slaver0寄存器地址范围为0x00000000—0x0000FFFF,内部寄存器使用必须在此范围;slaver1寄存器地址范围为0x00010000—0x0001FFFF,内部寄存器使用必须在此范围。

(11)设置成功后,如图所示,代码开发中需保证各个Slaver用户使用的寄存器在此范围配置内,否则无法响应

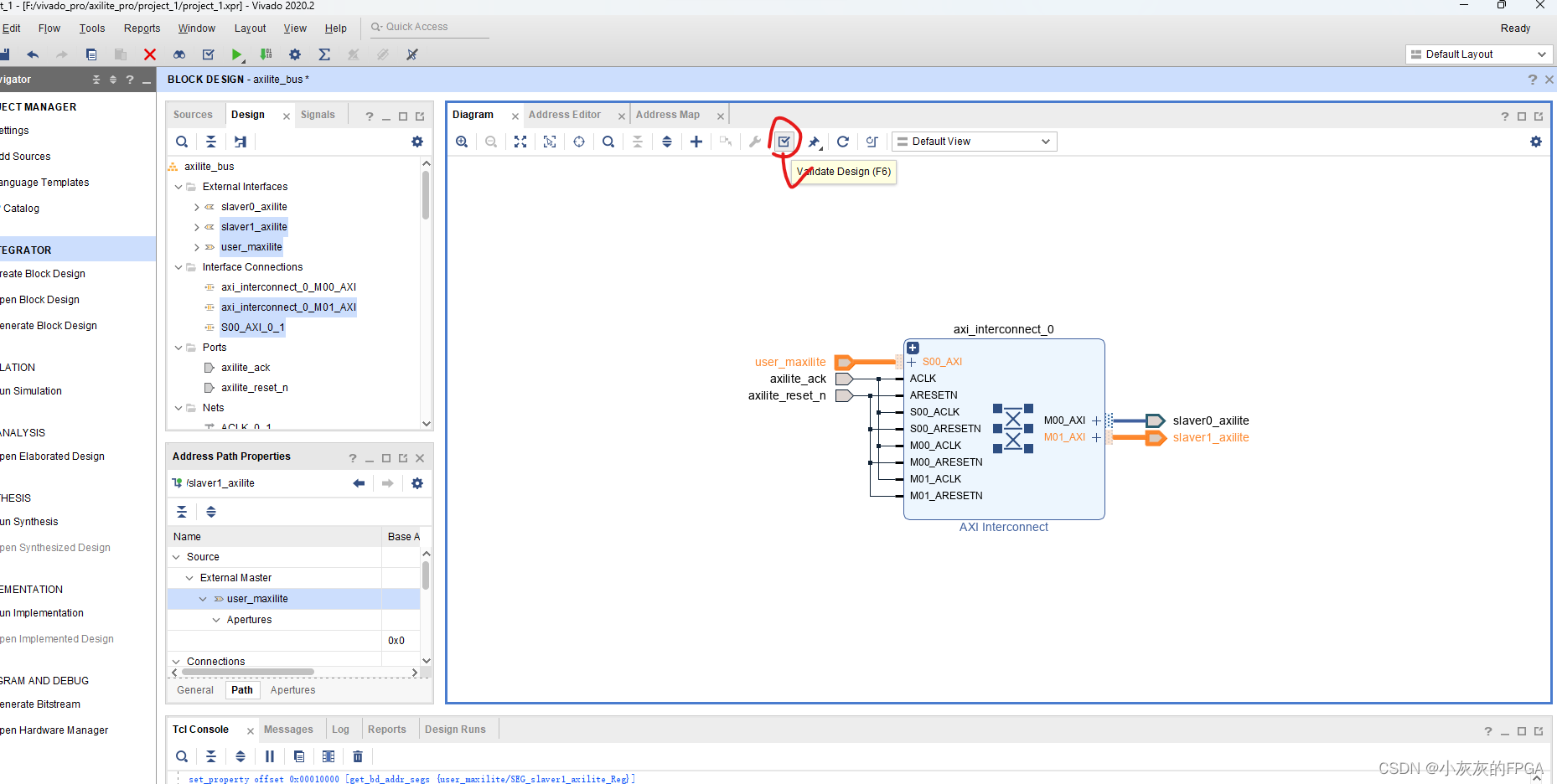

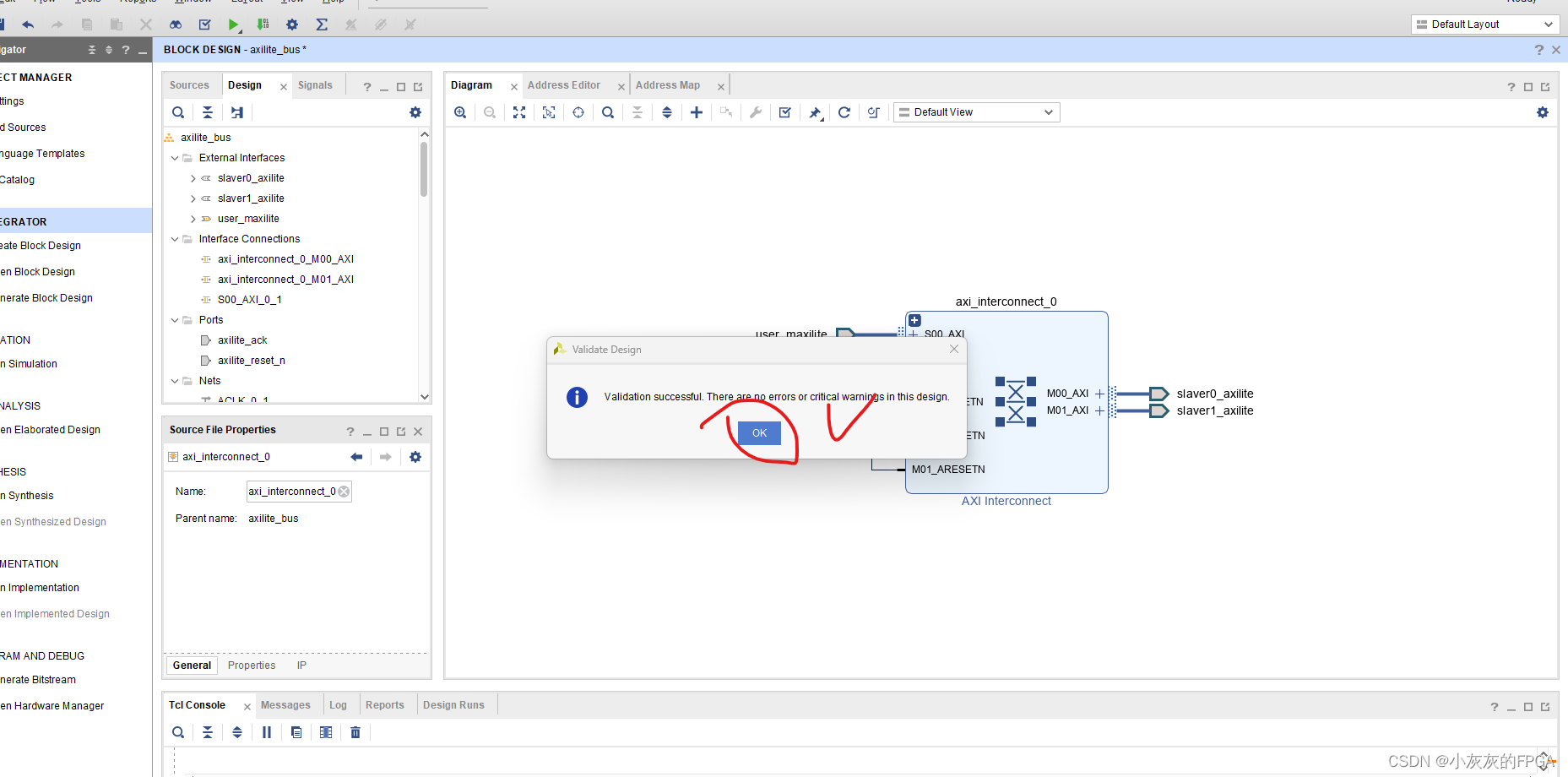

(12)验证设计的可用性,依次按照下述操作Vaildate Design,直至Vaildation suffection为止点击ok

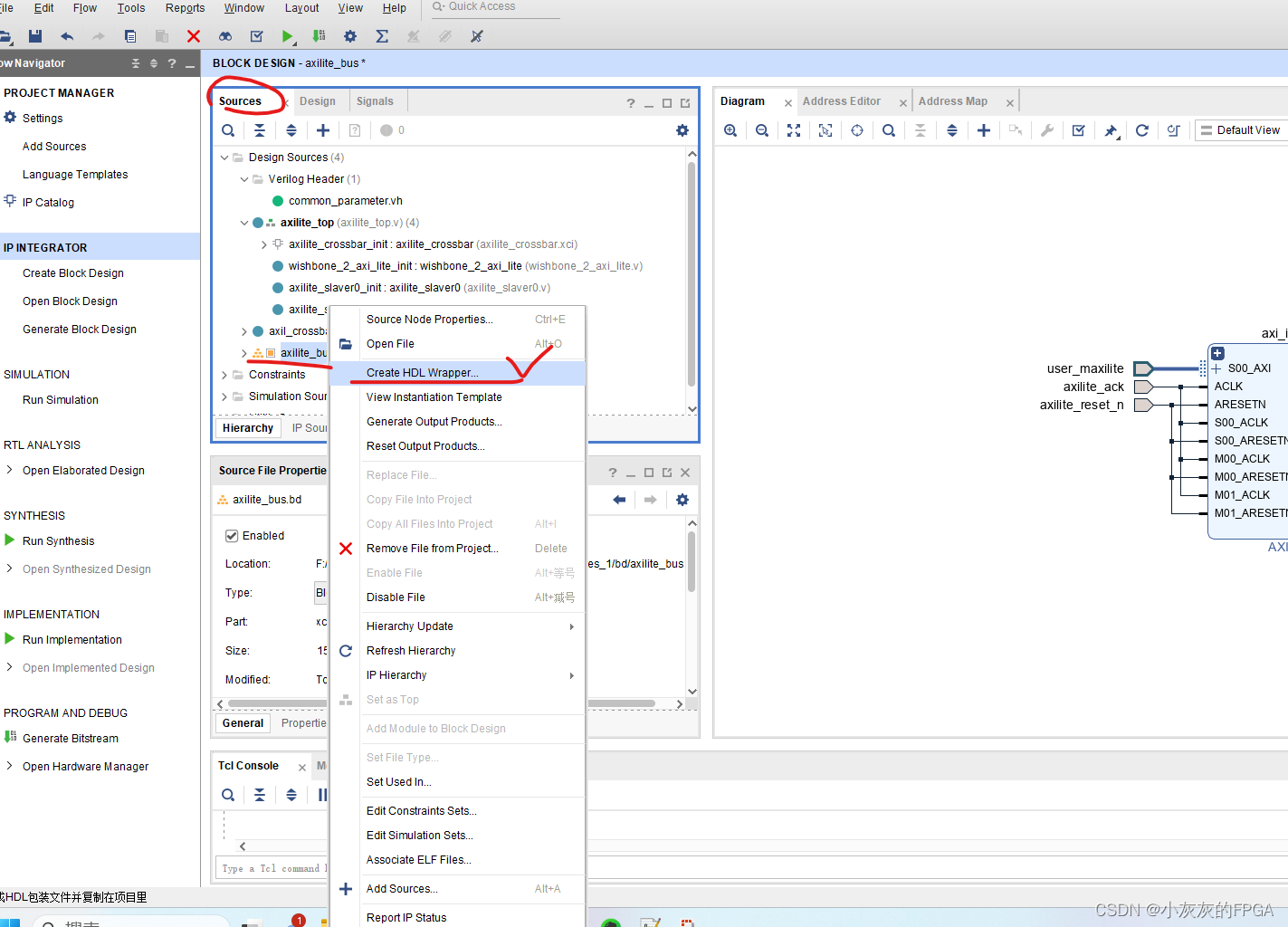

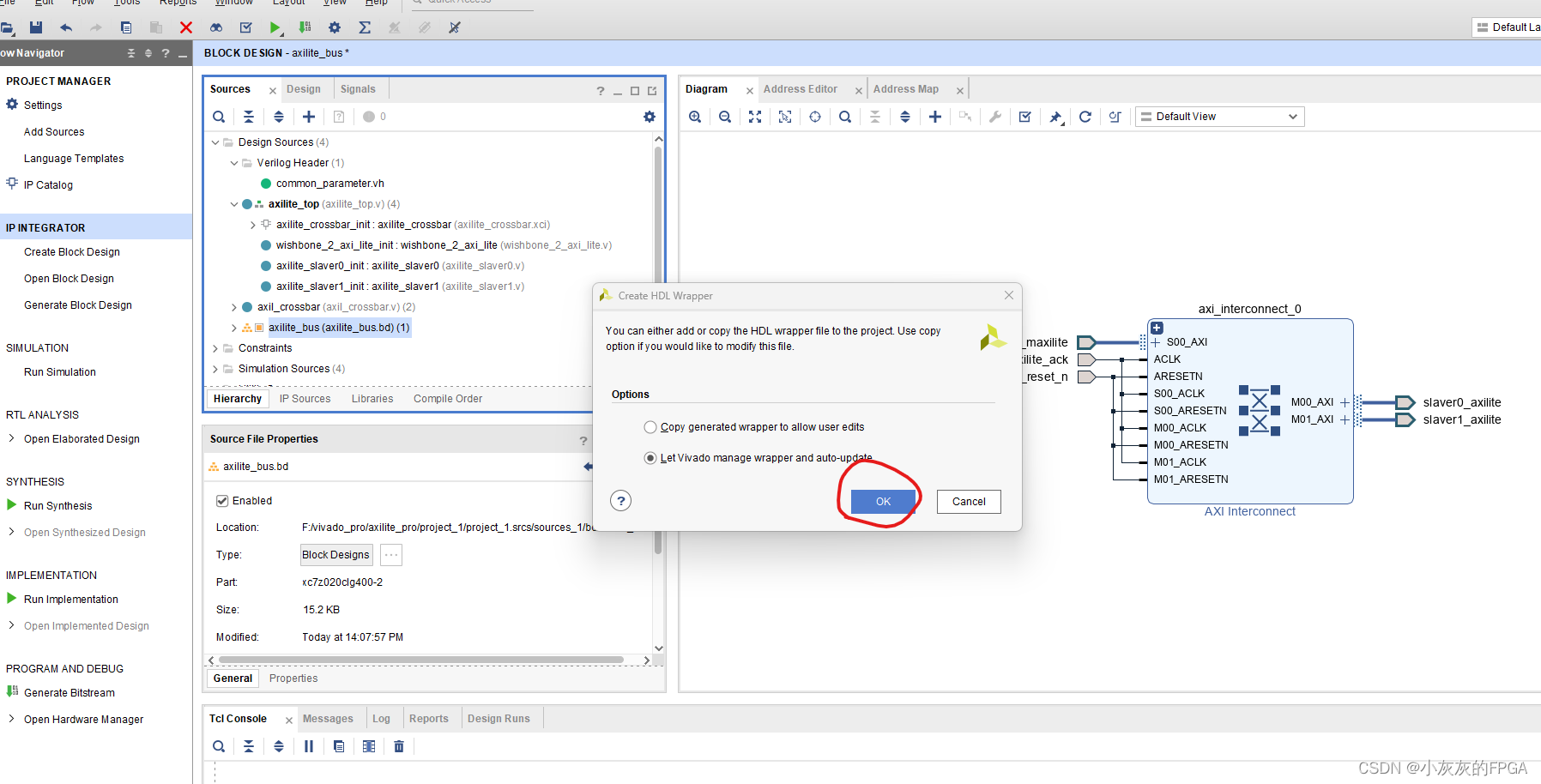

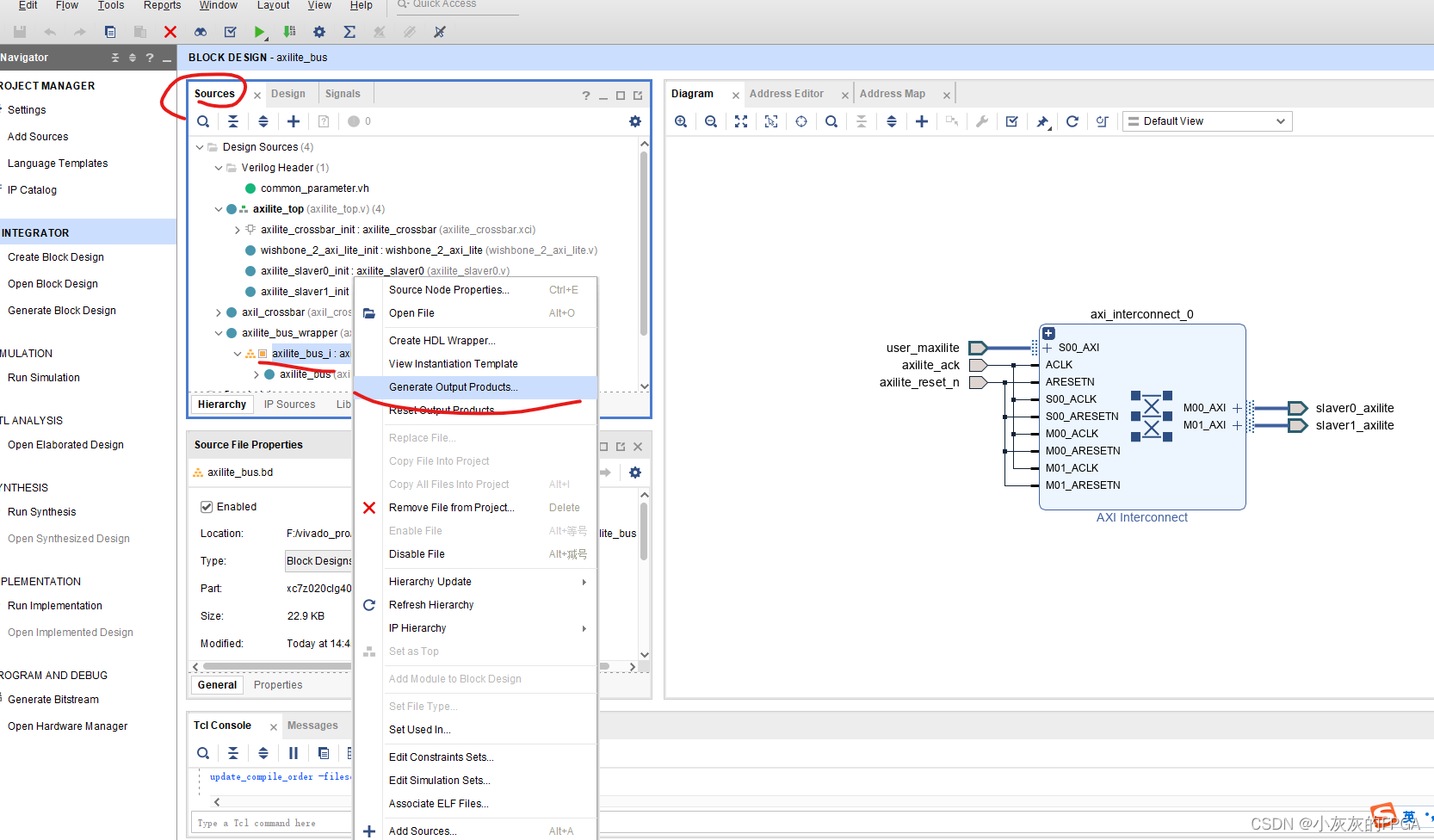

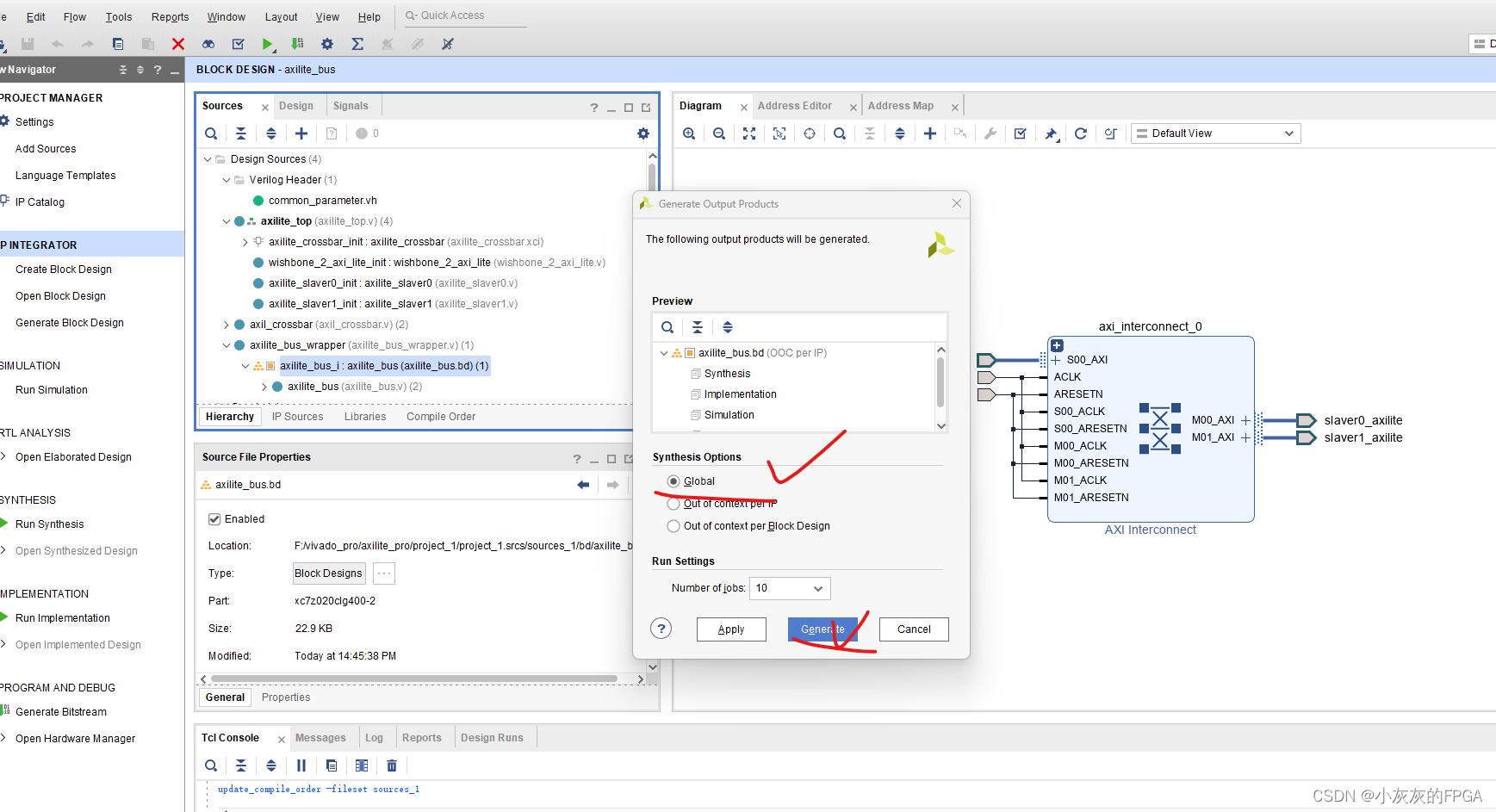

(13)Create HDL Wrapper以及Generate Output Porducts,个人习惯用Global,采用自顶而下的生成

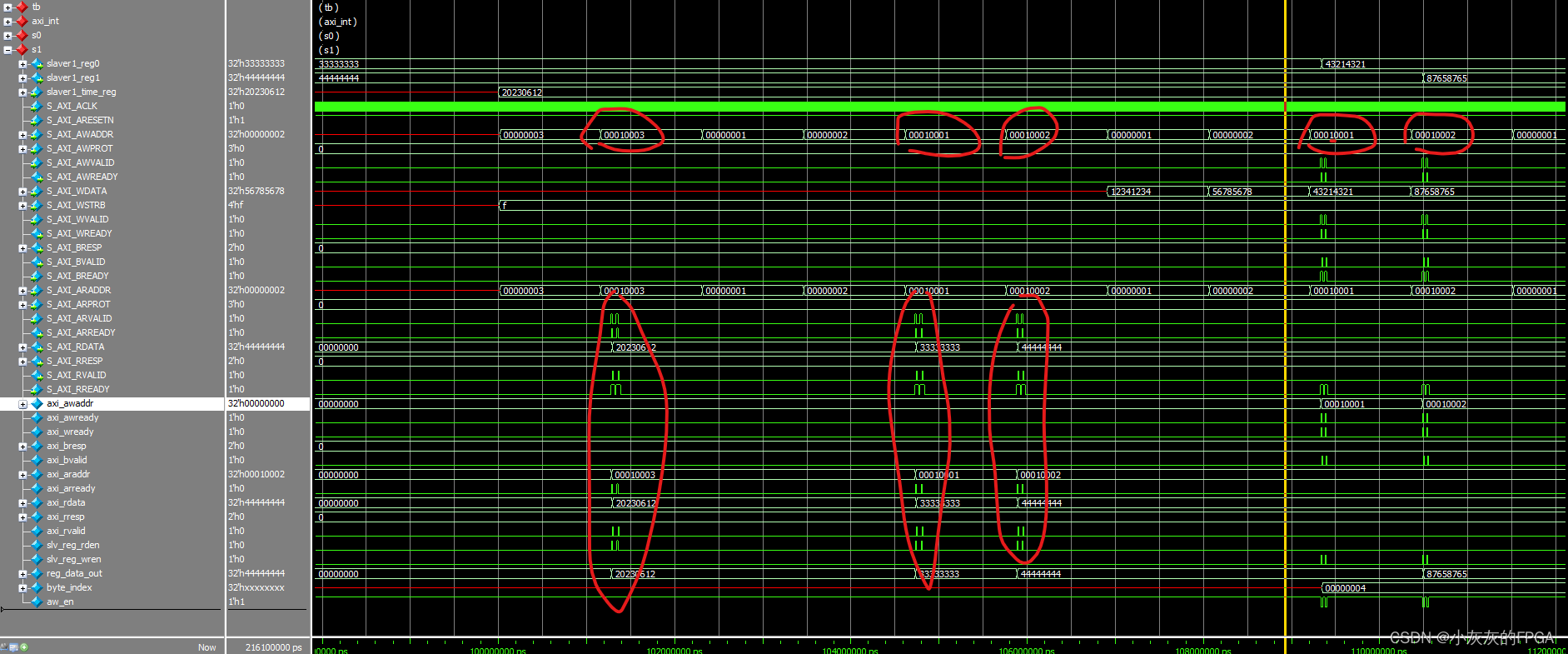

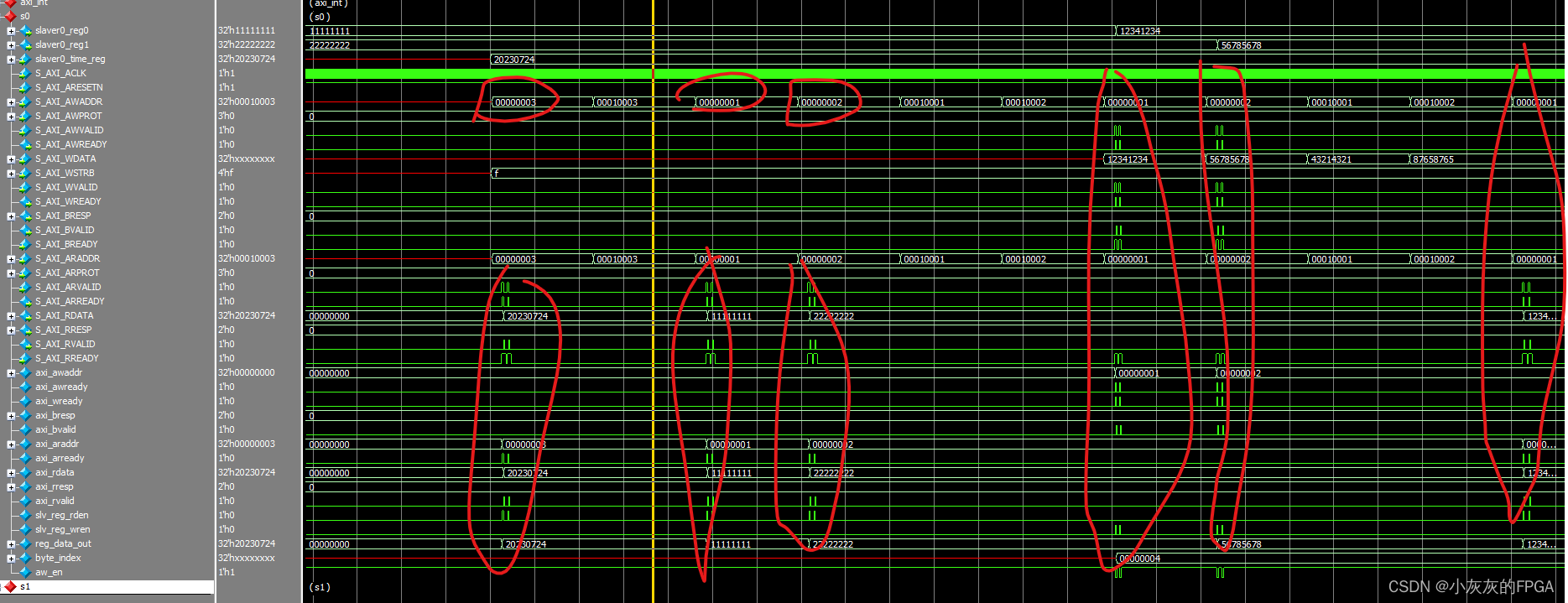

slaver0的AXIlite的仿真

slaver1的AXILite的仿真