一、创建除法ip核

vivado的除法器ip核有三种类型,跟ISE相比多了一个LuMult类型,总结来说就是

LuMult:使用了DSP切片、块RAM和少量的FPGA逻辑原语(寄存器和lut),所以和Radix2相比占用fpga资源更少;可以选择有符号或者无符号类型数据;但是位数有限,只能用于运算量小的时候,被除数位宽:2~17,除数位宽:2~11;只能选择余数模式

Radix2:使用FPGA逻辑原语(寄存器和LUTs);可以选择有符号或者无符号类型数据;被除数位宽:2~64,除数位宽:2~64;可以选择余数模式或者分数模式

High Radix:使用DSP切片和块ram;只能选择有符号类型(所以要扩展一位);被除数位宽:4~64,除数位宽:4~64;只能选择分数模式

tuser和tlast是两个输入信号,应该跟使能选择差不多

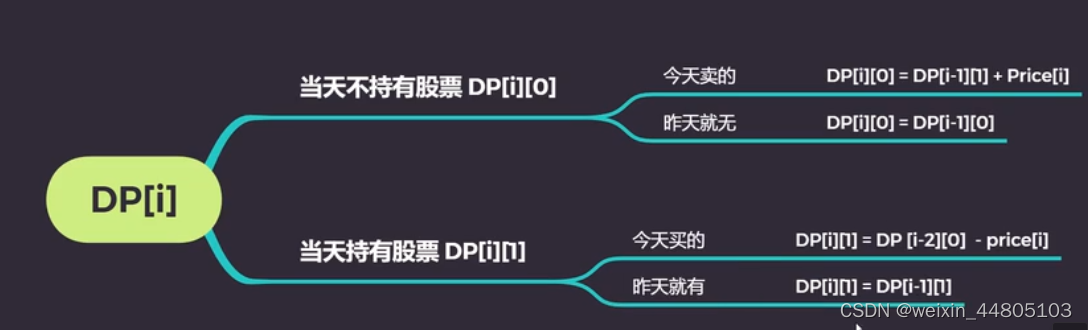

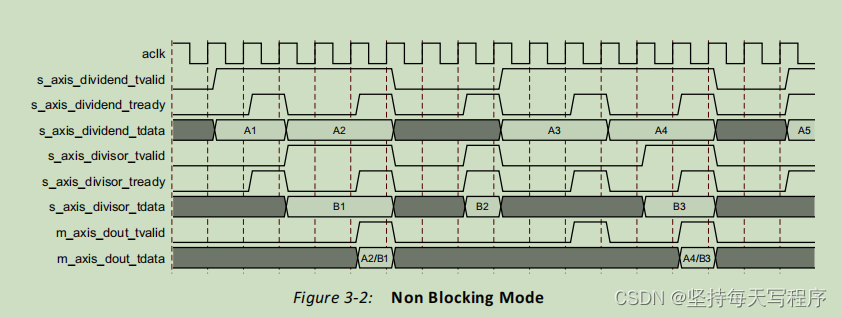

时序控制有两种模式:

valid是数据输入有效信号(in),ready是数据已经输入的标志信号(out),也就是说只有当除数和被除数同时输入成功,才会进行运算,并且在计算完成后在valid有效时,输出结果。但是在图中的dout_valid第二次有效时,这次的除数是无效的,所以要避免这个情况。

valid是数据输入有效信号(in),ready是数据已经输入的标志信号(out),但是在该模式下对于除数和被除数是否有效的判定是一样的,只是两个过程是独立的,相当于单独判断被除数和除数 是否有效,然后一次放到两个fifo当中,然后依次去计算。

二、编写VHDL程序

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity chufa0 is

PORT (

clk : IN STD_LOGIC;

nd_chuf0 : IN STD_LOGIC;

rdy0_chuf0 : OUT STD_LOGIC;

Tbkg : IN STD_LOGIC_VECTOR(15 DOWNTO 0);

rdy1_chuf0 : OUT STD_LOGIC;

Nbkg_Tobs : IN STD_LOGIC_VECTOR(23 DOWNTO 0);

rdy2_chuf0 : OUT STD_LOGIC;

Nbkg_Tobs_Tbkg : OUT STD_LOGIC_VECTOR(23 DOWNTO 0)

);

end chufa0;

architecture Behavioral of chufa0 is

COMPONENT div_gen_0

PORT (

aclk : IN STD_LOGIC;

s_axis_divisor_tvalid : IN STD_LOGIC;

s_axis_divisor_tready : OUT STD_LOGIC;

s_axis_divisor_tdata : IN STD_LOGIC_VECTOR(15 DOWNTO 0);

s_axis_dividend_tvalid : IN STD_LOGIC;

s_axis_dividend_tready : OUT STD_LOGIC;

s_axis_dividend_tdata : IN STD_LOGIC_VECTOR(23 DOWNTO 0);

m_axis_dout_tvalid : OUT STD_LOGIC;

m_axis_dout_tdata : OUT STD_LOGIC_VECTOR(23 DOWNTO 0)

);

END COMPONENT;

begin

chuf0 : div_gen_0

PORT MAP (

aclk => CLK,

s_axis_divisor_tvalid => nd_chuf0,

s_axis_divisor_tready => rdy0_chuf0,

s_axis_divisor_tdata => Tbkg,

s_axis_dividend_tvalid => nd_chuf0,

s_axis_dividend_tready => rdy1_chuf0,

s_axis_dividend_tdata => Nbkg_Tobs,

m_axis_dout_tvalid => rdy2_chuf0,

m_axis_dout_tdata => Nbkg_Tobs_Tbkg

);

end Behavioral;

三、编写仿真程序

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity chufa0_tb is

end chufa0_tb;

architecture Behavioral of chufa0_tb is

COMPONENT chufa0

PORT (

clk : IN STD_LOGIC;

nd_chuf0 : IN STD_LOGIC;

rdy0_chuf0 : OUT STD_LOGIC;

Tbkg : IN STD_LOGIC_VECTOR(15 DOWNTO 0);

rdy1_chuf0 : OUT STD_LOGIC;

Nbkg_Tobs : IN STD_LOGIC_VECTOR(23 DOWNTO 0);

rdy2_chuf0 : OUT STD_LOGIC;

Nbkg_Tobs_Tbkg : OUT STD_LOGIC_VECTOR(23 DOWNTO 0)

);

END COMPONENT;

signal clk : STD_LOGIC;

signal nd_chuf0 : STD_LOGIC;

signal rdy0_chuf0 : STD_LOGIC;

signal Tbkg : STD_LOGIC_VECTOR(15 DOWNTO 0);

signal rdy1_chuf0 : STD_LOGIC;

signal Nbkg_Tobs : STD_LOGIC_VECTOR(23 DOWNTO 0);

signal rdy2_chuf0 : STD_LOGIC;

signal Nbkg_Tobs_Tbkg : STD_LOGIC_VECTOR(23 DOWNTO 0);

-- Clock period definitions

constant clk_period : time := 10 ns;

begin

-- Instantiate the Unit Under Test (UUT)

uut: chufa0 PORT MAP (

clk => clk,

nd_chuf0 => nd_chuf0,

rdy0_chuf0 => rdy0_chuf0,

Tbkg => Tbkg,

rdy1_chuf0 => rdy1_chuf0,

Nbkg_Tobs => Nbkg_Tobs,

rdy2_chuf0 => rdy2_chuf0,

Nbkg_Tobs_Tbkg => Nbkg_Tobs_Tbkg

);

-- Clock process definitions

clk_process :process

begin

clk <= '0';

wait for clk_period/2;

clk <= '1';

wait for clk_period/2;

end process;

-- Stimulus process

stim_proc: process

begin

-- hold reset state for 100 ns.

nd_chuf0 <= '0';

wait for 25ns;

nd_chuf0 <= '1';

Nbkg_Tobs <= X"001008";

Tbkg <= X"0008";

wait for clk_period*1;

Nbkg_Tobs <= X"001118";

Tbkg <= X"0008";

wait for clk_period*1;

Nbkg_Tobs <= X"000000";

Tbkg <= X"0000";

wait for clk_period*5;

Nbkg_Tobs <= X"001008";

Tbkg <= X"1008";

wait for clk_period*1;

nd_chuf0 <= '0';

wait for clk_period*1;

nd_chuf0 <= '1';

Nbkg_Tobs <= X"001008";

Tbkg <= X"1008";

wait for clk_period*5;

Nbkg_Tobs <= X"101008";

Tbkg <= X"0008";

wait for clk_period*5;

Nbkg_Tobs <= X"001008";

Tbkg <= X"0008";

wait for clk_period*5;

nd_chuf0 <= '0';

wait for clk_period*1;

nd_chuf0 <= '1';

Nbkg_Tobs <= X"010108";

Tbkg <= X"0108";

wait for clk_period*1;

Nbkg_Tobs <= X"000000";

Tbkg <= X"0000";

wait for clk_period*5;

nd_chuf0 <= '0';

wait for clk_period*1;

nd_chuf0 <= '1';

Nbkg_Tobs <= X"010108";

Tbkg <= X"0108";

wait for clk_period*1;

nd_chuf0 <= '0';

wait for clk_period*1;

Nbkg_Tobs <= X"000000";

Tbkg <= X"0000";

wait for clk_period*5;

nd_chuf0 <= '1';

Nbkg_Tobs <= X"010108";

Tbkg <= X"0108";

wait for clk_period*2;

Nbkg_Tobs <= X"000000";

Tbkg <= X"0000";

nd_chuf0 <= '0';

wait for clk_period*5;

-- insert stimulus here

wait;

end process;

end Behavioral;

四、RTL图:

五、仿真图:

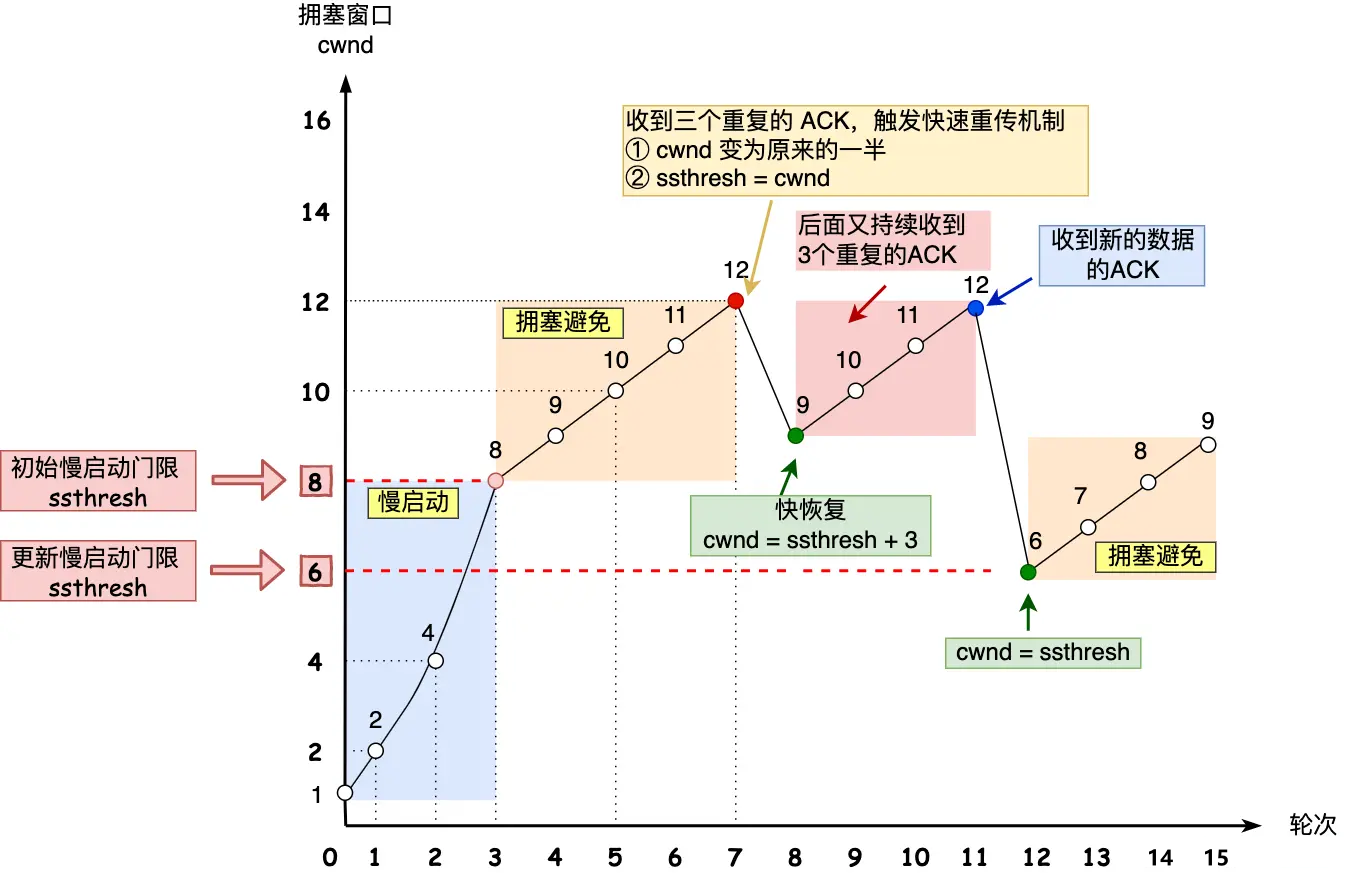

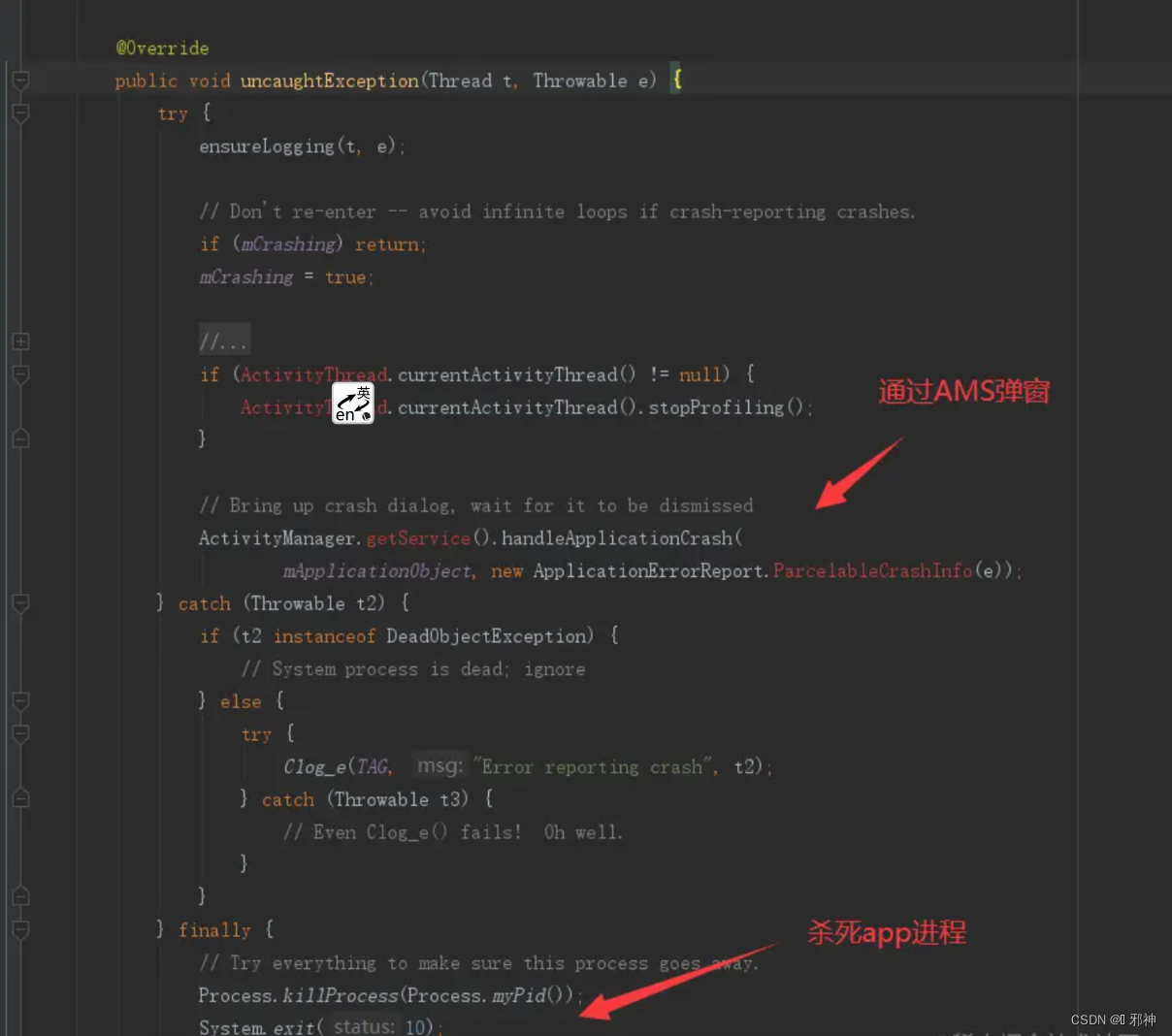

可以看到,因为除数和被除数的ready信号在使能无效时,一直为高,所以当除数被除数第一次被使能时,使能和ready信号是同时有效的,所以就直接在数据输入后的第三个时钟输出正确结果。而在第一个箭头位置,数据只维持了一个时钟,所以在ready信号有效时,数据已经发送变化,故没有产生正确结果。在第二个箭头处,由于数据输入的下一个时钟,使能信号没有了,所以也没有正确结果。因此,我们必须保证数据和使能信号要保持两个时钟,才能正确输出。(严格来说,就是使能信号必须有效至少两个时钟,而数据只要在ready信号有效时有效就行,但是由于测试结果和手册给的时序图不太一样,ready在空闲的时候是高,而手册上是低,所以只能说最好数据和使能信号同时保持两个时钟。不知道是不是我ip核设置的问题)

当除数或者被除数最高位是1时,就表示是负数(在该种模式下),所以结果也是不正确的。

综上,就是我们让使能信号两个时钟有效,就可以了,因为在这两个时钟里面,ready信号都只可能有效一次,然后数据两个时钟也是 一样的,就会在输出valid有效输出正确结果。

更正:之前说的输入使能和数据要保持至少两个时钟是错误的,根据ip手册里面只能得出在使能和tready信号都有效的时刻的数据才是输入数据,但是至于要使能之后几个时钟tready才变成有效是不确定的(tready是out信号),所以如果只是单纯用除法ip,可以使用第二种阻塞模式,将使能输入信号一直有效,就可以计算所有数据。但如果是要和其他模块进行级联计算,那么就可以使用非阻塞模式,然后通过使用状态机去使能除数和被除数的信号,在拉高使能信号后,进入下一个状态,并开始判断tready是否有效,有效之后就拉低使能信号,就可以只计算一次呢,注意数据的周期就要尽可能大于tready拉高的时间。