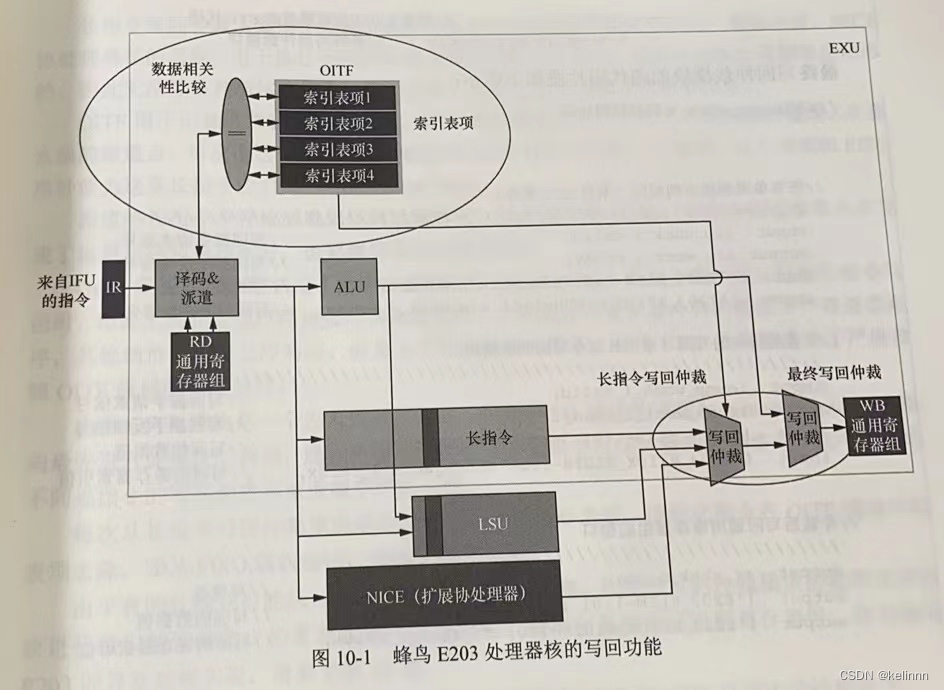

一、 蜂鸟E203处理器的写回硬件实现

核心思想如下

- 将指令划分为单周期指令和长指令两大类

- 将长指令的交付和写回分开,使得即使执行力多周期的长指令也不会阻塞流水线,妨碍单指令

主要包含最终写回仲裁、长指令写回仲裁

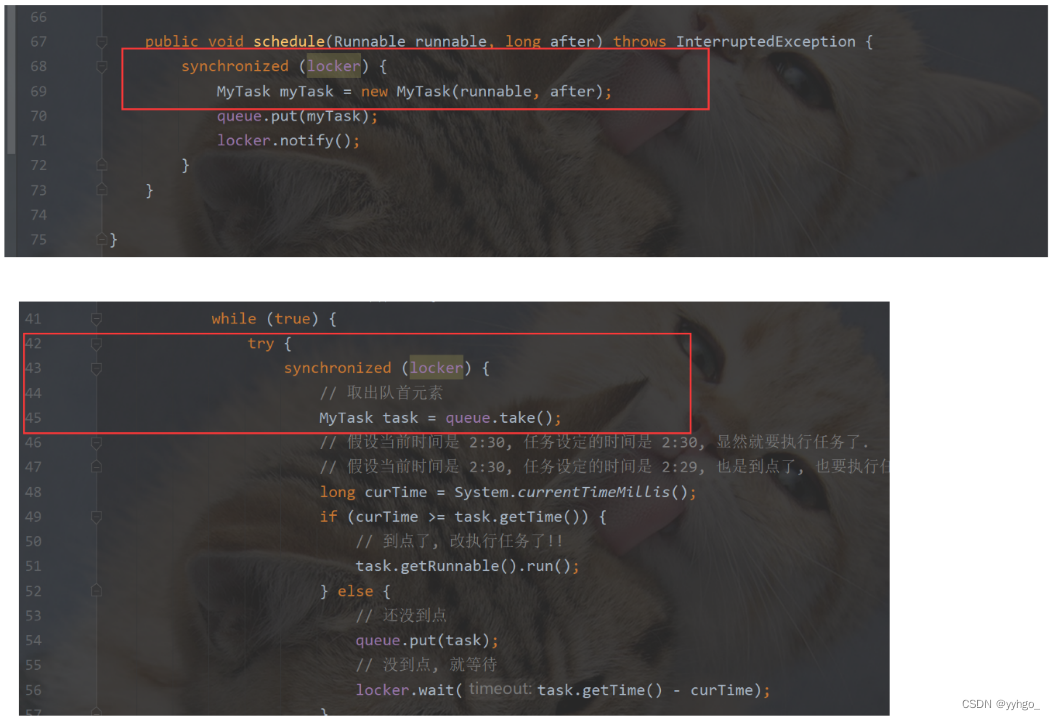

最终写回仲裁

长指令的写回比单周期指令的写回具有更高的优先级,在没有长指令写回的空闲周期,后面的单周期指令可以随时写回,乱序写回。

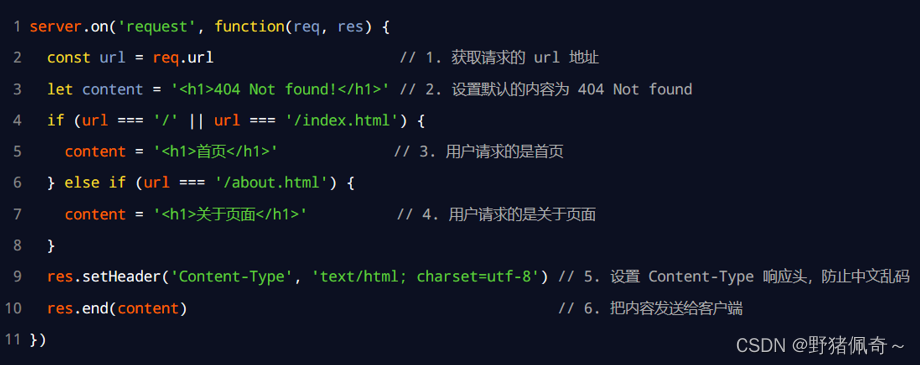

最终写回仲裁的部分源代码如下所示

module e203_exu_wbck(

//////////////////////////////////////////////////////////////

// The ALU Write-Back Interface

input alu_wbck_i_valid, // Handshake valid //alu表明有指令需要写回

output alu_wbck_i_ready, // Handshake ready //wbck向alu返回读写反馈请求

input [`E203_XLEN-1:0] alu_wbck_i_wdat, // 从alu写回的数据值

input [`E203_RFIDX_WIDTH-1:0] alu_wbck_i_rdidx, // 写回的寄存器索引值

// If ALU have error, it will not generate the wback_valid to wback module

// so we dont need the alu_wbck_i_err here

//////////////////////////////////////////////////////////////

// The Longp Write-Back Interface

input longp_wbck_i_valid, // Handshake valid //表明有长指令需要写回

output longp_wbck_i_ready, // Handshake ready //wbck向longpwbck返回读写反馈请求

input [`E203_FLEN-1:0] longp_wbck_i_wdat, // 从longpwbck写回的数据值

input [5-1:0] longp_wbck_i_flags, // 从longpwbck写回标志

input [`E203_RFIDX_WIDTH-1:0] longp_wbck_i_rdidx, // 从longpwbck写回的寄存器索引

input longp_wbck_i_rdfpu, // 从longpwbck写回到FPU的标志

//////////////////////////////////////////////////////////////

// The Final arbitrated Write-Back Interface to Regfile

output rf_wbck_o_ena, // 写使能

output [`E203_XLEN-1:0] rf_wbck_o_wdat, // 写回的数据值

output [`E203_RFIDX_WIDTH-1:0] rf_wbck_o_rdidx, // 写回的寄存器索引

input clk,

input rst_n

);

OITF模块和长治零写回仲裁模块

这两个模块完成所有长指令的写回操作。

执行不同的长指令所需要的周期数不同,我们使用OITF来纪录长治零的先后关系。OITF红的每个表项都带有一个指针(Instruction Tag),每个长指令都会带着这个ITAG。只要没有发生寄存器冲突都可以乱序写回,但是会增加硬件设计。

总结

E203如果只考虑单周期指令则为“顺序发射、执行写回”

如果仅讨论长指令“顺序发射、乱序执行、顺序写回”

如果都考虑“顺序发射、乱序执行、乱序写回”

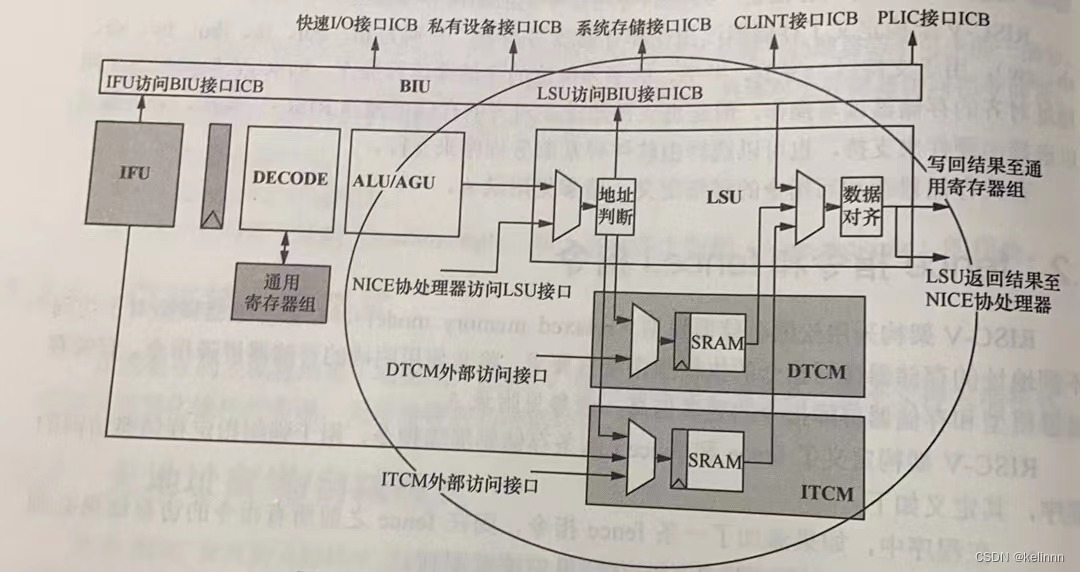

二、 蜂鸟E203处理器的存储器

没有缓存

有一些低功耗处理器是不使用缓存的主要有以下几个原因

- 无法保证实时性。有可能发生缓存不命中(cache miss),这就需要到外部存储器读取数据,所以一般使用ITCM和DTCM

- 代码量较少

- 面积和功耗考虑

ARM CortexM0、3、4都没有配备缓存 7配有缓存,是双发射6级流水线的CPU

一定要有存储器

哈佛体系结构特点

- 将程序和数据存储在不同的存储空间中国,每个存储器独立编址,独立访问

- 与两个存储器相对应的是两条独立的指令总线和数据总线。这样可以使得处理器在一个时钟周期内同时获得指令字和操作数

- 取址和执行可以并行执行

ITCM和DTCM

M3和M4就配置了这两个,原因如下

- 能够保证实时性,不存在缓存不命中的情况,延迟是可知的

- 满足代码量要求

- 面积功耗小

RISC-V对于存储器访问指令的简化

- 仅支持小端格式

- 无地址自增自减模式

- 无一次读多个数据和一次写多个数据的指令

AGU:负责读和写指令,以及A拓展指令集生成存储器访问地址

LSU:主要作为存储器访问的控制模块