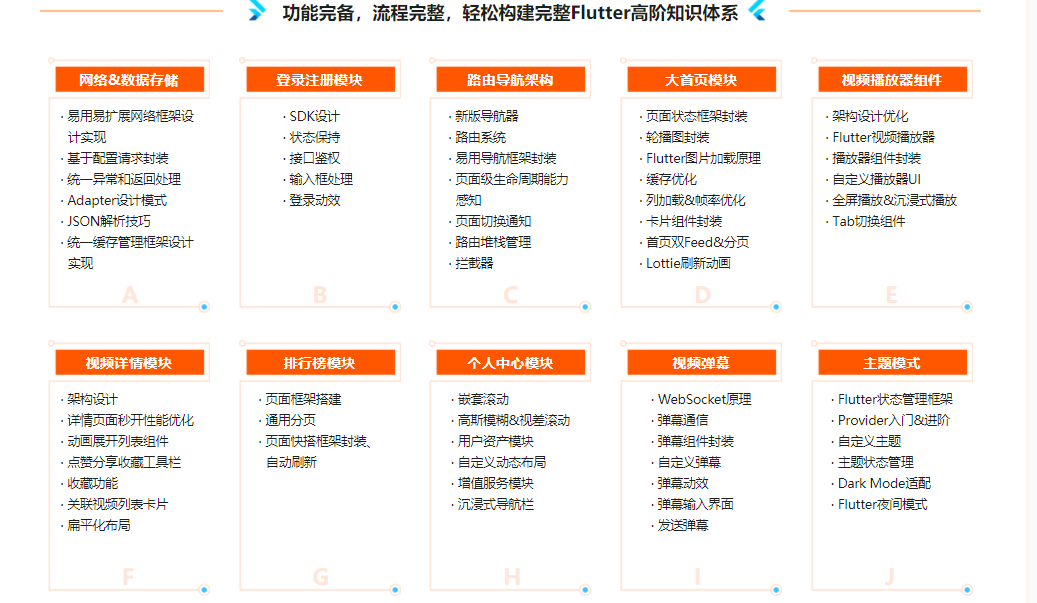

文章目录

- 简介

- 门

- 与门

- 或门

- 非门

- 异或门

- ALU

- 加法

- 半加器

- 全加器

- 8位加法器

- 减法

- 补码

- 8位补码器

- 8位减法器

- 存储

- 锁存器

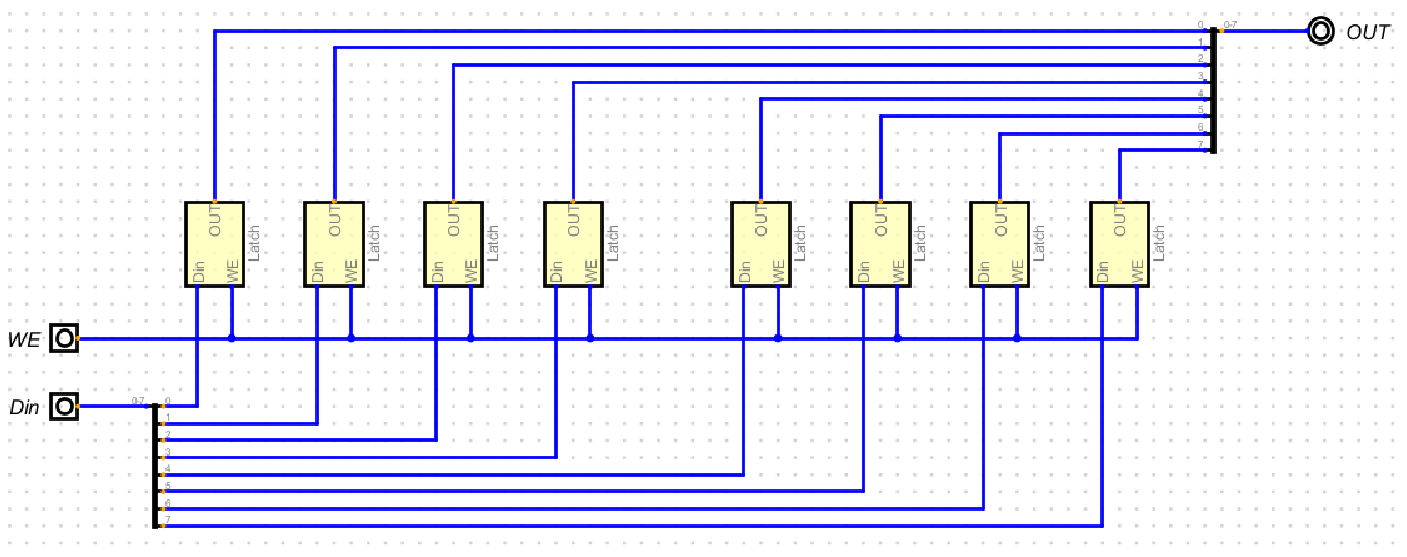

- 8位锁存器

- 带边沿触发的锁存器

- 内存

- 内存单元

- 16位内存

- CPU

- PC程序计数器

- CPU连接

- 自制乘法器

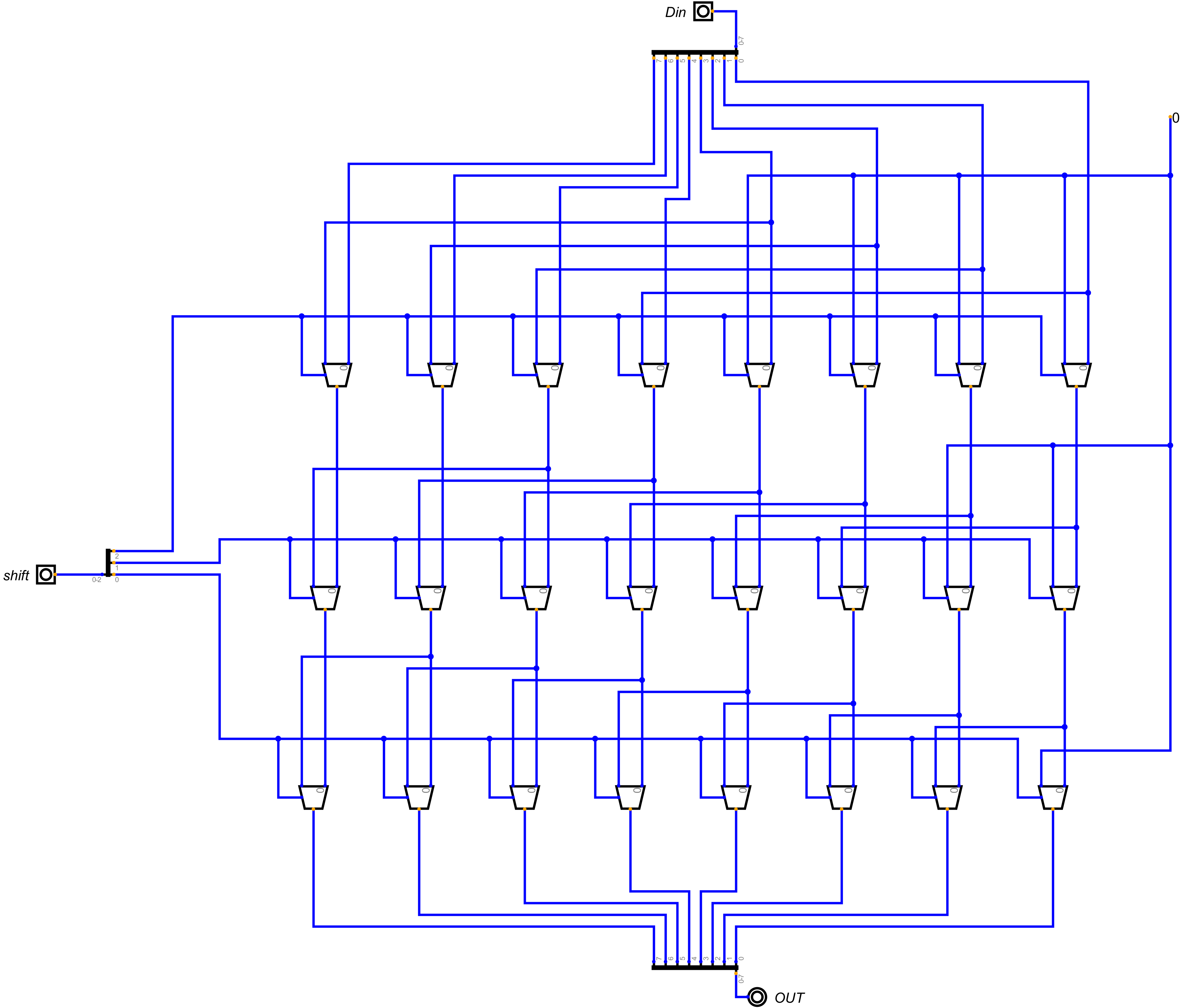

- 移位

- 8位乘法器

- 自制除法器

- 比较

- 一位比较

- 8位比较

- 8位除法器

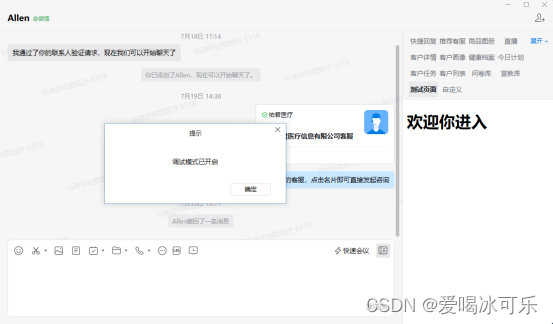

简介

黑马最近出了个制作计算机的视频:https://www.bilibili.com/video/BV1nV411T7U3

我看了看,感觉不错,跟着做了个,扩展了减法,乘法,除法,文件在文末,大佬轻喷

门

与门

两个继电器同时控制输出

或门

两个继电器都直接连接输出

非门

双掷继电器反接,默认连通

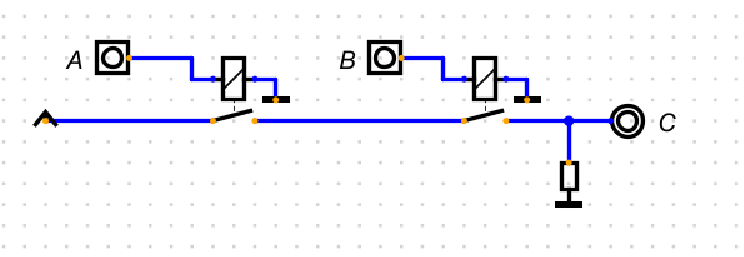

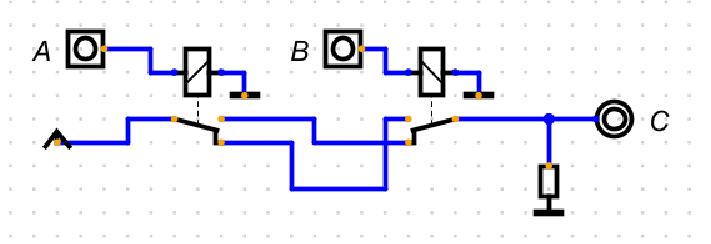

异或门

两个双掷继电器镜像交叉相连

ALU

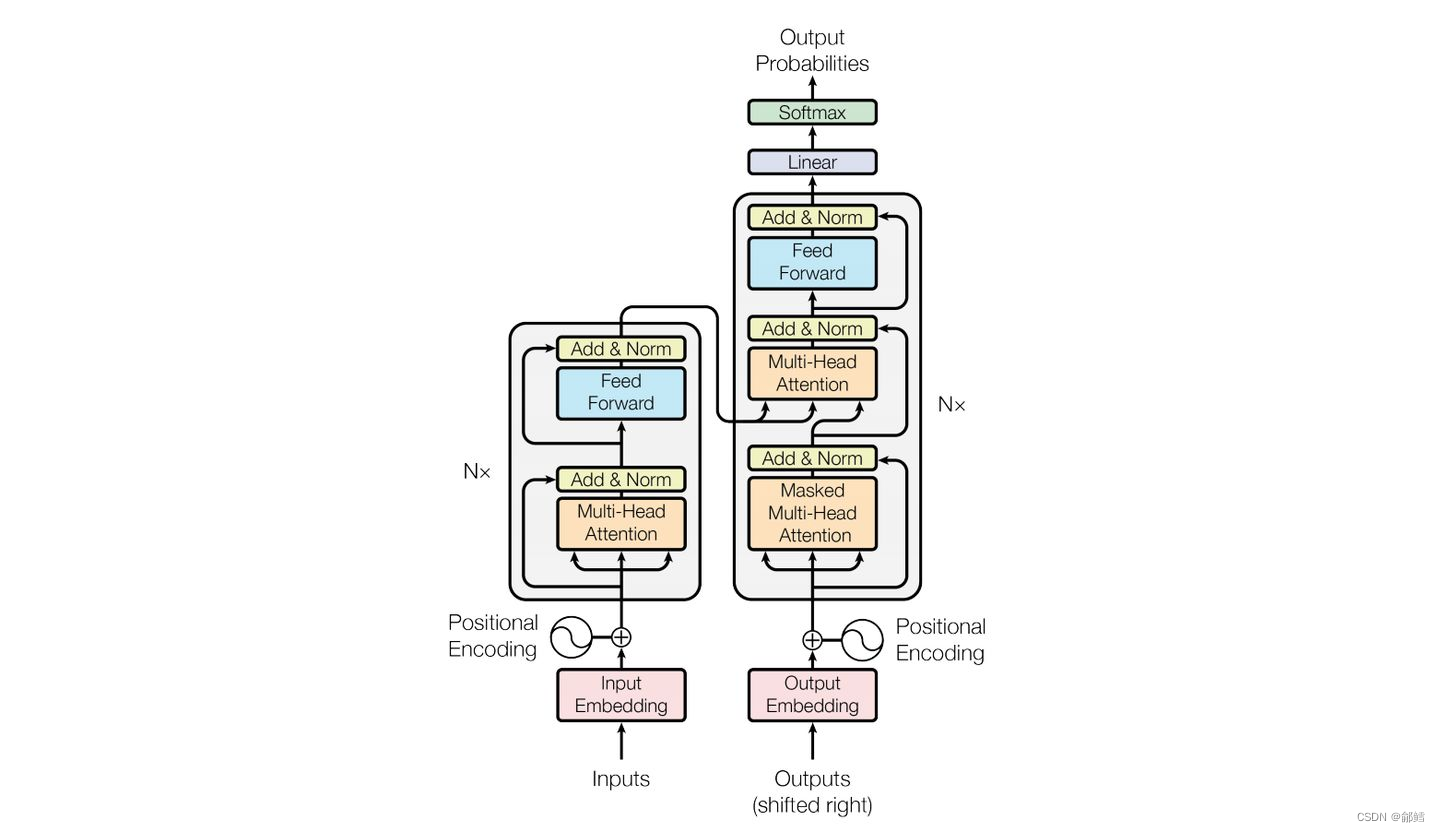

即算术逻辑单元,有两个单元:算数单元(负责加减乘除等运算)和逻辑单元(负责与或非等判断)

加法

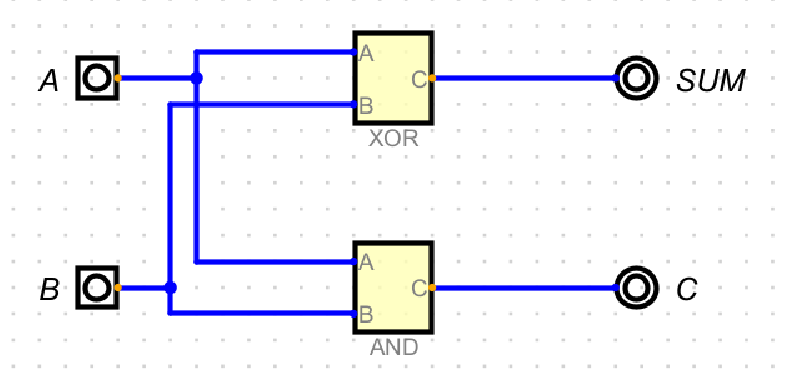

半加器

只能处理一位的加法,利用异或门输出SUM(输入相同时输出0,不同时输出1),利用与门输出进位C(全为1时才输出1)

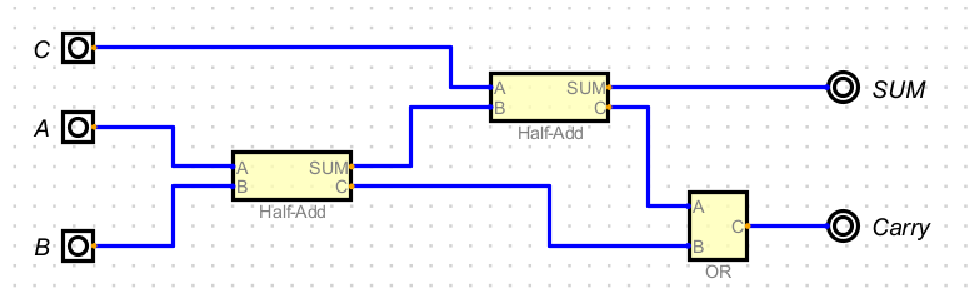

全加器

能处理包含进位的一位的加法,先用半加器处理被加数和加数,再用半加器处理结果和输入的进位的加法,得到最终结果,两次半加有一个进位则最终结果进位

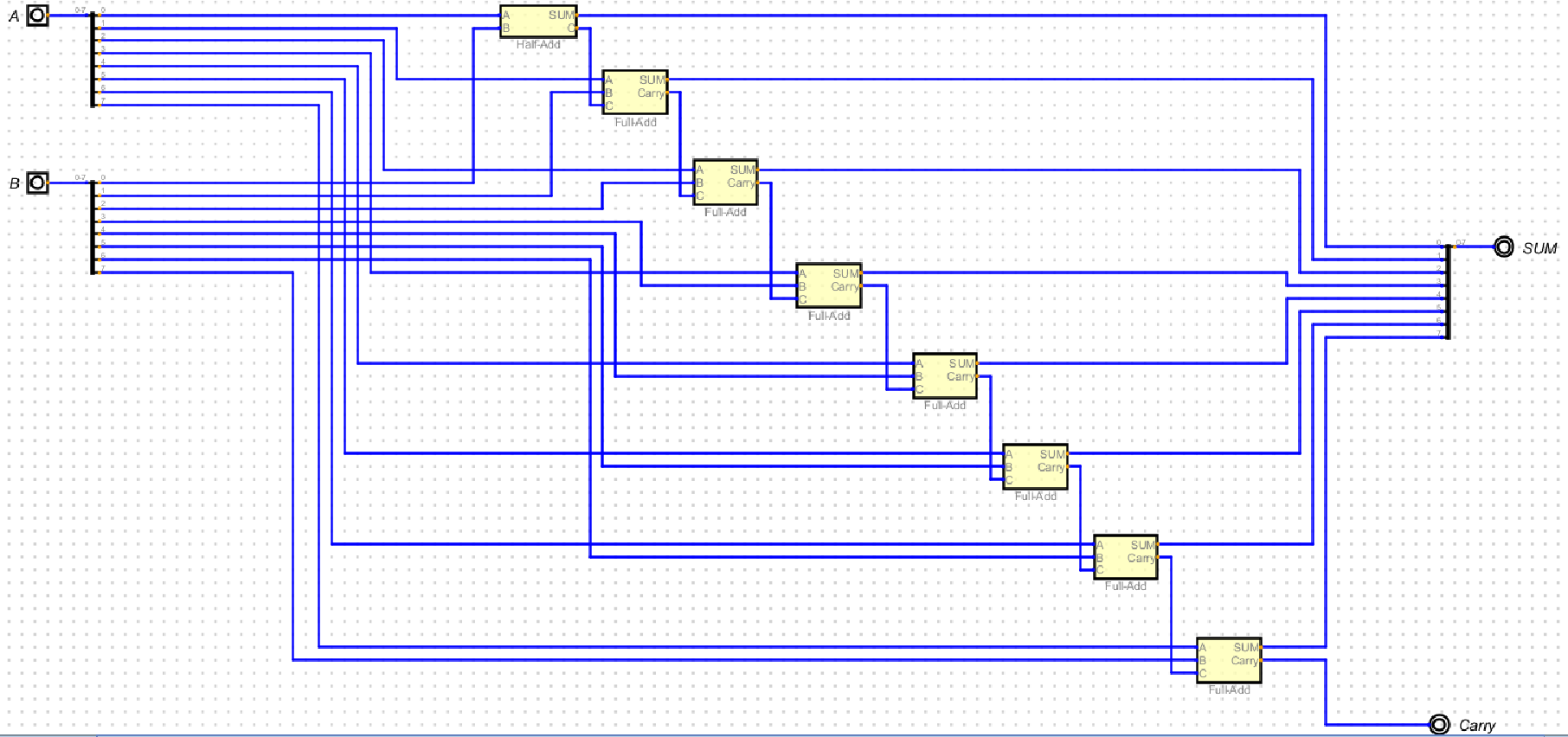

8位加法器

第0位无进位输入,使用半加器,其他位有进位输入,使用全加器,最终聚合出结果

减法

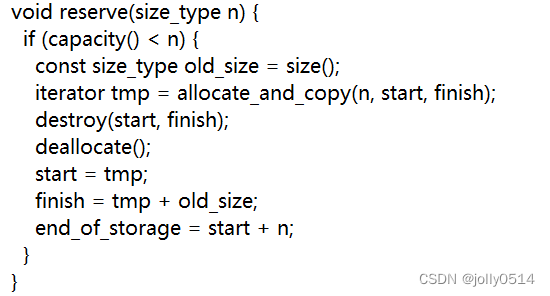

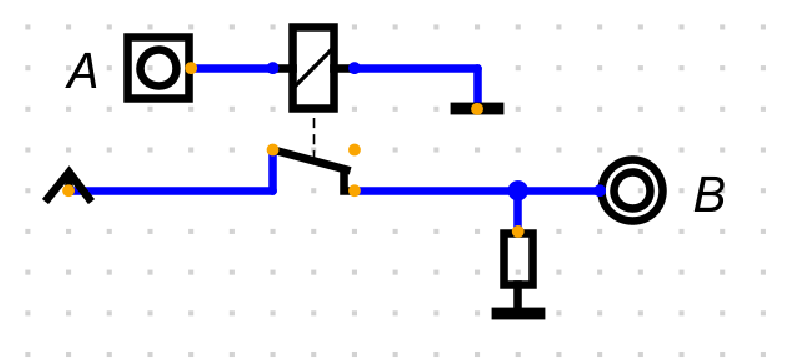

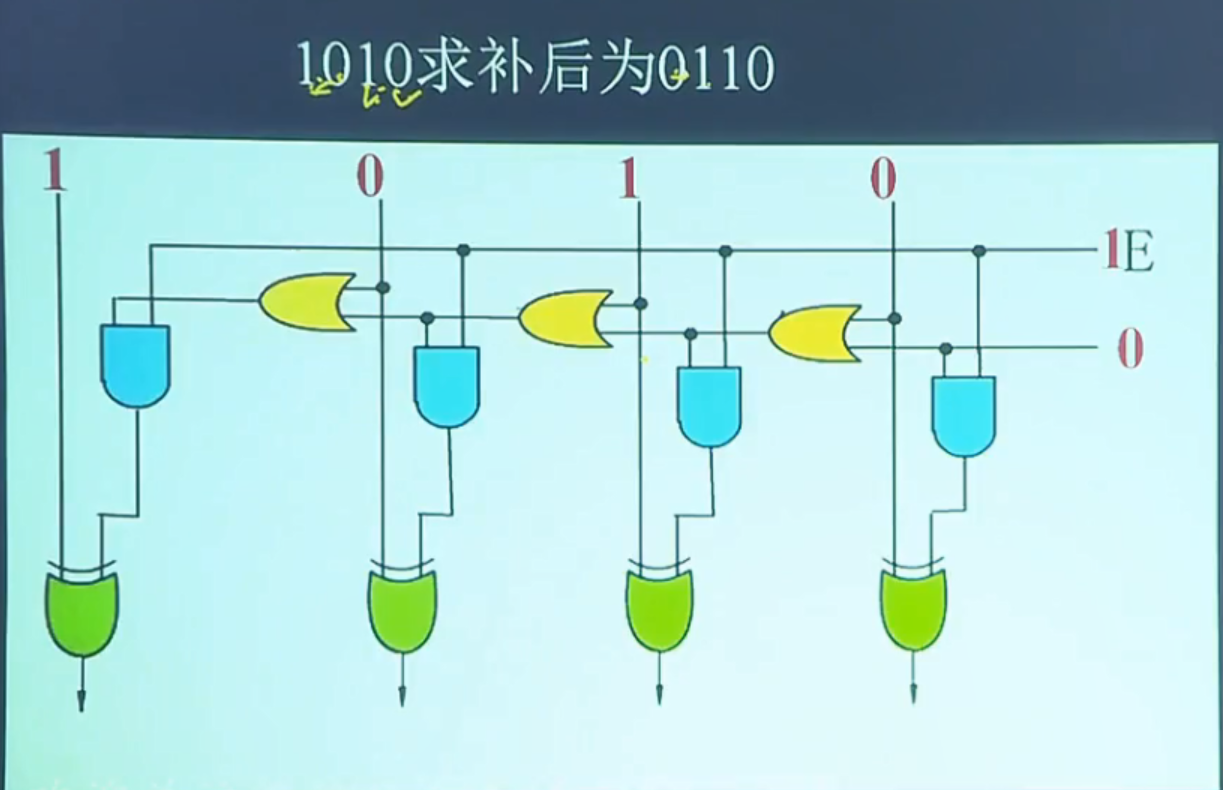

补码

二进制减法使用被减数加上减数的补码实现,补码=原码取反+1

当E为1时,是求补码,例如1010输入,异或输出0110

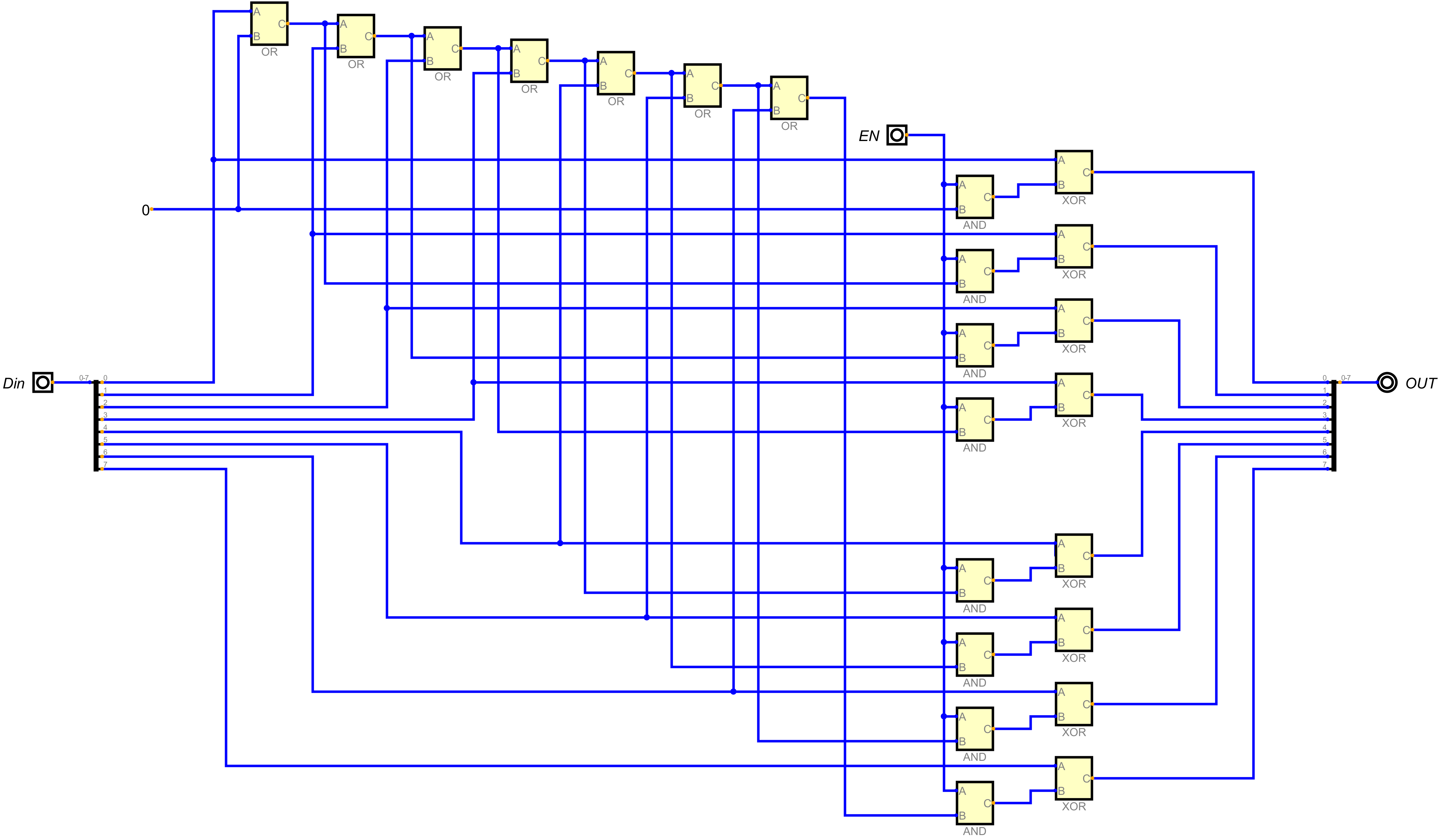

8位补码器

根据上图扩展得到

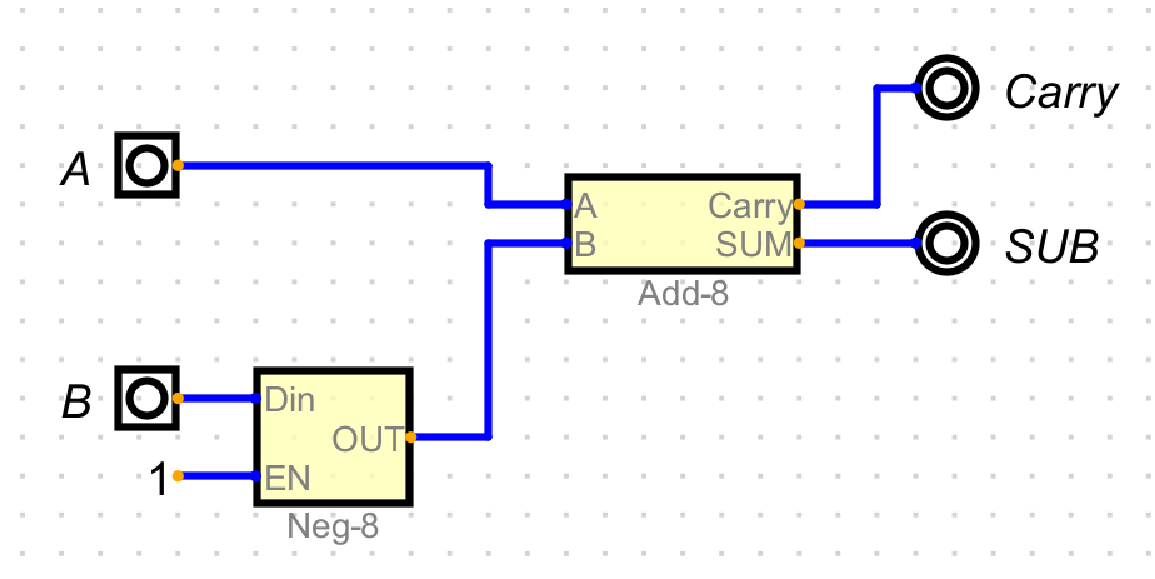

8位减法器

存储

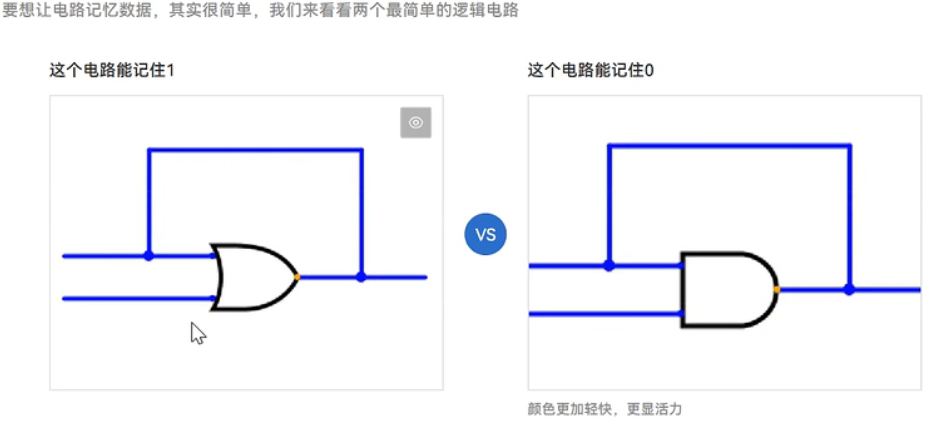

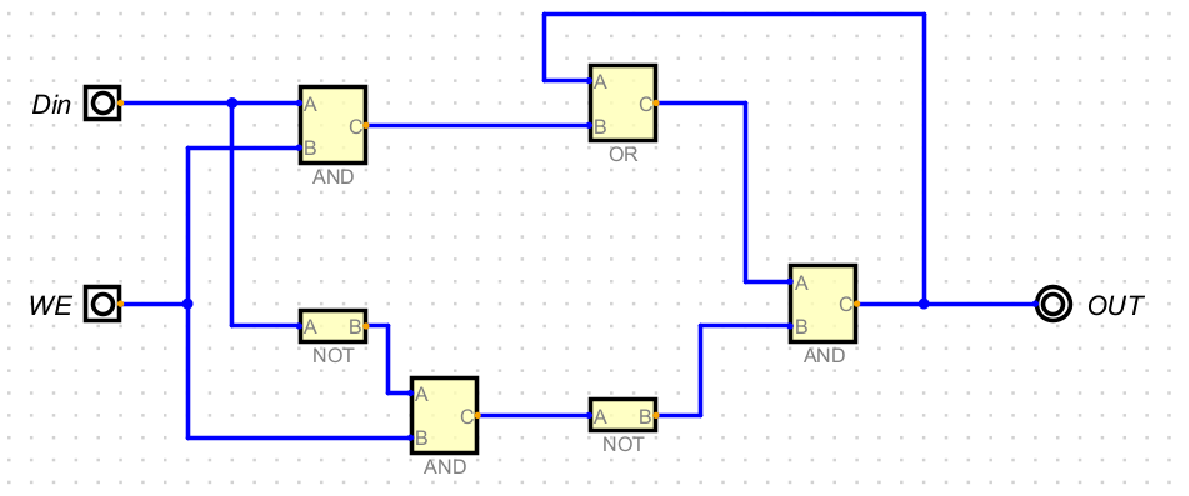

锁存器

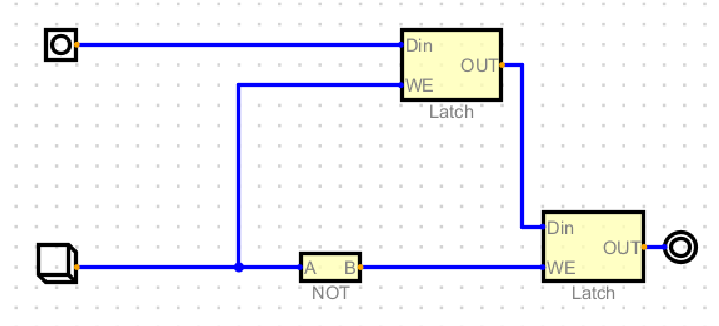

两个反馈门电路结合即可做出锁存器

当Din和WE(写使能)同为1,则反馈或门(记住1的)输入1。下面的电路目的是筛选出Din为0,WE为1的输入情况,此时反馈与门(记住0的)输入0

8位锁存器

带边沿触发的锁存器

此时这里的按钮/时钟输入就是WE,带时钟的目的是保证器件同步动作,使得操作更有效率

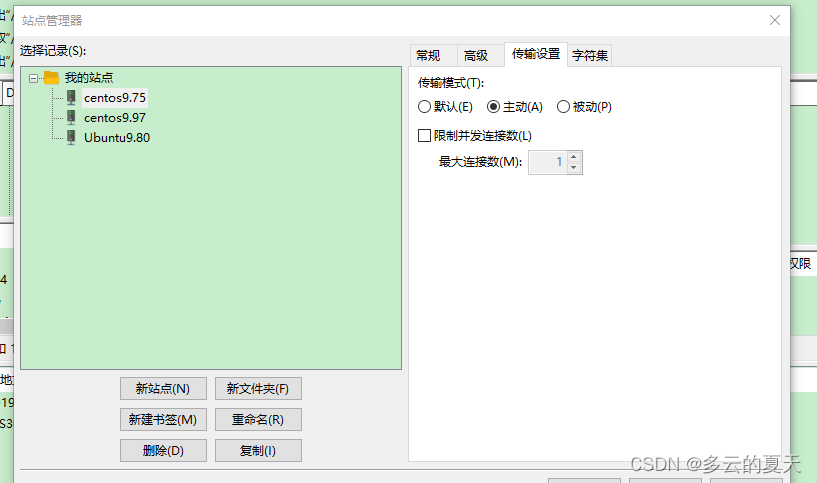

内存

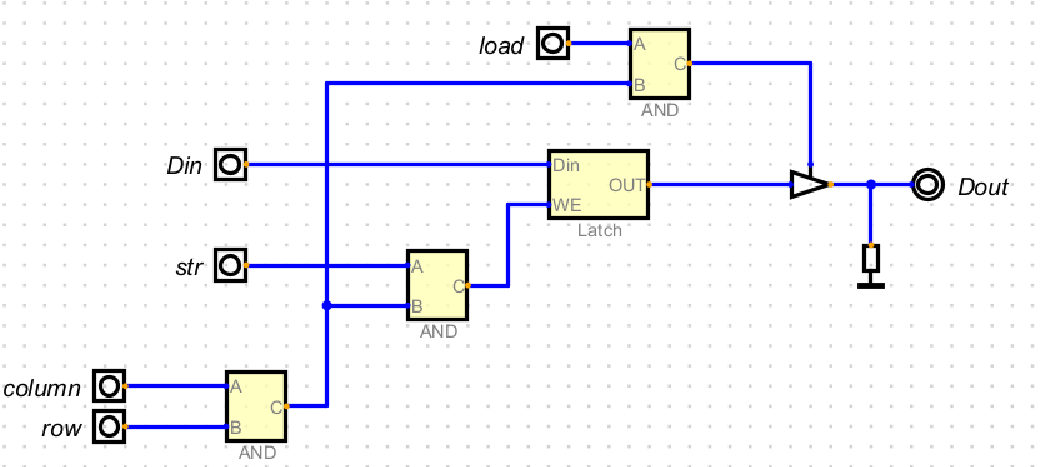

内存单元

先根据行和列(row, column)选择单元,选中后才能写(str)或读(load),选中并load驱动输出,下拉电阻默认低电平输出。

16位内存

输入address为4位地址,LUT查找表处理输入输出的映射关系,使0 ~ 15的输入分别对应到16个内存单元上

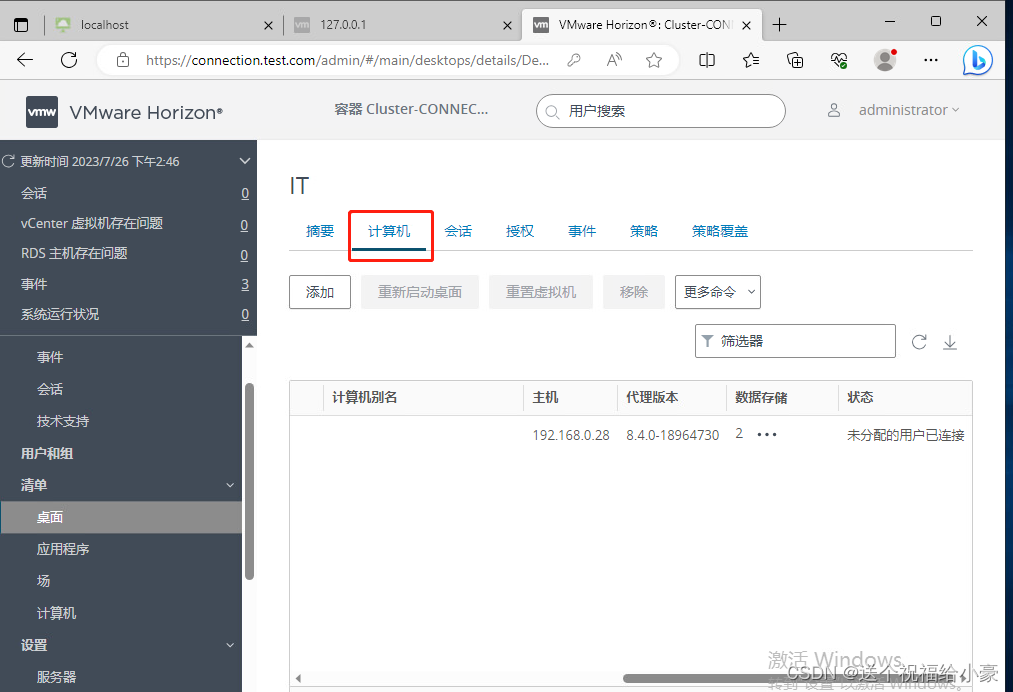

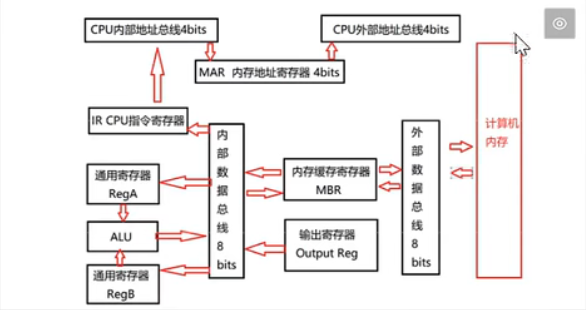

CPU

PC程序计数器

时钟输入上升沿时,4位寄存器中的值被取出加一,再放回寄存器中输出出来

CPU连接

执行步骤:

-

取指(令)阶段——所有指令相同

- PC程序计数器初始为0,其中的数据通过CPU内部地址总线发给MAR内存地址寄存器

- PC程序计数器+1

- MAR内存地址寄存器中的值(内存中指令的地址编号)通过CPU外部地址总线发给内存(EEPROM),内存输出指令通过CPU外部数据总线给MBR内存缓存寄存器

- MBR内存缓存寄存器通过CPU内部数据总线将数据交给IR指令寄存器

-

译码和执行阶段

- IR指令寄存器输出给LUT查找表,查出对应的操作集(开闭一系列模块的输入)

- 通过开闭一系列输入实现不同操作,如运算、从内存中取数据等

-

下一个取指阶段

一个指令对应的操作步骤完成后(由一个计数器控制步骤的进行——计数器接入LUT查找表),控制操作步骤的计数器溢出,从零开始计数,PC程序计数器(此时已+1)发数据给MAR内存地址寄存器

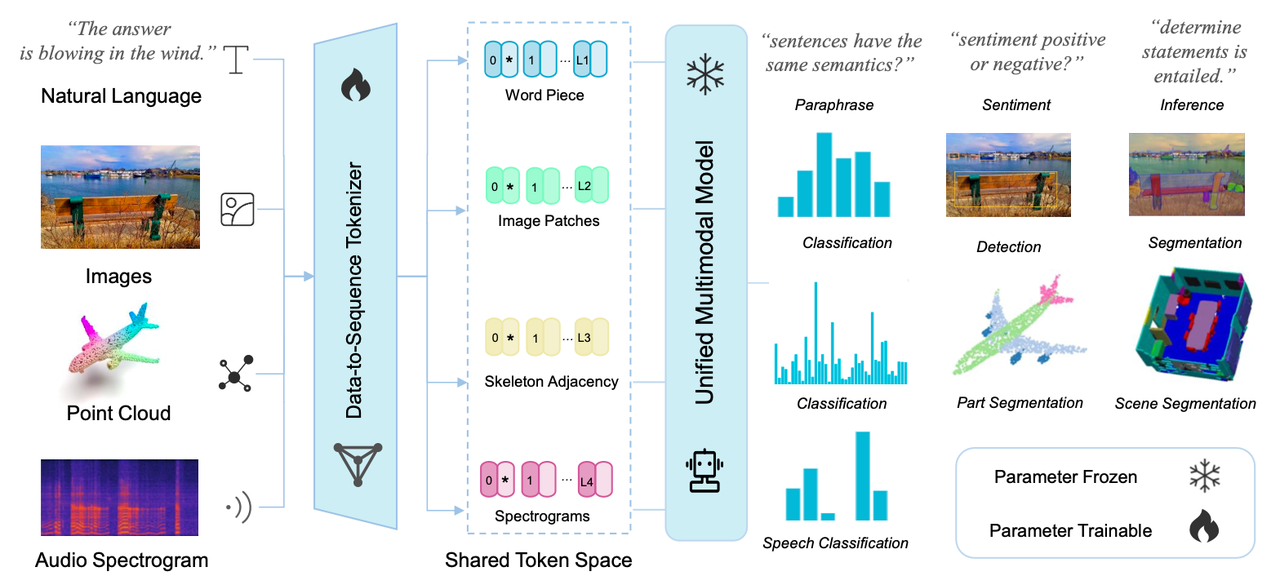

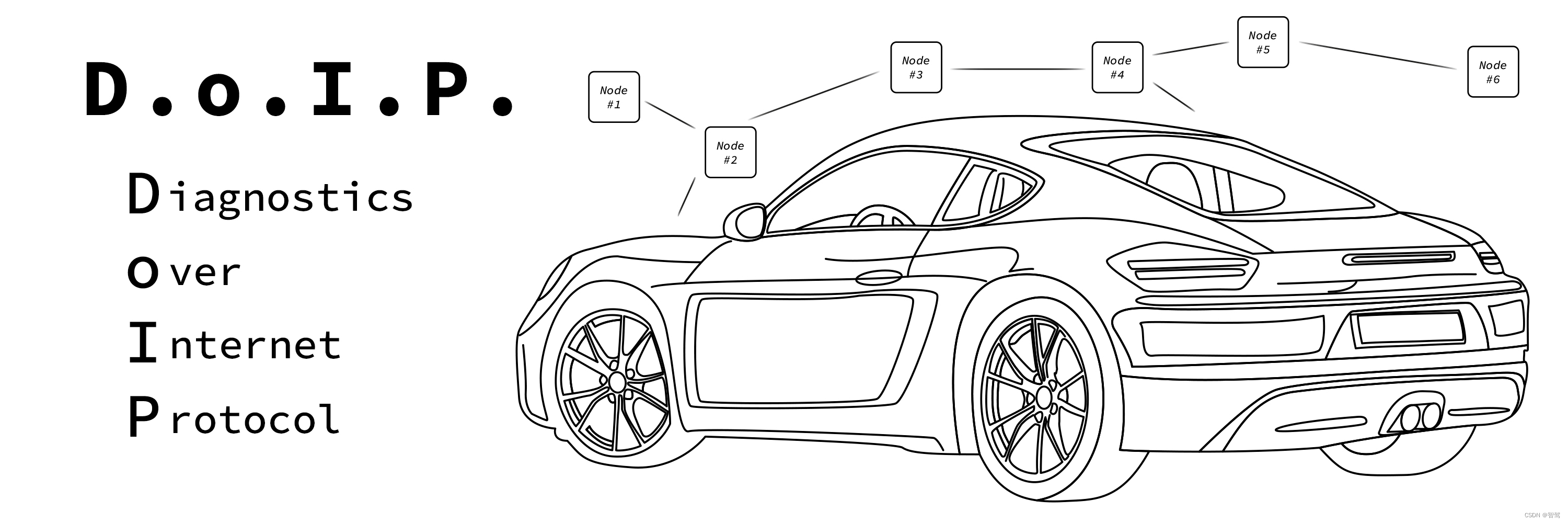

自制乘法器

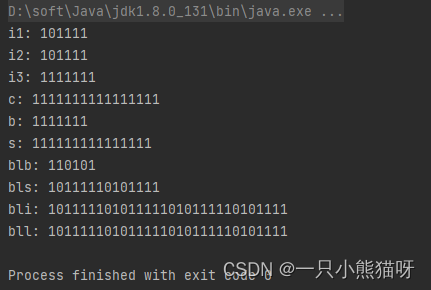

二进制乘法原理

PS:上图中被乘数是0111,乘数是0101,算式为0111 * 0101

移位

经修改可变成左移

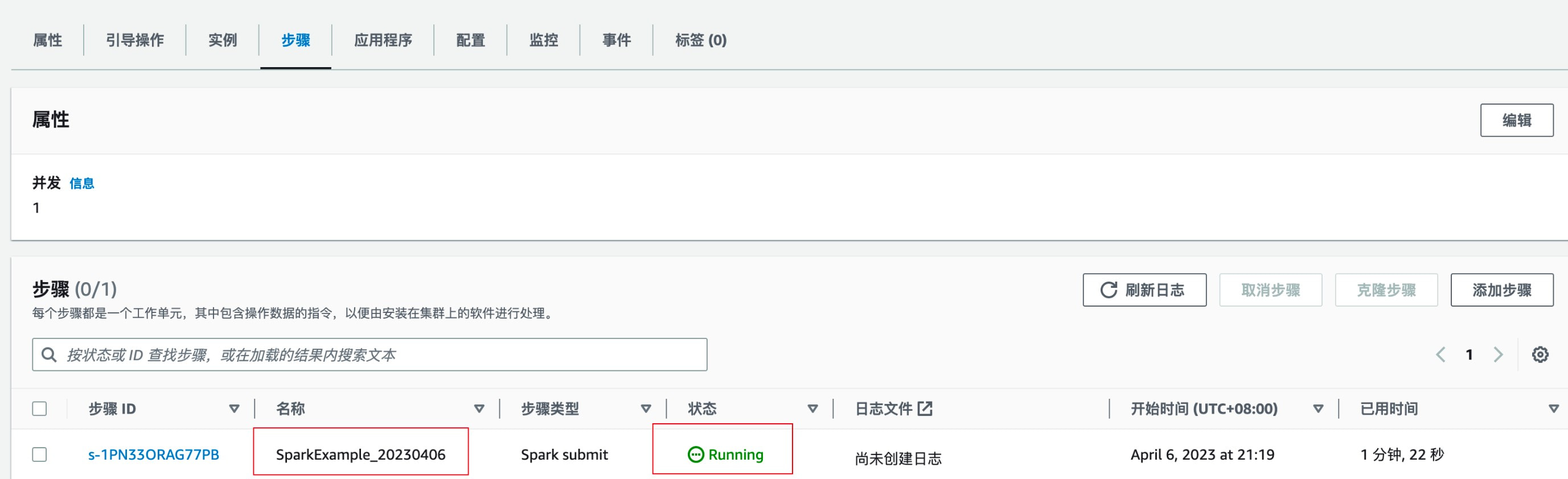

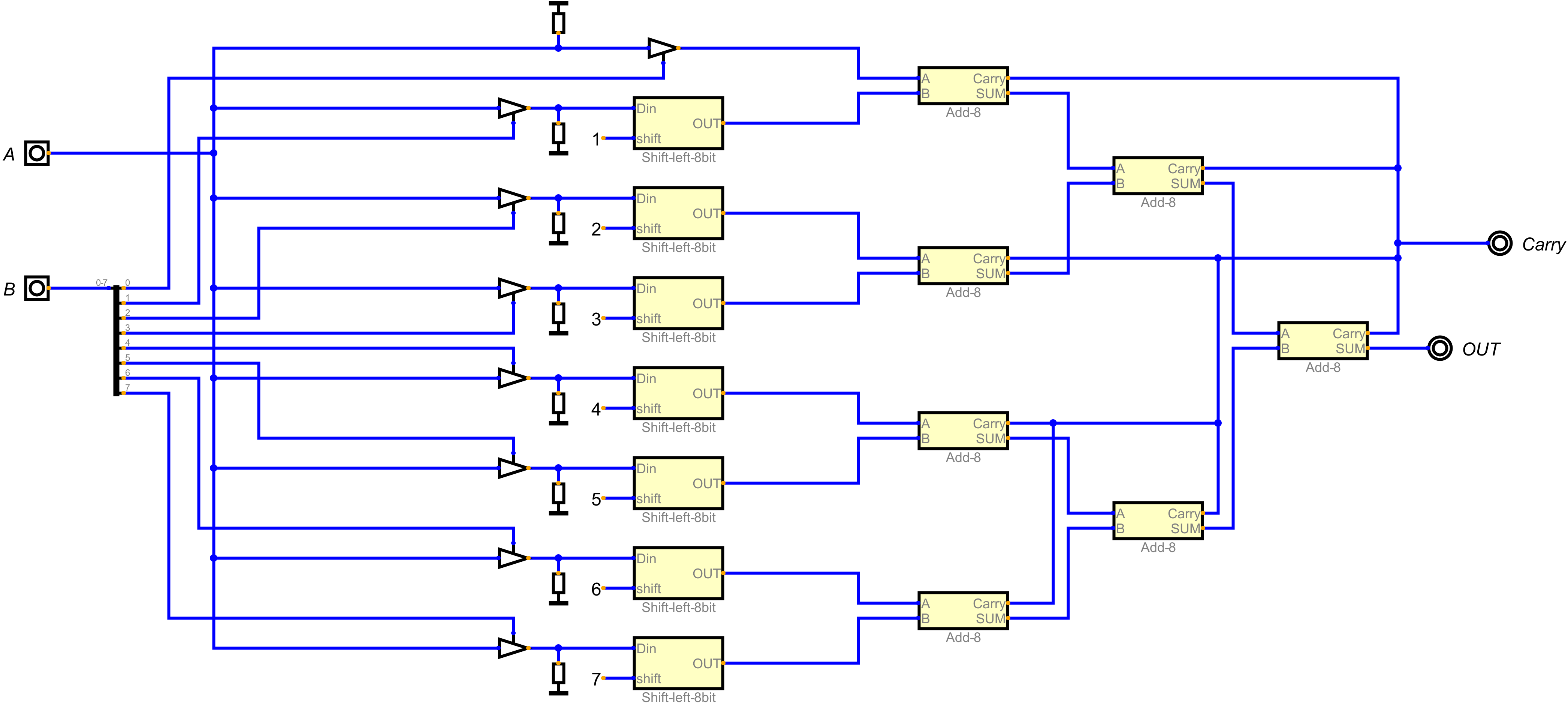

8位乘法器

乘数B的各个位分别控制被乘数A是否左移1 ~ 7位,不左移则此位的结果为0,最后各位结果相加,输出

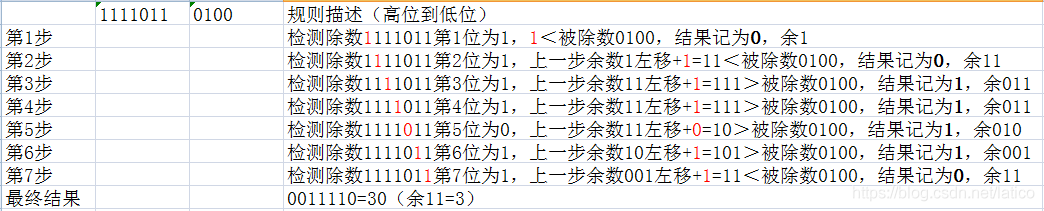

自制除法器

二进制除法原理

PS:被除数为1111011,除数为0100,算式为1111011 / 0100

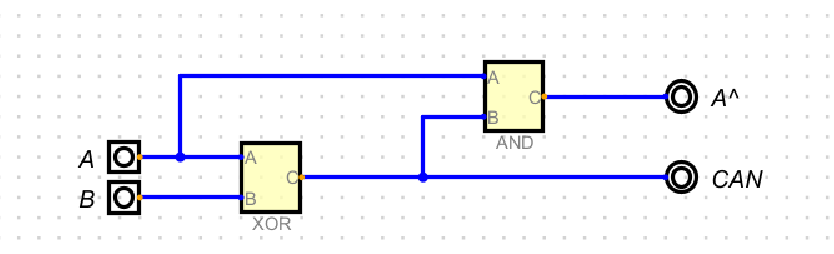

比较

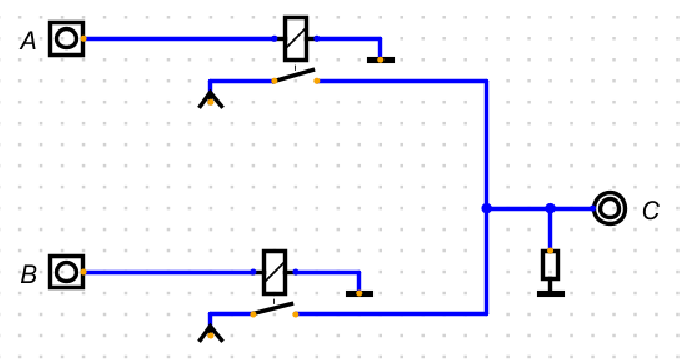

一位比较

异或门先判断是否相同,从而输出能否比较,能比较就给与门输入1,同时AB只有一个1,则与门输出与A输入相同,A ^ 为1表示A大

8位比较

拆成两个4位比较器,CAN驱动1位比较结果,同时CAN又被邻高位控制,或门接收4位中两个高位的CAN,输出1时表示高位已经完成比较了,低位不需要比较。两个4位比较器结合又用到两个或门,接收(4、5位)和(6、7位与的结果),然后控制。

8位除法器

性能很差,只是翻译了二进制除法原理,时不时会报错,可能是软件Bug

最终组合为ALU:

软件及子电路图:

链接: https://pan.baidu.com/s/1A9UI37GTXxFWFdGyMnV5nw?pwd=9cn6 提取码: 9cn6 复制这段内容后打开百度网盘手机App,操作更方便哦