文章目录

- CPSR

- SPSR

- SPSR

- CPSR 各个位含义

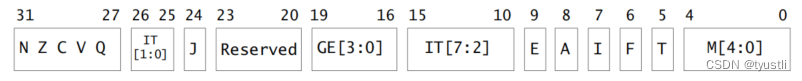

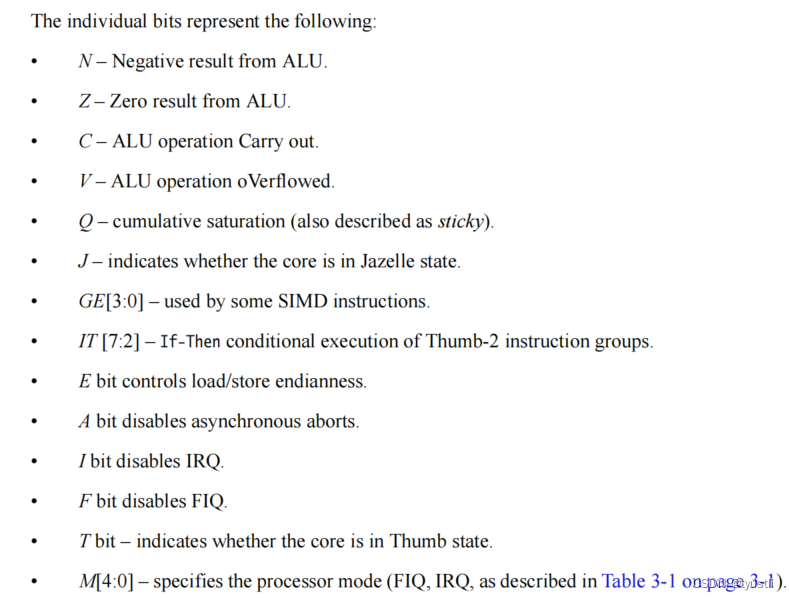

CPSR

Current Program Status Register 即 CPSR,当前程序状态寄存器,可以在任何处理器模式下被访问。它包含了条件标志位、中断禁止位,当前处理器模式标志以及其他的一些控制和状态位。

SPSR

除了 usr 和 sys 模式外,每一种处理器模式下都有一个专用的物理寄存器,称为 SPSR(备份程序状态寄存器)。当特定的异常中断发生时,这个寄存器用于存放当前程序状态寄存器的内容。在异常中断程序退出时,可以用 SPSR 中保存的值来恢复 CPSR。

由于用户模式和系统模式不是异常中断模式,所以他们没有 SPSR。当在用户模式或系统模式中访问 SPSR,将会产生不可预知的结果

SPSR

Usr 模式下有一个受限的 APSR(application program status register) 寄存器用来简单的代替 CPSR

应用程序必须使用APSR来访问CPSR中可以在非特权模式下更改的部分。可访问的位包括:N Z C V Q 和 GE[3:0]。也就是说在 usr 模式下只能访问这些位。

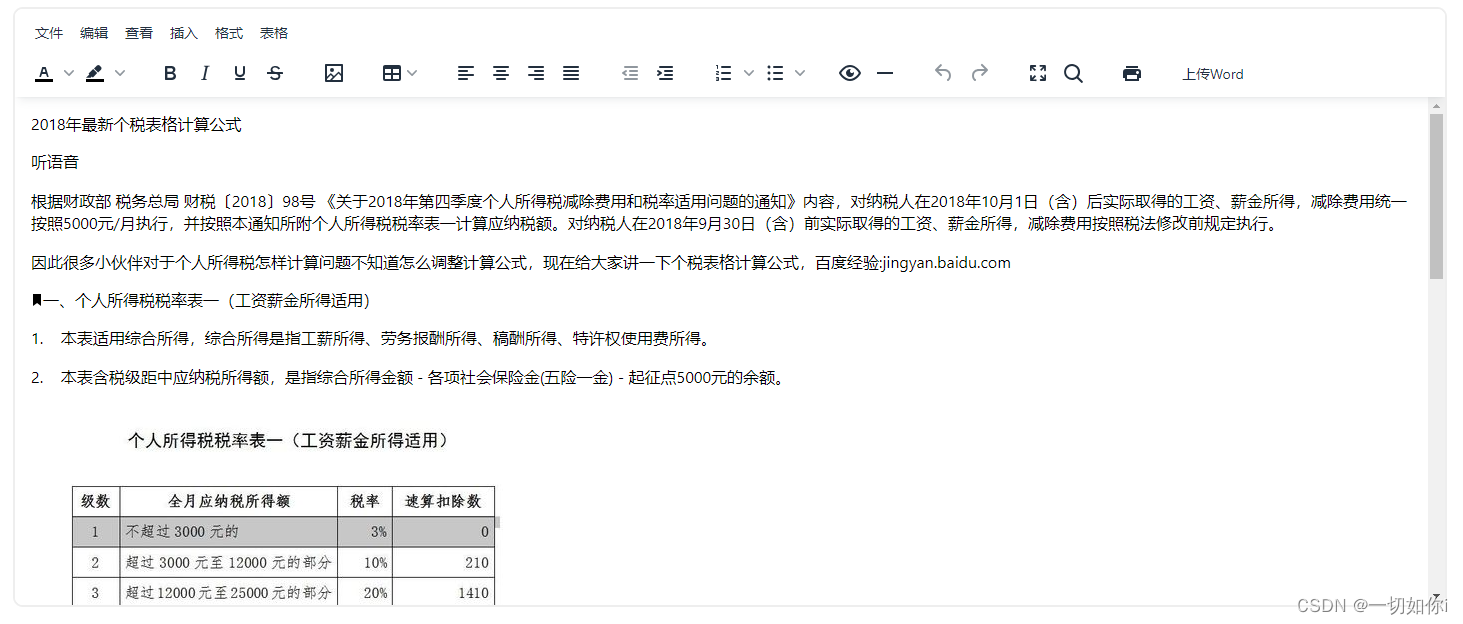

CPSR 各个位含义

需要注意的是,

-

User 模式下,不能操作 bit[4:0],即不能切换处理器模式

-

User 模式下,不能操作 A,I 和 F 位

-

N

ALU 计算单元结果是否为负数- N = 1 表示运算的结果为负数

- N = 0 表示运算的结果为正数

-

Z

ALU 计算单元的结果是否为 0- Z = 1 表示运算的结果为 0

- Z = 0 表示运算的结果不为 0

-

C

ALU 计算单元的结果是否有进位或借位- 运算器进行加法运算

进位自动置 1

否则为 0 - 运算器进行减法运算

借位自动置 0

否则为 1

- 运算器进行加法运算

-

V

ALU 运算单元计算结果是否溢出

对于加减运算指令,当操作数和运算结果为二进制的补码表示的带符号数时,V=1表示符号位溢出;通常其他指令不影响V位 -

IT[7:0]

- IT[7:5]:指示条件执行的条件码。这3个bit用于表示先前指令的条件码,决定是否执行下一条指令。

- IT[4:0]:指示条件执行的操作数量。这5个bit用于表示条件执行期间的操作数量。

-

J

用于指示当前处理器是否处于Java执行状态-

J = 0,表示处理器处于非Java执行状态。

-

J = 1,表示处理器处于Java执行状态。

Java状态位主要用于ARM架构中支持Java虚拟机(JVM)的处理器。当处理器处于Java执行状态时,它会根据Java虚拟机的需求进行相应的优化和处理。Java状态位的具体使用和影响会根据具体的处理

需要注意的是,Java状态位在现代ARM架构中已经不再被广泛使用,因为ARM处理器已经有更高效的方式来支持Java虚拟机。因此,在一些较新的ARM处理器中,J位可能没有具体的功能或被保留为未来的扩展使用

-

-

GE[3:0]

被一些 SIMD(single instruction multi data 单指令多数据) 指令使用- GE[3]:指示饱和标志的第4位。

- GE[2]:指示饱和标志的第3位。

- GE[1]:指示饱和标志的第2位。

- GE[0]:指示饱和标志的第1位。

饱和标志主要用于指示算术运算的结果是否饱和。在一些特定的 SIMD 指令中,当运算结果超过了指定的范围时,会将结果饱和到最大或最小的可表示值,并将相应的饱和标志设置为1。通过检查饱和标志,可以判断运算结果是否发生。

-

E

控制 load/store 的字节序- E = 1 大端模式

- E = 0 小端模式

-

A

禁止异步中止

User 模式下,不能操作 A- A = 1 禁止异步中止

- A = 0 允许异步中止

异步中止是一种处理器中断机制,用于处理由于内存访问错误或其他异常情况引起的中止。通过设置或清除bit8,可以控制处理器是否响应异步中止。

-

I

User 模式下,不能操作 I

禁止 IRQ 中断- I = 0 使能 IRQ 中断

- I = 1 禁止 IRQ 中断

-

F

User 模式下,不能操作 F

禁止 FIQ 中断- F = 0 使能 FIQ 中断

- F = 1 禁止 FIQ 中断

-

T

指示处理器是否处于 Thumb 状态- T = 0 表示 ARM 指令

- T = 1 表示 Thumb 指令

-

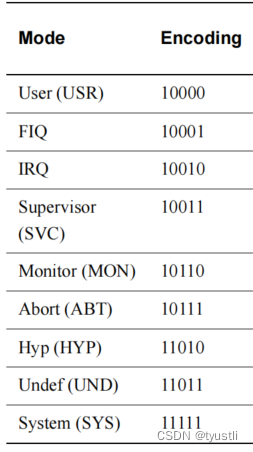

M[4:0]

User 模式下,不能操作 bit[4:0],即不能切换处理器模式

更常见的情况是,处理器因异常事件而自动改变模式。

处理器模式