晶体管

- N型MOS管

- P型MOS管

算术逻辑单元 ALU

晶体管–>门电路–>加法器–>ALU

既可以做逻辑运算、也可以做逻辑运算、成为计算机CPU中非常核心的组件。

指令

- 一条指令只完成一个基本操作的精简指令集 RISC 、它们的指令长度基本上是固定的。比如 ARM

- 一条指令可以完成一个复杂功能的复杂指令集 CISC、它们的指令长度基本上是不固定的 x86

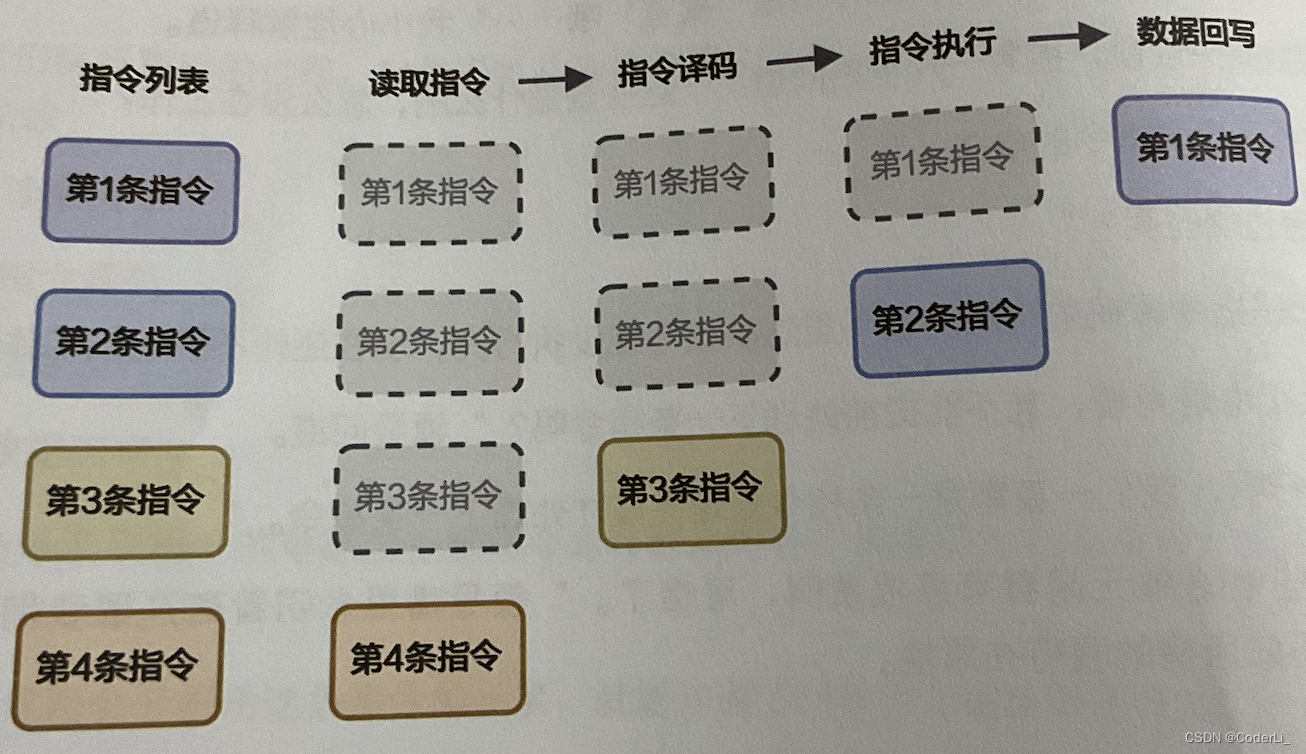

指令执行的过程

-

读取指令

读取指令的电路会根据指令寄存器从内存中读取要执行的指令、交给指令译码电路来处理

-

指令译码

译码电路会分析出这条指令的长度、就知道这个指令从哪里开始

-

指令执行

ALU 来执行这条指令所代表的功能

-

数据回写

将结果写入到对应的位置

指令流水线

指令流水线遇到的问题(冒险)

-

结构冒险

流水线出现硬件资源竞争

-

数据冒险

流水线中后面的指令需要等待前面指令完成数据的读写

-

控制冒险

流水线需要根据前面指令的执行结果来决定下一步去哪儿执行

遇到这些问题只能让流水线停顿下来等待、等待前面的指令完成、再继续工作

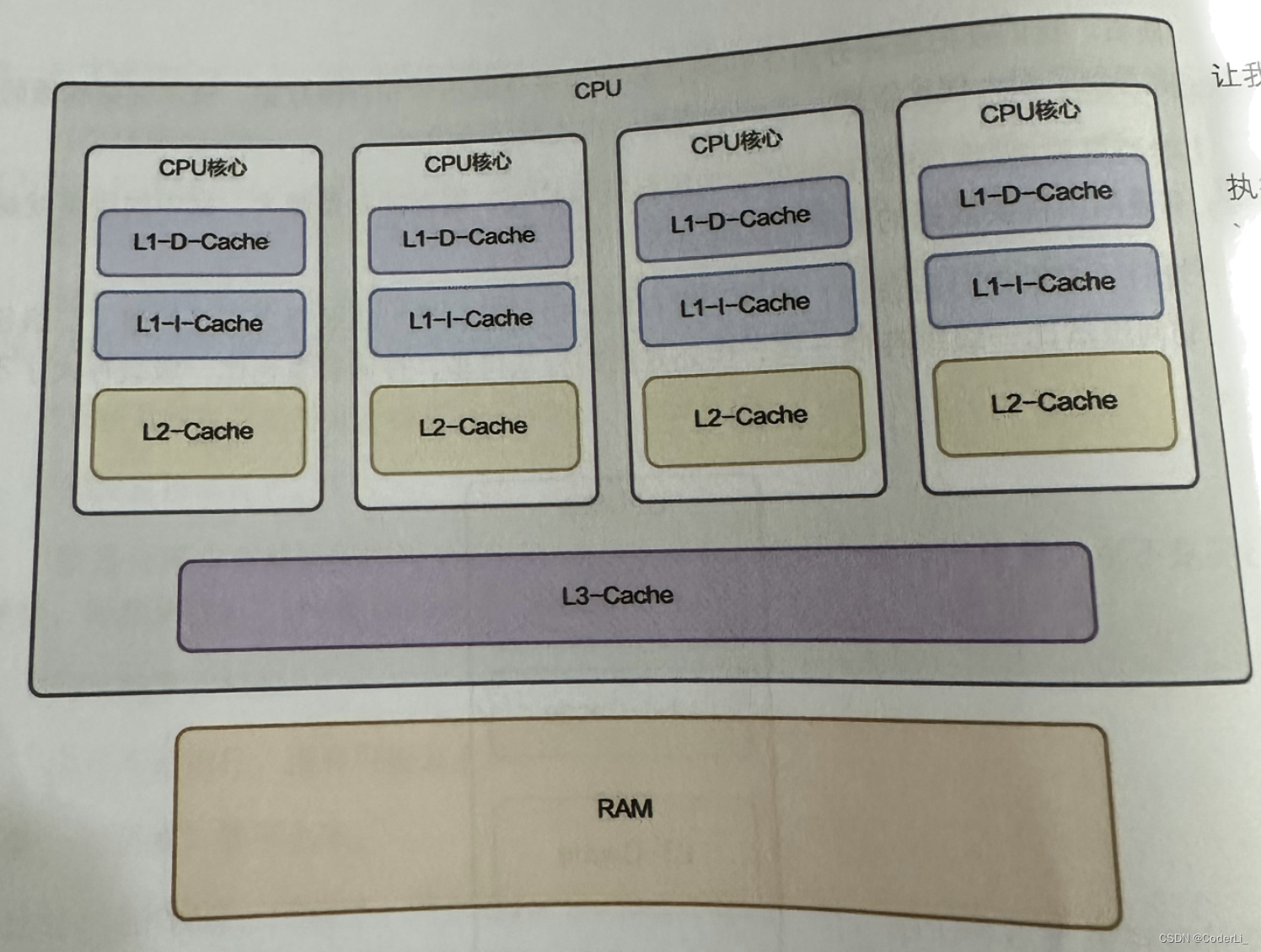

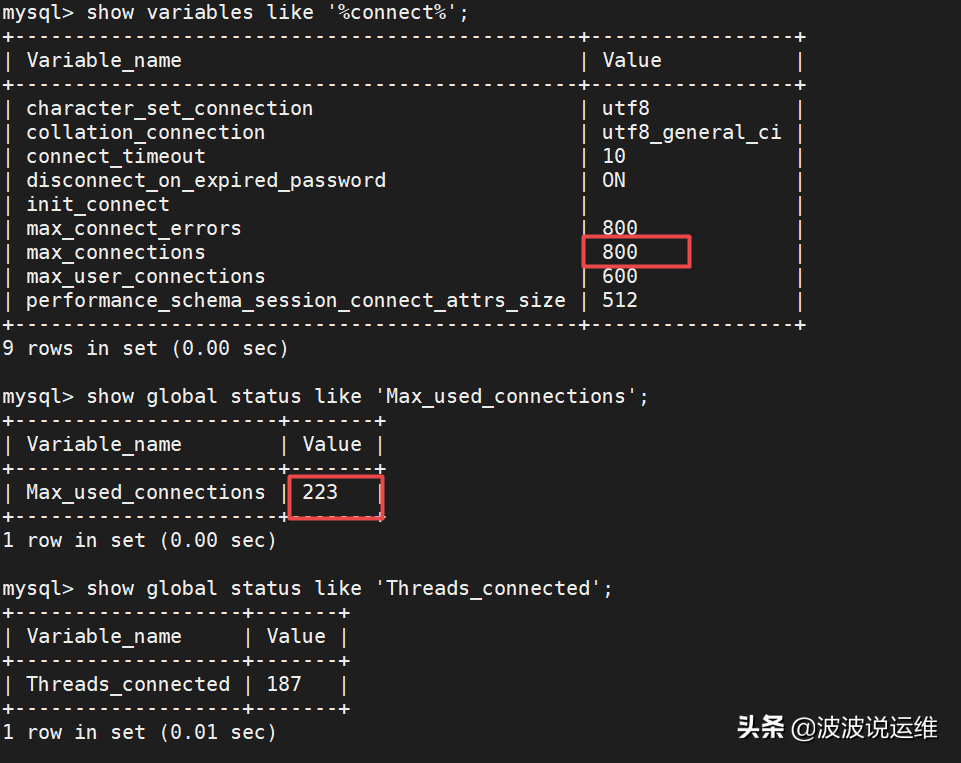

缓存

使用 SRAM(静态随机存储器)、耗用很多的晶体管、大小只有 64kb

缓存行一般为 64字节、每个缓存行有标志位:现在只有失效、脏数据两种状态

内存中读取的数据放在缓存的哪个位置上?

取模之后再用列表存储,如果列表的长度为2、则为二路组相连。如果为4则为死路组相连。

指令缓存和数据缓存

将指令和数据在缓存中分开存储、这样子能大大减少流水线执行的结构冒险

A 执行指令需要读取数据

B 读取指令

如果都在缓存中、如果缓存没有分类、那么A和B不能同时执行,如果分类了的话、分别走不同的线路同时获取

多核缓存不一致引发的问题

缓存一致性协议 MESI

各个 CPU 之间拉了一条新的专线、用于CPU 之间进行信息沟通、不同于CPU外部的总线系统、大家把它叫做片内总线

-

M modify 已修改

缓存行已经被修改、与内存的值不一样。

-

E exclude 独占

缓存行只存在当前 CPU 核心缓存中、而且和内存中数据一样

-

S share

缓存行存在于多个 CPU 核心缓存中、而且和内存中的内容一致

-

I invalid 无效

缓存行是无效丢

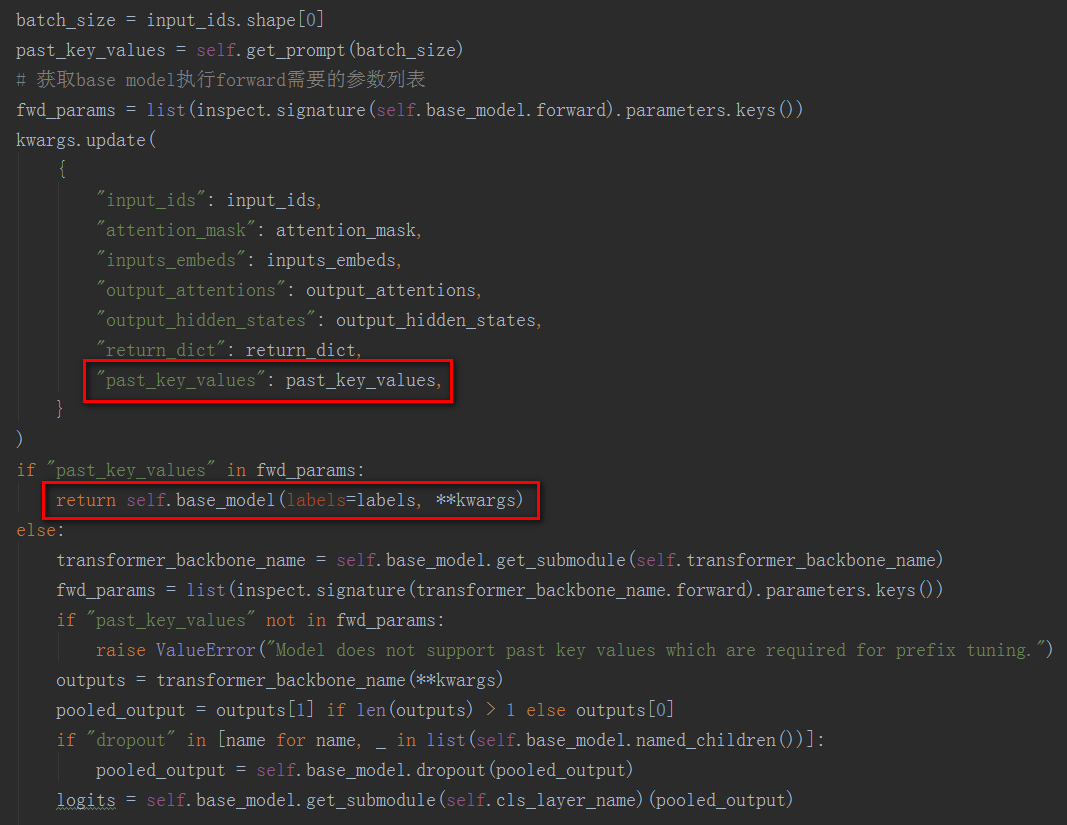

指令乱序执行

在指令经过译码之后、进入 ALU 执行之前、我没设置了一个缓冲区、指令会先到这里排队。

在这缓冲区中、会登记指令师傅有数据依赖、具体依赖什么数据、需要用到执行部件有哪些、当前是否繁忙、以及需要读写的寄存器是哪些等信息。这个缓冲区我们称它为保留站。随后指令调度单元就可以去这个缓冲区挑选没有依赖的指令来执行。

重排序缓冲区

指令在内部是乱序执行的、但不能把结果直接进行回写。所以得按照它们实际的顺序重新排序后再回写。所以在外面看来指令还是按顺序一条条执行的、但是内部真正执行的时候是打乱的、但这个不会影响程序的逻辑。

通过指令乱序执行、可以减少数据冒险带来的停顿了。

分支预测

针对指令流水线遇到的控制冒险、我们有相当大的概率预测正确后续执行的分支、不用再把流水线停顿下来。

预测错了怎么办?

错了就错了呗、大不了把已经进入流水线中还没处理完的指令中间结果全部清除、当没事发生过。

一条指令同时处理多个数据

并行处理

单条指令多数据流 SIMD single instruction multiple data

比如说对一个数据里面的元素都 + 1

超线程技术

一个核同时执行两个线程

每个 CPU 分成两套班子、各自维护一套寄存器、对外宣称我们有两个不同的物理核心、但实际上缓存和计算资源只有一套。

在执行指令的时候、充分利用等待时间去执行另一个线程的指令。这样子就不用担心指令以来的问题了。比如说内存读取缓慢、指令依赖等方面的原因、虽然有乱序执行、但是找到没有依赖的指令还是不那么容易。

还有就是如果遇到资源闲置的时候、可以同时执行两个线程的指令、比如一个是整数运算指令、一个是浮点数运算指令。

绝大多数能提升 20 -30 % 就很不错啦

CPU 如何管理内存的

没有操作系统的时候、程序执行直接使用真实内存地址、实地址模式。

虚拟内存、保护模式。

每个程序都可以使用 0x000 到 0xfff 总共 4GB 那么大范围的地址空间、当然不会真的分配那么多空间、物理内存总共也没有那么大。

而是按需分配、分配的单位是页、32 位的一页是4kb、分配管理的活是操作系统做的。CPU 只要做好地址翻译的工作就好了。

CR3 寄存器专门用来指向一个地址翻译查询字段。32位地址划分为3部分、前面两部分分别指向两级目录的条目、用来定位地址在物理内存的哪个页、最后一部分就是指向物理内存页面的偏移、这就是地址翻译的工作。

分页交换

随着程序越来越多、对内存的需求页越来越大、内存空间很快就要耗尽。

去硬盘空间中划分一块区域来、把在内存长时间没有用到的页面换到这块区域,然后做个标志、如果后面谁访问那个页面、CPU 就就先检查、如果有这个标志、就发送一个错误的中断信号给操作系统、去把那个页面换回来。

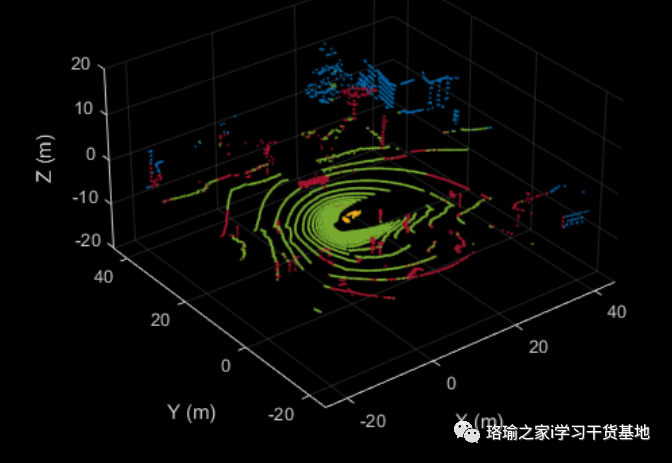

GPU 和 CPU 有啥区别

SIMT 单指令多线程技术 批量执行计算 GPU 的

SIMD 单指令多数据流 批量操作数据 CPU 的

https://book.douban.com/subject/36428782/

![[工业互联-17]:常见EtherCAT主站与实现方法](https://img-blog.csdnimg.cn/img_convert/290bef9205e738ed7950c39603fc5b61.webp?x-oss-process=image/format,png)