前段时间,有时间整理了一下关于+vcs+initreg+random 编译和仿真选项的心得,草草写了两篇笔记。自觉得对该选项已经掌握了,后来实际应用中再次触及到了该知识点,不想又卡壳了。今天,继续追加一篇,希望对大家能有所帮助!不正之处,请指正。

对于上述规则rule#2和 rule#3, 并没有什么可值得推敲的地方。今天我们着重看第一点,rule#1。

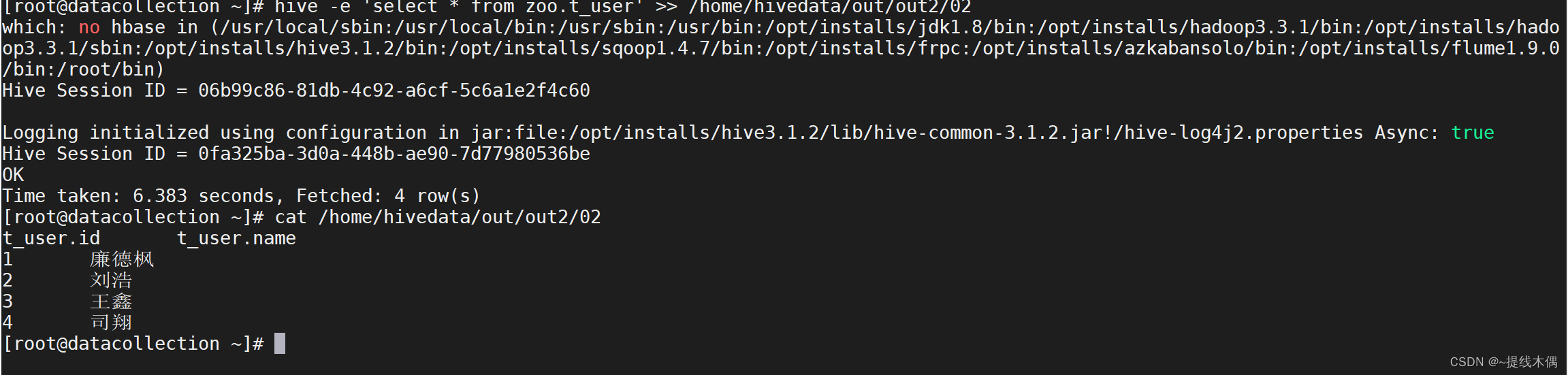

代码:

`timescale 1ps/1ps

module tb_top;

wire aa,bb,cc,dd;

reg clk;

reg rst_n;

wire [7:0] t_i, t_j, t_k, t_l_a, t_l_b, t_l_c;

wire [1:0] t_bit_a, t_bit_b;

wire [7:0] t_byte;

wire [63:0] t_time_value;

wire [127:0] t_r_time_value;

wire [3:0] data_out0;

wire [3:0] data_out1;

reg [3:0] data_in0;

reg [3:0] data_in1;

bit [1:0] bit_a, bit_b;

integer age, score;

int i, j, k;

byte addr;

real time_value;

realtime r_time_value;

logic [5:0] l_a, l_b, l_c;

assign cc = aa + bb ;

assign cc = aa+dd;

counter u_counter0(.clk(clk), .rst_n(rst_n), .data_out0(