1.FPGA的开发流程

Fpga代码的开发分为以下流程:

- 设计定义(处于架构阶段,对需求进行定义,分析,模块划分)

- 设计输入(verilog RTL代码输入、原理图)

- 功能仿真

- 分析和综合(由源文件综合编译run synthesis与生成特定设计的网表,逻辑综合实质上是设计流程的一个阶段,在这个阶段中将较高级的抽象层次的描述自动的转换成较低层次的描述)

- 布局布线(run implementation实现编译)

- 时序仿真(一般不需要)

- 约束输入(这个是xdc约束文件,时序、引脚约束)

- 配置(bitstream generator烧写FPGA,可以在线bit流,可以bin、mcs固化)

- 板级调试(使用ila等工具进行调试)

- 系统验证与产品发布

上述过程中包含了编译的三个流程,分别是综合编译run synthesis---run implementation实现编译---生成bit位文件

2.以流水灯为例熟悉vivado开发流程

(1)打开vivado创建新工程,路径不要有中文和特殊符号。

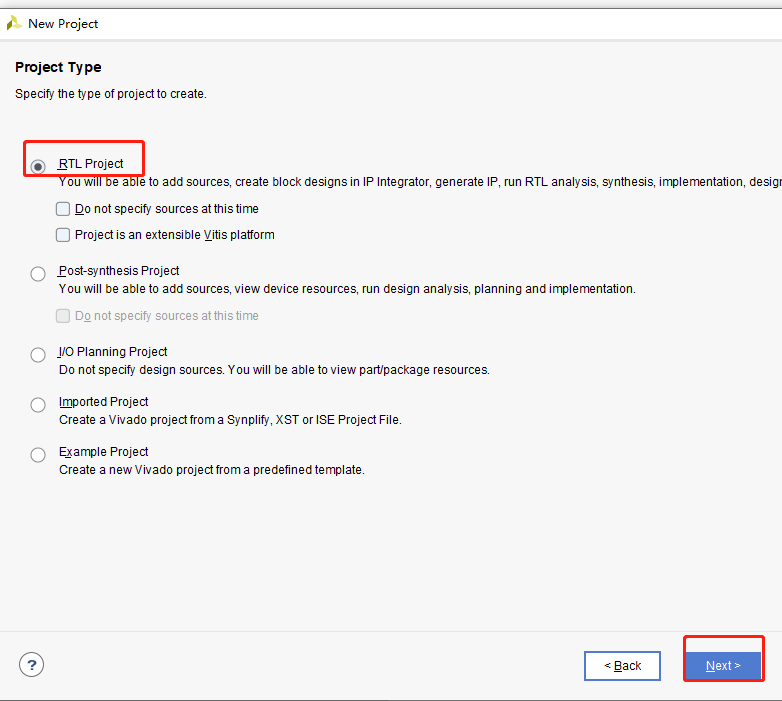

(2)选择RTL project点击下一步

(3)可以在此处添加源文件,此处选择不添加

(4)选择不在此处添加约束,直接next.

(5)选择所用芯片型号

(6)选择finish完成工程创建

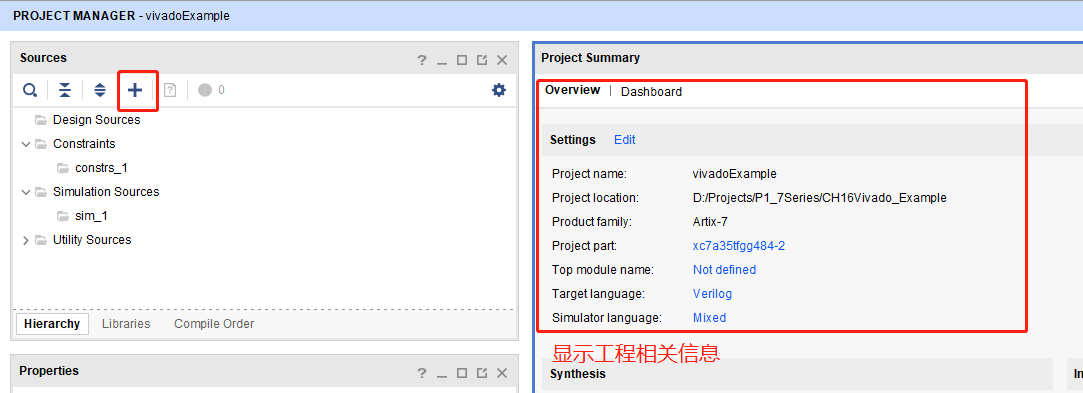

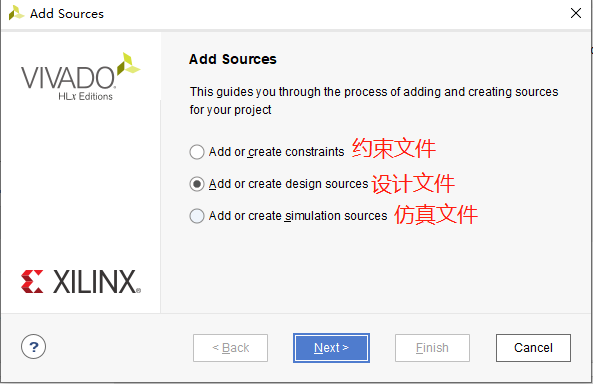

(7)Project summary是工程信息的简要,单击“+”,选择设计文件,next。

(8) 选择新建并命名单击OK,选择finish.

(9) 输入RTL,保存.v文件

module Flowled(

input clk_i, //输入系统时钟 50MHz

output reg [2:0]led

);

reg [27:0]clk_cnt=0;

reg [1:0]led_cnt=0;

wire switch;

assign switch = clk_cnt==27'd50_000_000;

always @(posedge clk_i) begin

if(clk_cnt==27'd50_000_000)begin //1s

clk_cnt <= 0;

led_cnt <= led_cnt +1;

end else

clk_cnt <= clk_cnt + 1;

end

always @(*) begin

case (led_cnt)

0:led = 3'b000;

1:led = 3'b001;

2:led = 3'b010;

3:led = 3'b100;

default: ;

endcase

end

endmodule

(10)依次点击综合和布线

(11)布线成功后,打开“Open Implemented Design”,打开window中的I/O ports,此处添加所有的约束,并另存为xdc文件,点击generate bitstream

(12)连接下载器与电源,打开电源,单击open hardware manager ,随后点击open target—>Auto connect

(13)点击program device下载程序,在板卡上看到对应的LED在闪烁

3.FPGA文件目录

- .cache:vivado软件运行缓存

- .hw:波形文件

- .ip_user_files:用户关于IP的文件

- .runs: 编译与综合的结果,其中\impl-1文件夹中存放的是编译生成的可执行文件,.bin 是可以固化的文件,.bit是烧写的bit流文件。

- .sclk:SDK环境代码,一般是ZYNQ设计中关于PS端的代码

- .sim:仿真结果文件

- .srcs:源码,仿真文件,约束文件

- .tmp:自制IP核时的临时设计工程文件夹

- .xpr: ivado的工程文件

4.代码固化

代码固化的原理是将fpga的程序烧录到flash中,flash兼具了rom和ram的有点,即速度快并且掉电不失数据。Vivado的固化文件有两种,一种是mcs文件,一种是bin文件。Bin文件是选择tools-->setting-->bitsream-->勾选 -file_bin,然后正常的生成比特流文件,会在bit文件相同的位置生成bin文件,然后与bit文件的烧写方式一样,只不过选择bin文件即可实现代码的固化。对于mcs有两种方式生成,一种是使用命令窗口tcl输入相应的指令生成mcs,另外一种是tools中选则相应按钮配置生成mcs文件,其中具体的操作过程参看正点原子开发指南。过程较为繁琐,推荐使用bin文件进行固化。现有板卡上的Flash芯片型号MT25QL128ABA1ESE-0SIT,存储容量128 4bitSPIx4

①添加原语(约束文件中)

set_property CFGBVS VCCO [current_design]

set_property CONFIG_VOLTAGE 3.3 [current_design]

set_property BITSTREAM.GENERAL.COMPRESS true [current_design]

set_property BITSTREAM.CONFIG.CONFIGRATE 50 [current_design]

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]

set_property BITSTREAM.CONFIG.SPI_FALL_EDGE Yes [current_design]

②生成MCS和prm文件

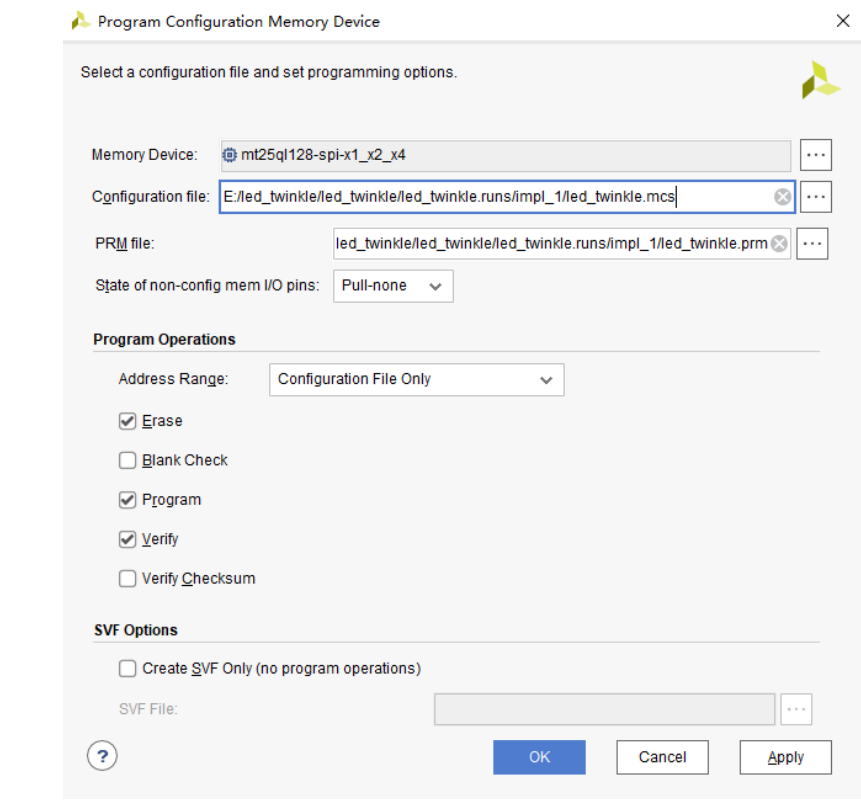

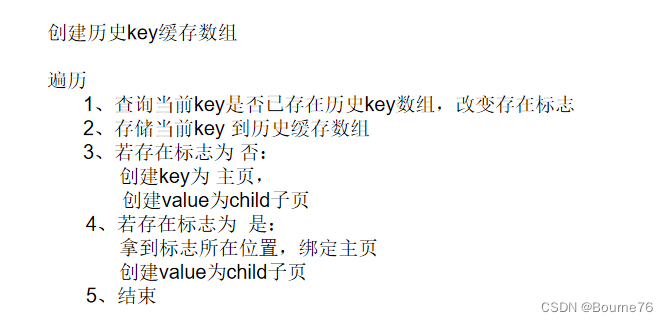

从图中我们可以看到一些配置选项,在此仅对我们需要用到的一些配置做简要介绍:

- Format:指的生成文件的格式,这里我们选择生成 MCS 文件。

- Custom Memory Size(MB):指的是所用flash的容量大小,这里选128(根据flash手册决定)。

- Filename:这里编辑生成的mcs文件名称,右边的三个点按钮是选择mcs文件保存路径。

- Interface:指的是所用flash的通信方式,这里我们选SPIx4(4bit通信flash,根据flash 手册决定)。

- Load bitstream files:这个选项勾上,然后添加你要生成mcs文件的原文件(bit 流文件)。

- Write checksum:写校验。

- Disable bit swapping:禁止位交换。

- Overwrite:覆盖原文件。

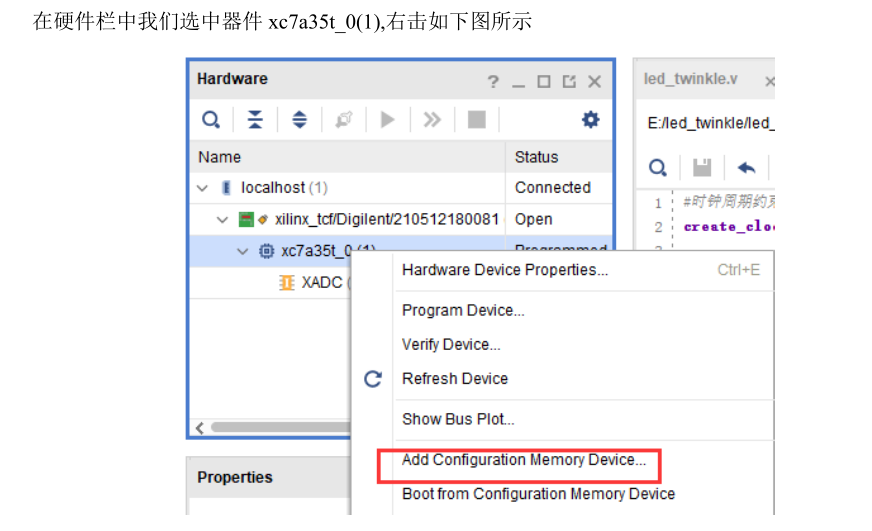

③烧写操作

右击选择program flash器件,按照如下图操作(图中mcs文件不对应)